طراحی یک بلوک دیاگرام

تراشه Xilinx Zynq به کاربران اجازه میدهد تا بلوکهای منطقی سفارشی خود را با سیستم پردازشگر نهفته ترکیب کنند. ما در ادامه یک فایل سورس به پروژه اضافه میکنیم که نشان دهنده بخش پردازشگر نهفته طراحی ما در قالب بلوک دیاگرام خواهد بود. طراحی در بلوک دیاگرام (Block Design) یکی از ویژگیهای Xilinx Vivado است و ما از آن در این درس استفاده خواهیم کردیم.

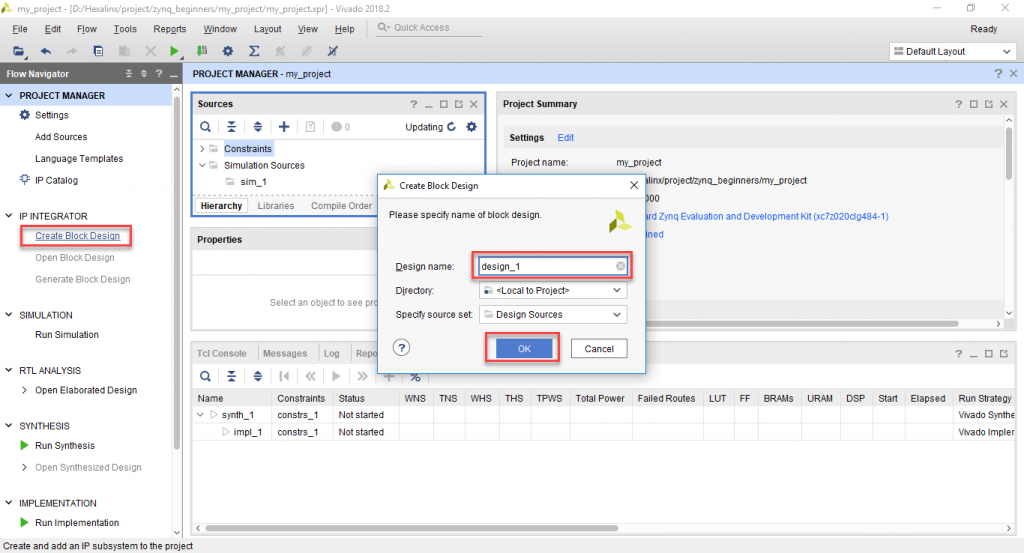

۱- در صفحه Flow Navigator در سمت چپ صفحه نمایش، بر روی آیکون Create Block Design کلیک کنید.

۲- در پنجرهای که برای شما باز میشود، نام پیشفرض بلوک دیاگرام را تغییر نداده و بر روی OK کلیک کنید.

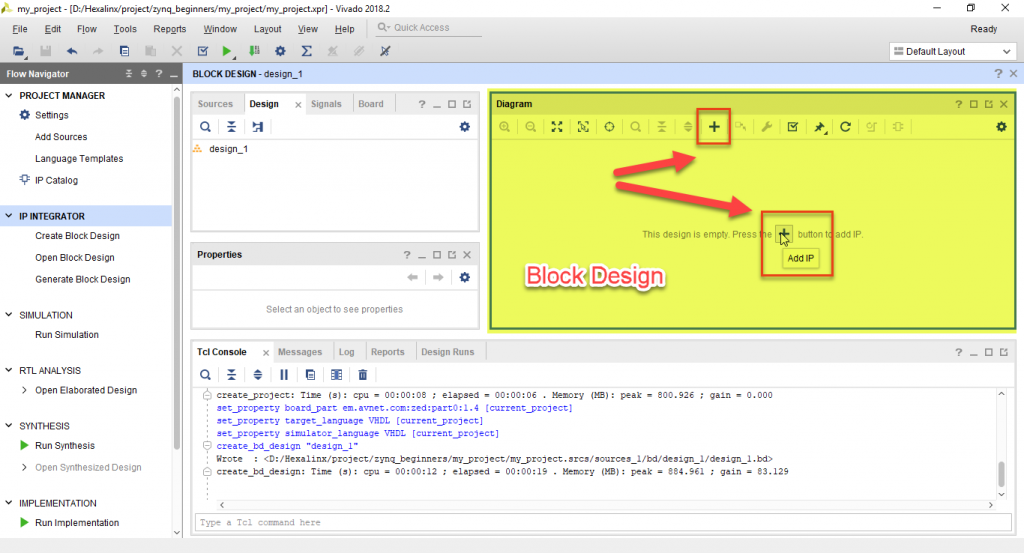

۳- پس از چند ثانیه، صفحهای در سمت راست، درون نمای Block Design (که مرزهای آن با نوار آبی رنگ در قسمت فوقانی صفحه مشخص شده است) باز میشود و یک صفحه خالی بلوک دیاگرام به نمایش در خواهد آمد.

حالا نوبت به تنظیم بخش پردازشگر سخت افزاری درون تراشه Zynq میرسد.

۴- در مرکز صفحه و یا در نوار ابزار در بخش بالایی صفحه خالی بلوک دیاگرام بر روی علامت + که همان گزینه Add IP است، کلیک کنید.

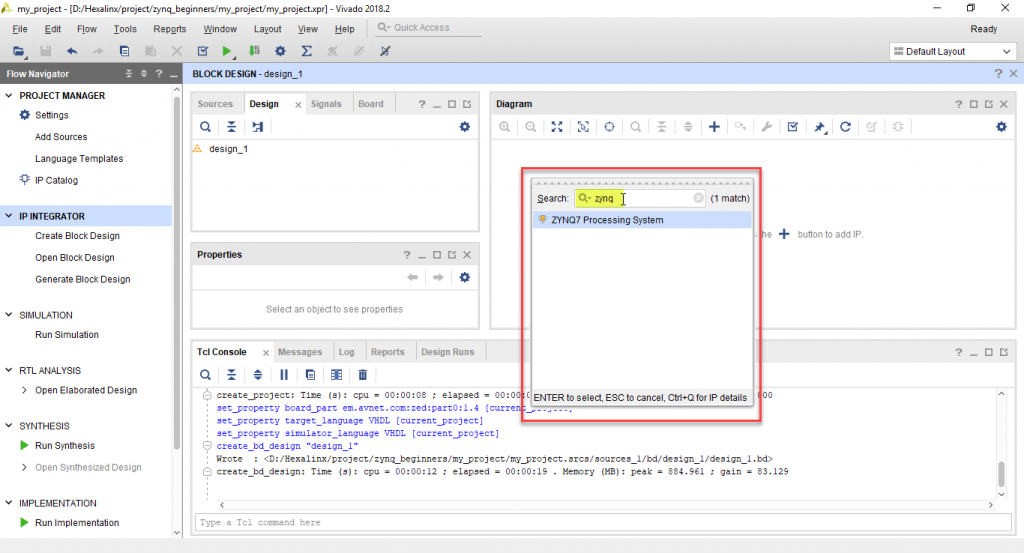

۵- از لیست موجود گزینه Zynq7 Processing System را انتخاب کنید. شما میتوانید، این کار را هم از طریق اسکرول کردن در لیست و هم با فشردن کلیدهای حروف اول مربوط به آن در فیلد بالای جعبه جستجو انجام دهید. برای اضافه کردن IP به بلوک دیاگرام بر روی IP داخل لیست دوبار کلیک کنید، یا آن را به وسیله ماوس به روی بلوک دیاگرام درگ کنید.

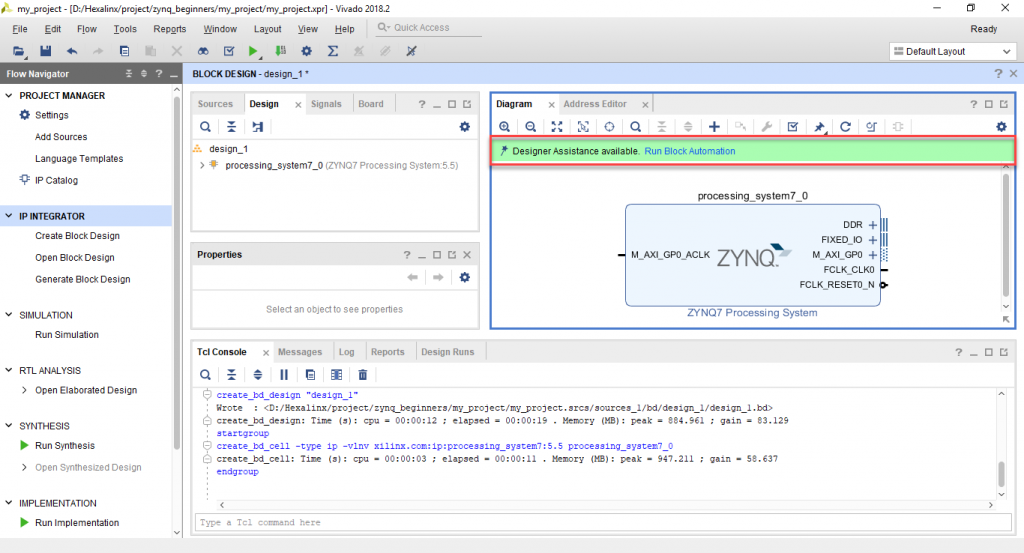

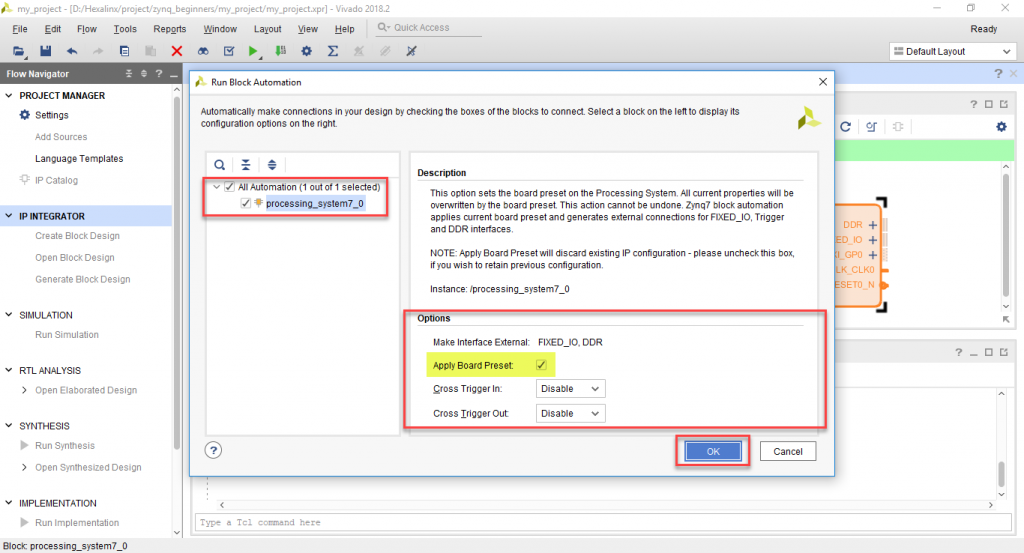

۶- بلافاصله یک نوار سبز رنگ به نام «دستیار طراح» در بالای صفحه ظاهر میشود تا در ادامه طراحی شما را همراهی نماید. (این نوار سبز رنگ به معنای واقعی کلمه یک دستیار طراح یا Designer Assistance است و بیش از آنکه تصور کنید در فرایند طراحی به شما کمک میکند) در این نوار استفاده از قابلیتی به نام Run Block Automation به شما پیشنهاد میشود که هدف آن کمک به اجرای اتوماتیک تنظیمات است. در واقع Vivado متوجه شده که یک بلوک تنظیم نشده داخل دیاگرام به وجود آمده و به کاربر اجازه اتصال پینهای مورد نیاز را بر روی این بلوک ارائه میکند. بر روی لینک Run Block Automation در نوار دستیار طراح کلیک نموده و سپس در سمت چپ پنجرهای که باز میشود، بر روی نام نمونهای که برای بلوک انتخابی شما در دیاگرام اضافه شده است، کلیک نمایید این نام احتمالاً processing_system7_0 خواهد بود. در سمت راست گزینه Apply Board Preset را تیک خورده رها کنید، این تیک باعث میشود تنظیمات مورد نیاز ZedBoard اعمال شوند، حالا روی OK کلیک کنید. سایر گزینهها را بدون تغییر رها کنید.

۷- توجه کنید که اتصالات ورودی خروجیهای ثابت و DDR به طور خودکار ایجاد شدهاند. ابزارهای Vivado بوردی را که برای پروژه انتخاب شده است، شناسایی کردهاند و اصطلاحا «آگاه به بورد» هستند، در نتیجه تغییراتی را بر روی تنظیمات داخلی بلوک سیستم پردازشی Zynq7 Processing System اعمال کردهاند. مشاهده میکنید که تعدادی اتصال اضافی نیز در بلوک ظاهر شده است که شامل کلاکها، ریستها، خروجیهای تایمر و باس اینترفیسهایی که امکان اتصال بلوکهای AXI IP بیشتری را فراهم میکنند (منظور از بلوکهای AXI IP هر پریفرال نرم افزاری قابل فراخوانی در بطن بخش قابل پیکره بندی تراشه Zynq است.)

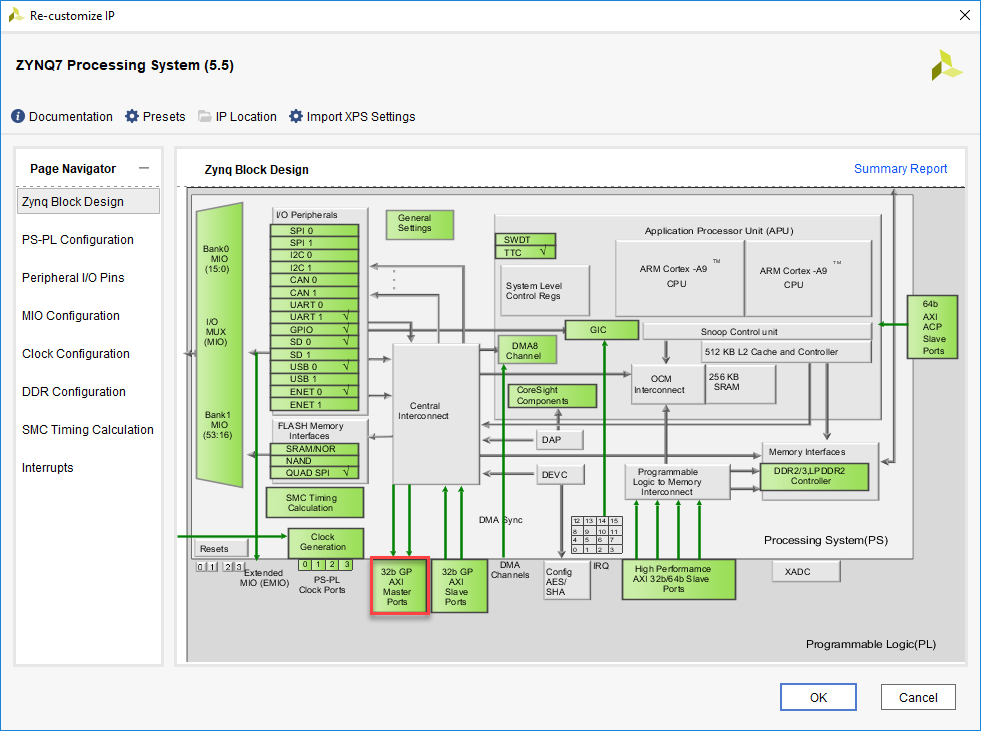

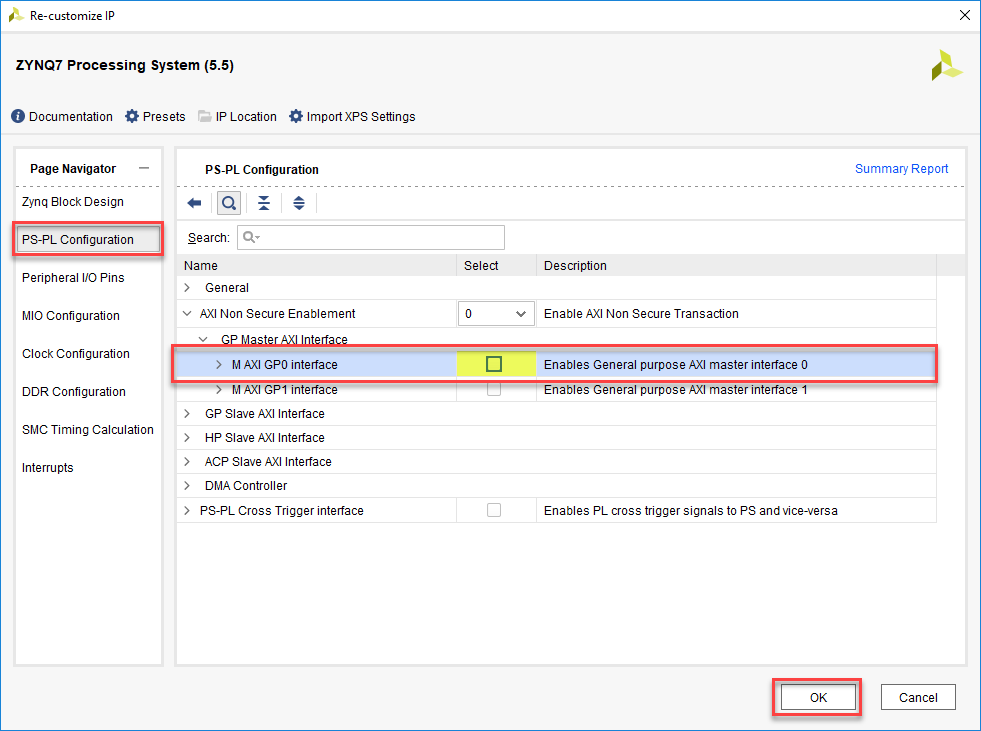

۸- حالا بر روی بلوک Zynq7 Processing System دوبار کلیک کنید تا پنجره سفارشی سازی آن باز شود. در اینجا میتوانید تغییراتی را در بخش پردازشی تراشه Zynq اعمال کنید، و همانطور که مشاهده میکنید تنظیمات متعددی در آن وجود دارد. ما سعی خواهیم کرد در ابتدا طراحی را بسیار ساده نگاه داریم، بنابراین باس اینترفیسهای AXI را که به بخش قابل پیکره بندی متصل میشوند، غیرفعال خواهیم کرد.

۹- دیاگرام تراشه Zynq که در این پنجره نشان داده شده، کاملاً تعاملی است. برای اعمال تنظیمات میتوانید بر روی هر چیزی که به رنگ سبز روشن درآمده باشد، کلیک کنید. بر روی بلوک 32b GP AXI Master Ports در پایین دیاگرام کلیک نمایید. تیک مربوط به گزینه M AXI GP0 interface را بردارید تا پورت مربوط به آن غیرفعال شود، حالا بر روی OK کلیک نمایید. پنجره سفارشیسازی بسته خواهد شد و شما به ویرایشگر بلوک دیاگرام باز میگردید. توجه کنید که پورتهای AXI از بلوک Zynq7 Processing System حذف شدهاند، و تنها خروجیهای کلاک، ریست و تایمر باقی مانده است. (توجه: میتوانستیم این خروجیها را نیز در تنظیمات سفارشی سازی غیرفعال کنیم، اما ما در طراحی خود به قطع اتصال آنها بسنده میکنیم.)

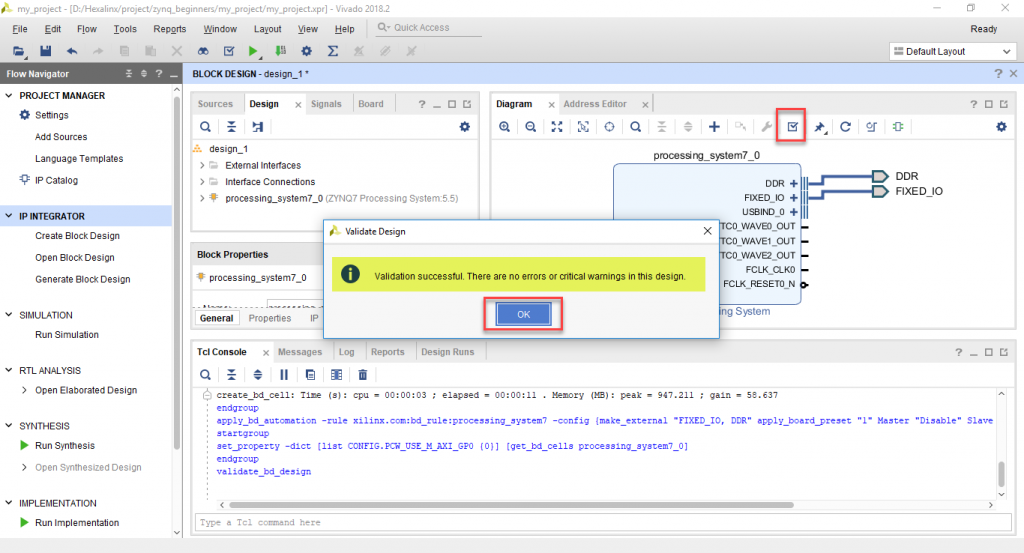

۱۰- تنظیمات بخش پردازشی طرح ما در اینجا به پایان میرسد. بر روی آیکون Validate Design که در نوار ابزار بالای بلوک دیاگرام قرار دارد کلیک کنید تا طراحی برای خطاهای احتمالی بررسی شود. باید در انتهای این پروسه پیغام Validation Successful نشان داده شود.

۱۱- با انتخاب گزینه File > Save Block Design از منوها، طراحی بلوک خود را ذخیره نمایید.

۱۲- در مرکز صفحه بر روی زبانه Sources و سپس نمای Design Hierarchy در پایین، که سلسله مراتب طراحی را نشان میدهد، کلیک نمایید. حالا شما سورس فایل طراحی بلوک خود را در پوشه Design Sources خواهید دید. بر روی نام سورس فایلی که ایجاد کردهاید، کلیک کنید (آیکون زرد رنگ و پسوند bd.) تا انتخاب شود. این ماژول حاوی کلیه تنظیماتی است که شما در ویرایشگر بلوک دیاگرام اعمال نمودهاید، و میتوانید در هر زمان با دوبار کلیک بر روی این سورس به آن بازگردید.

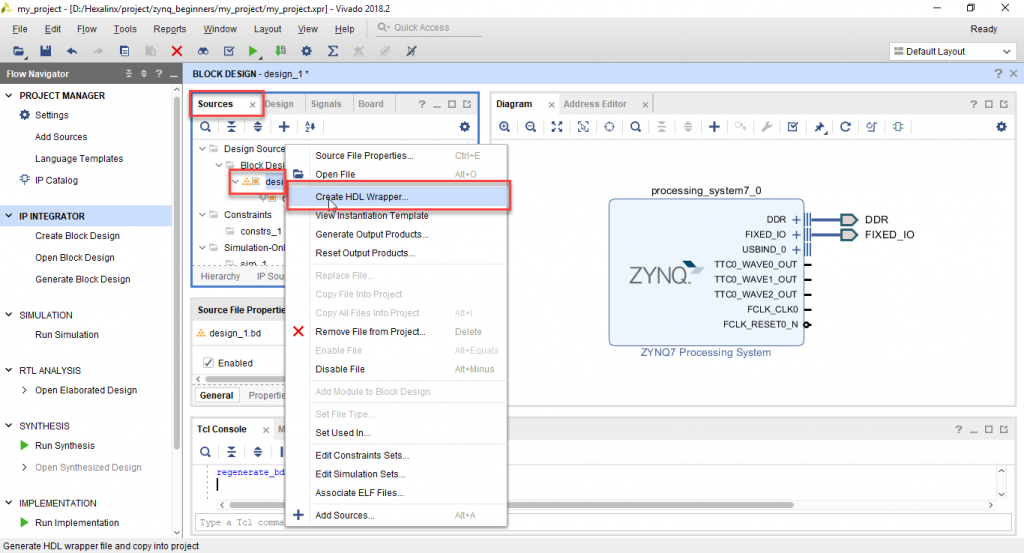

اکنون باید یک فایل تاپ ماژول wrapper به زبان VHDL/Verilog ایجاد کنید تا طراحی بلوک ما را در بر بگیرد. این سورس سطح بالا عموماً باید توسط طراح به طور سفارشی ایجاد شود، اما میتوان از ابزارهای Vivado نیز به عنوان یک میانبر برای انجام این کار استفاده نمود.

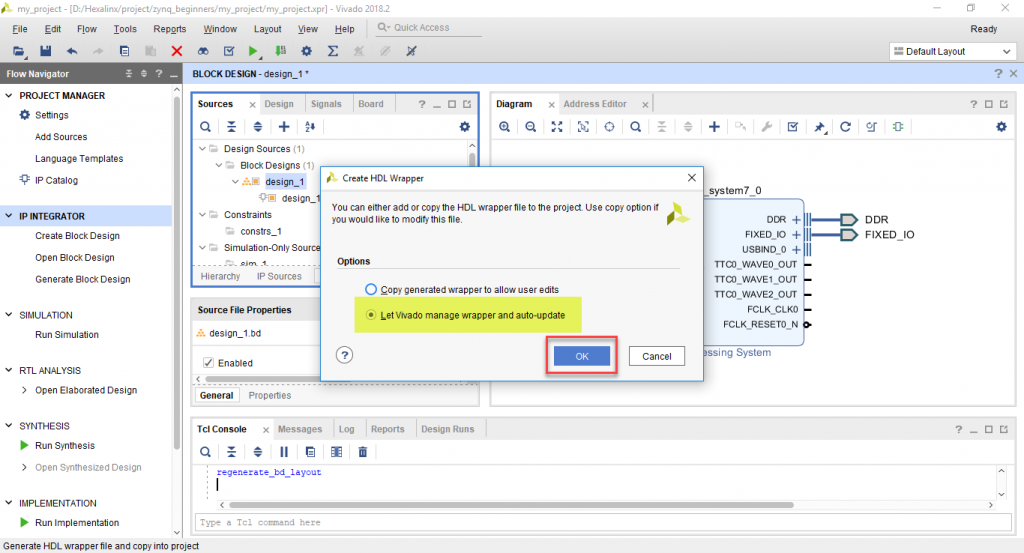

۱۳- بر روی فایل سورس طراحی بلوک، راست کلیک کنید و گزینه Create HDL Wrapper را از منویی که باز میشود انتخاب و سپس گزینه Let Vivado manage wrapper and auto-update را انتخاب نمایید، بر روی OK کلیک کنید. ابزارهای Vivado به طور خودکار یک فایل VHDL یا Verilog ایجاد خواهند نمود که نام آن براساس نام سورس طراحی بلوک شما به علاوه یک پسوند”_wrapper” تعیین میشود. در صورت تمایل میتوانید با دوبار کلیک کردن بر روی این فایل سطح بالا در سمت راست صفحه، محتوای آن را مشاهده و بررسی کنید. این فایل کمکی به عنوان فایل تاپ ماژول HDL به طراحی ما اضافه میشود.