ایجاد اولین پروژه

با انتخاب ZedBoard یک پروژه جدید در Vivado ایجاد کنید.

۱- از منوی Start گزینه Xilinx Design Tools > Vivado 2018.2 را انتخاب کنید.

میتوانید از نسخههای دیگر ابزار Vivado نیز استفاده کنید، اما توجه داشته باشید که صفحههای نشان داده شده در این دوره ممکن است متفاوت باشند.

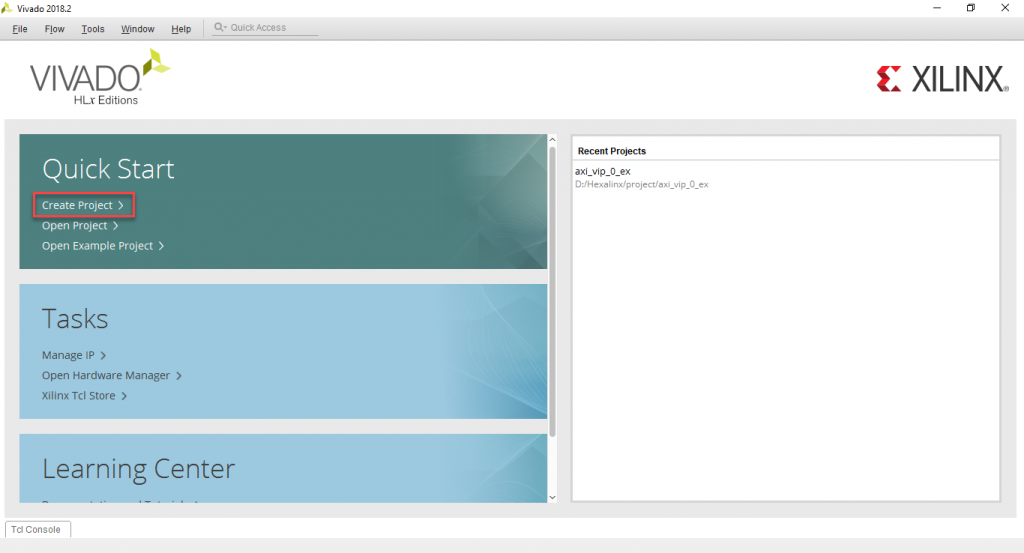

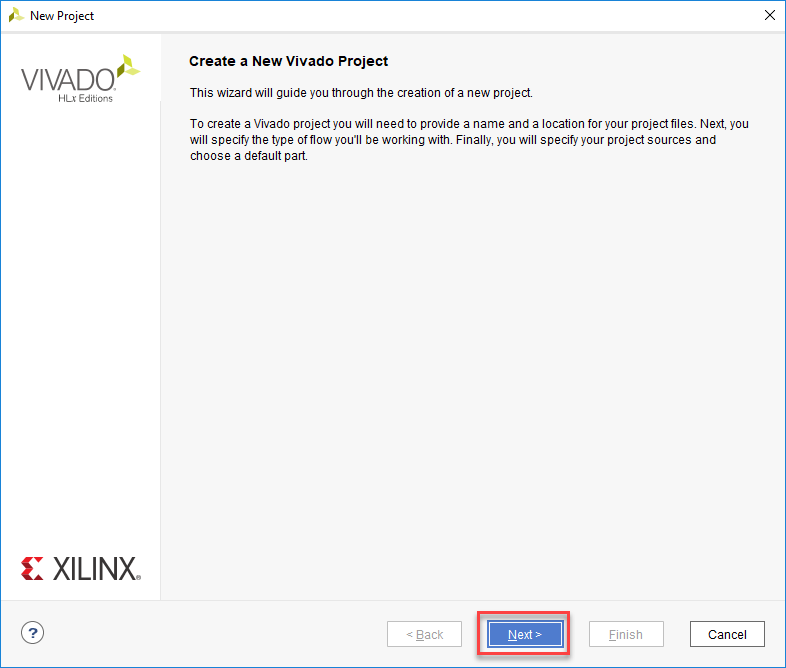

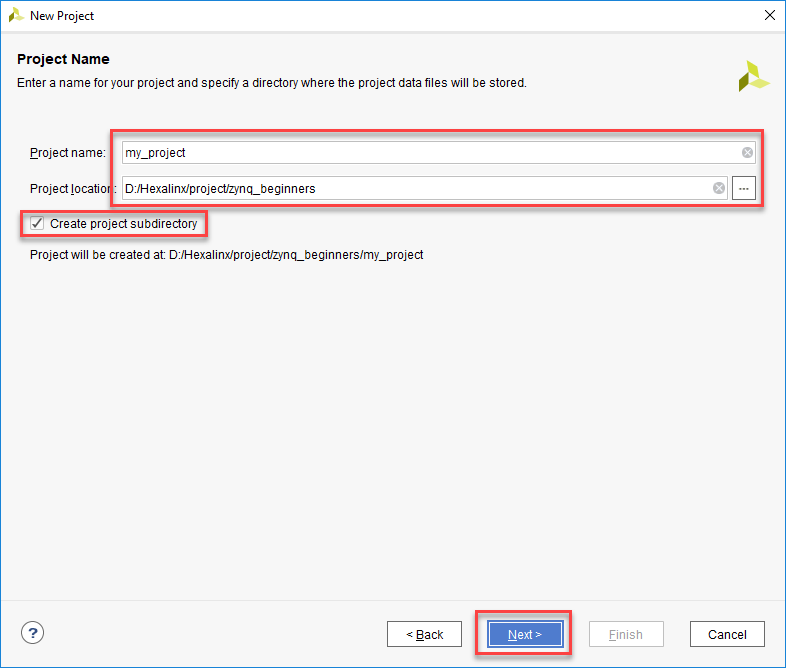

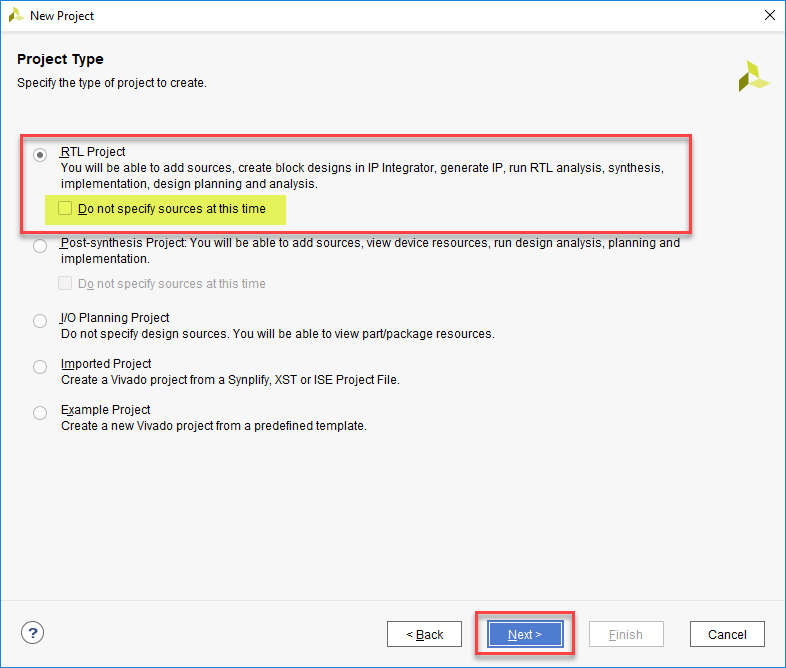

۲- در صفحه خوشامدگویی روی گزینه Create Project کلیک کنید تا ویزارد ساخت پروژه روی صفحه ظاهر شود. روی Next کلیک کنید و نام پروژه دلخواه خود را وارد کرده و مکانی مناسب برای ذخیره فایلهای پروژه بر روی کامپیوتر خود انتخاب نمایید. گزینه Create project subdirectory را به صورت تیک خورده رها کنید و روی کلید Next کلیک کنید. در صفحه بعدی گزینه RTL Project را از لیست انواع پروژهها انتخاب و مجدداً روی کلید Next کلیک کنید. دقت کنید که تیک گزینه Do not specify source at this time غیر فعال باشد.

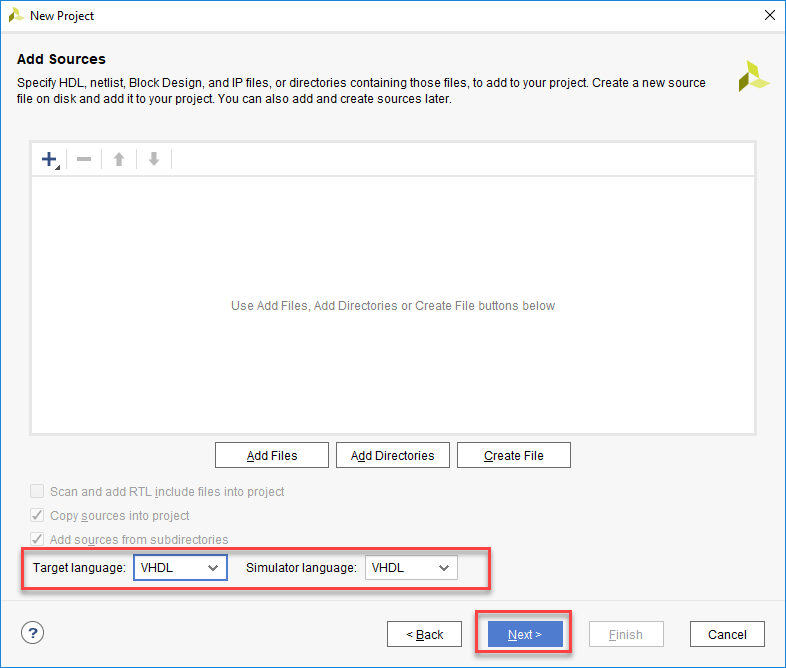

۳- گزینه VHDL را به عنوان زبان هدف از لیست کشویی Target language و Simulator language انتخاب کنید. اگر به جای VHDL ترجیح میدهید از Verilog استفاده کنید، میتوانید آن را در این صفحه انتخاب نمایید اما در ادامه این آموزش میبایست با مهارتهای خودتان به تغییر آن بپردازید. چند بار بر روی کلید Next کلیک کنید تا صفحه Default Part را مشاهده کنید.

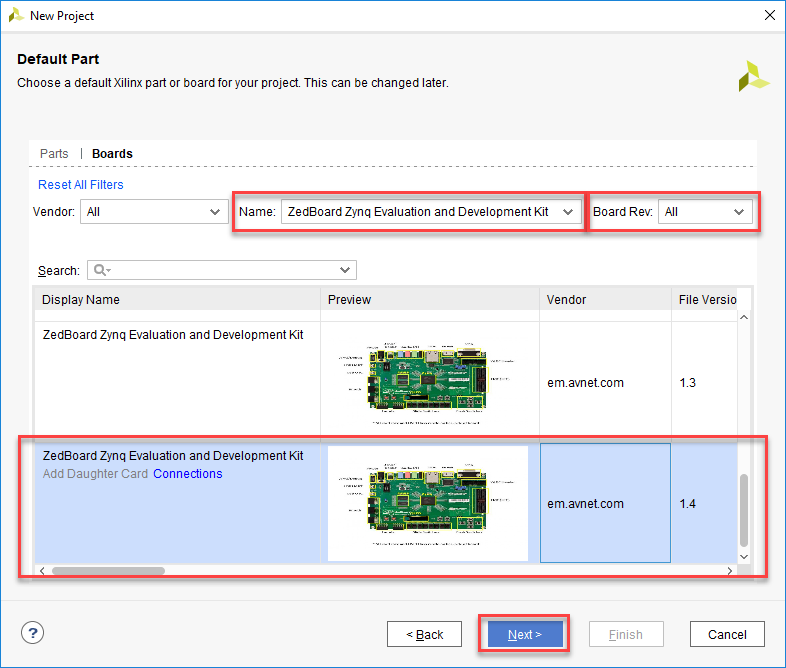

۴- در بالای صفحه روی گزینه Boards کلیک کنید. از فیلتر کشویی Name گزینه ZedBoard را انتخاب نمایید. از فیلتر کشویی Board Rev گزینه All را انتخاب نمایید.

۵- با مراجعه به نسخه درج شده روی برچسب بارکدی که روی بورد درج شده است، از نسخه ZedBoard خود مطلع شوید.

۶- ورژن صحیح ZedBoard Zynq Evaluation and Development Kit را از میان لیست بوردهای معرفی شده انتخاب نمایید. ابتدا بر روی Next و سپس روی Finish کلیک نمایید.

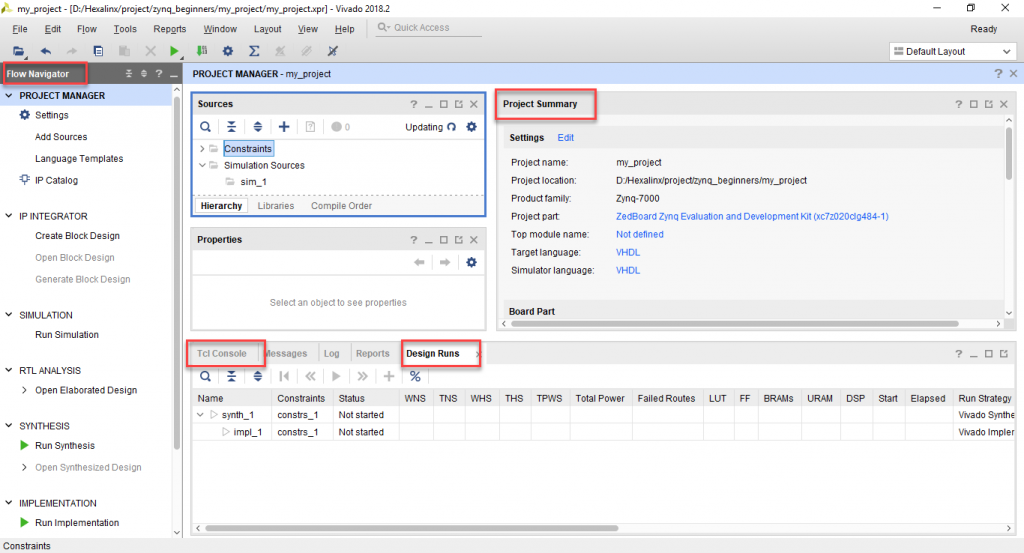

حالا یک صفحه خالی پروژه Vivado پیش روی شما است. برای استفاده بهتر از این ابزار، پنجره Vivado را بزرگ کنید.

۷- در سمت چپ صفحه نمایش، صفحه Flow Navigator را مشاهده خواهید نمود. از طریق این صفحه میتوانید جریان طراحی را کنترل نمایید. با استفاده از این صفحه شما میتوانید عملیات سنتز، پیاده سازی و ایجاد فایل بیت نهایی را مدیریت کنید.

۸- در میانه صفحه نزدیک به بالا، صفحه Sources را مشاهده میکنید. در اینجا سورس فایلهایی را که برای طراحی، به پروژه خود اضافه خواهید کرد، میبینید. در حال حاضر هیچ سورس فایلی برای پروژه تعریف نشده است، در نتیجه لیست ما فعلاً خالی است. همچنین فهرست قیود “Constraints” طراحی پروژه، که در این صفحه قرار دارد، نیز فعلاً خالی میباشد. از وجود زیر پوشه constrs_1 گیج نشوید، این شاخه نشان میدهد که شما دستهای پیش فرض برای قیود در پروژه دارید، ولی در حال حاضر فایلی در آن ثبت نشده است. همینطور زیر پوشه دیگری به نام sim_1 وجود دارد که این پوشه فایلهای شبیه سازی را در خودش جای میدهد. این پوشه هم خالی است.

۹- در سمت راست، صفحه خلاصه پروژه Project Summary را مشاهده خواهید نمود. در اینجا تنظیمات و آمار مرتبط با پروژه خود را ملاحظه میکنید، از جمله: اندازه و بزرگی پروژه، حجم منابعی که بر روی تراشه Zynq مصرف کردهاید، و خلاصهای از فایلهای گزارش که توسط ابزار تولید شده است. در حال حاضر اطلاعات بسیار کمی در این صفحه وجود دارد، زیرا ما هنوز کاری انجام ندادهایم.

۱۰- در پایین صفحه مجموعهای از زبانههای مختلف شامل گزارشات، پیغامهای خطا، اخطارها، پیامها و سابقه وقایع قرار دارد. شما میزان پیشرفت طراحیهای جاری را در زبانه Design Runs مشاهده میکنید. در این بخش زبانه دیگری به نام Tcl Console وجود دارد که به کاربران حرفهای اجازه میدهد فرامین پیشرفته و سفارشی خودشان را اجرا کنند.