مقدمه

در بخش اول این سری آموزشی به شکل خلاصه مبانی اینترفیس AXI را با هم مرور کردیم. شاید یکی از مهمترین سوالاتی که بعد از مطالعه بخش اول برای شما پیش آمده باشد، این است که چگونه میتوانیم در زمان طراحی از عملکرد صحیح AXI اطمینان حاصل کنیم. به راستی برای شبیه سازی AXI چه گزینههایی پیش رو داریم؟ در این آموزش از پایگاه دانش هگزالینکس، شیوه شبیه سازی اینترفیسهای AXI را به صورت خلاصه با هم مرور میکنیم. ما قصد داریم شما را با یک IP Core اختصاصی که برای همین منظور توسعه داده شده است، آشنا کنیم. اگر علاقمند به این موضوع هستید، تا انتهای این مطلب با ما همراه باشید.

مقدمهای بر AXI Verification IP

راه حل پیشنهادی Xilinx برای تسهیل فرایند شبیه سازی اینترفیسهای AXI4 و AXI4-Lite استفاده از یک IP Core رایگان به نام AXI Verification IP (به اختصار AXI VIP) است که به سادگی از طریق مخزن IP های Xilinx در مجموعه نرم افزاری Vivado قابل فراخوانی است. این IP میتواند به عنوان AXI protocol checker نیز مورد استفاده قرار بگیرد.

در مخزن IP های Xilinx یک IP دیگر با نام AXI protocol checker نیز وجود دارد که وظیفه آن بررسی سازگار بودن تراکنشهای AXI با پروتکل AXI است.

PG101

به طور کلی AXI VIP برای یکی از موارد زیر بکار برده میشود.

- تولید فرامین کنترلی و دیتای payload نوشتن به عنوان یک جایگزین برای اینترفیس AXI Master

- تولید پاسخ برای تراکنش نوشتن و دیتای payload خواندن به عنوان یک جایگزین برای اینترفیس AXI Slave

- بررسی اینکه آیا تراکنشهای AXI به صورت کامل با پروتکل AXI سازگار است یا خیر؟

این IP فقط برای شبیه سازی است و قابل سنتز نیست، در صورتی که IP در مد path-through پیکرهبندی شود، بعد از سنتز IP با سیم جایگزین میشود.

PG267

این IP Core را میتوان به ۵ شکل متفاوت پیکرهبندی کرد:

- پیکرهبندی به صورت AXI Master VIP

- پیکرهبندی به صورت AXI Pass-through VIP بدون مدل حافظه

- پیکرهبندی به صورت AXI Pass-through VIP همراه با مدل حافظه

- پیکرهبندی به صورت AXI Slave VIP بدون مدل حافظه

- پیکرهبندی به صورت AXI Slave VIP همراه با مدل حافظه

این IP Core به صورت کامل توسط Xilinx مستند سازی شده است و API های آن به خوبی تهیه شدهاند و درون یک فایل ZIP قابل دانلود هستند. همینطور برای آشنایی بیشتر با AXI VIP میتوانید ویدئو کوتاه زیر را مشاهده بفرمایید.

مثالی از طراحی با AXI VIP

استفاده از AXI VIP چندان دشوار نیست. تنها کافی است یکبار مثالهای آماده Xilinx را اجرا کنید. شیوه استفاده از این IP به صورت مثالهای آماده درون محیط توسعه Vivado در اختیار کاربران قرار داده شده است.

برای ساخت و دسترسی به این مثالهای نمونه، مراحل زیر را به ترتیب اجرا کنید.

- در محیط Vivado یک پروژه جدید بسازید و سپس روی گزینه IP Catalog کلیک کنید.

- در فیلد جستجو عبارت AXI Verification IP را وارد کنید تا این IP به صورت اتوماتیک برای شما فیلتر شود. روی آن دو بار کلیک کنید، تا صفحه تنظیمات آن برای شما باز شود. بعد از اینکه تنظیمات مورد نظرتان را اعمال کردید روی گزینه Generate IP کلیک کنید.

- روی IP با کلید راست موس کلیک کنید و از منوی آن گزینه Open IP Example Design را انتخاب کنید.

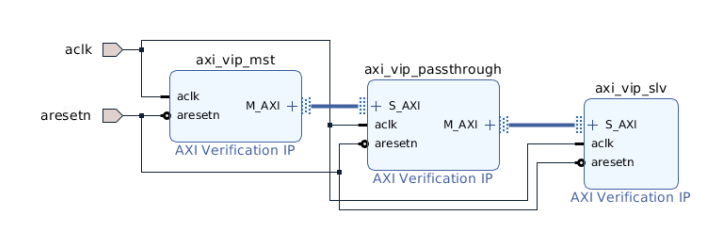

مثالهای نمونه Xilinx شامل سه AXI VIP است:

- یکی به صورت اینترفیس Master پیکرهبندی شده است.

- دیگری به صورت اینترفیس Pass-through پیکرهبندی شده است.

- و در نهایت آخری به صورت اینترفیس Slave پیکرهبندی شده است.

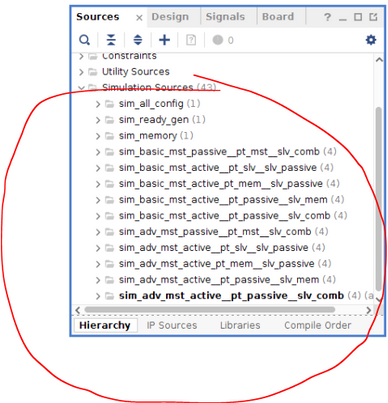

چندین تست بنچ در این پروژه وجود دارد که در هر کدام از آنها ترکیب متفاوتی از AXI VIP ها فراخوانی میشود و حالت خاصی شبیه سازی میشود.

نکته آخر اینکه، تمام فایلهای تست بنچ با زبان System Verilog توصیف شدهاند.

آنالیز تراکنشهای اینترفیس AXI

یکی از ویژگیهای کاربردی ابزار شبیه سازی Vivado قابلیت protocol instances است که میتواند به پنجره نمایش شکل موج اضافه شود تا سیگنال در سطح پروتکل مشاهده باشد. یعنی طراح میتواند علاوه بر مشاهده تغییرات سیگنالها، نحوه هندشیک سیگنالهای مختلف را نیز مانیتور کند. (

قابلیت Protocol Instance از نسخه 2019.1 به بعد به Vivado اضافه شده است و در نسخههای قبلی Vivado همچنان شکل موجها در الگوی مرسوم قبلی قابل مشاهده هستند.

Vivado 2019.1 Release note

از بین گزینههای موجود من گزینه sim_basic_mst_active_pt_mem__slv_passive از بین چندین مجموعه شبیه سازی که لیست آنها را مشاهده میکنید، انتخاب میکنم.

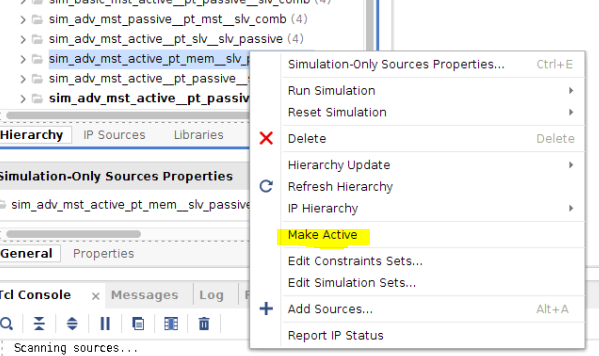

برای استفاده از هر کدام از این تست بنچها (مجموعه شبیه سازی یا simulation set)، با کلید راست موس در پنجره Source کلیک کنید و گزینه Make Active را انتخاب کنید.

مجموعه شبیه سازی انتخابی تنها از یک Master AXI VIP و Path-through AXI VIP تشکیل شده است. (که به عنوان یک Slave با سطح حافظه کار میکنند).

برای اجرای عملیات شبیه سازی کافی است روی گزینه Run Simulation در بخش Flow Navigator کلیک کنیم و کار را آغاز کنیم.

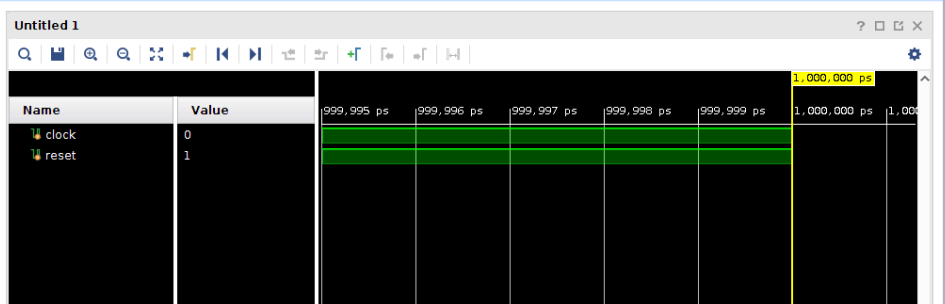

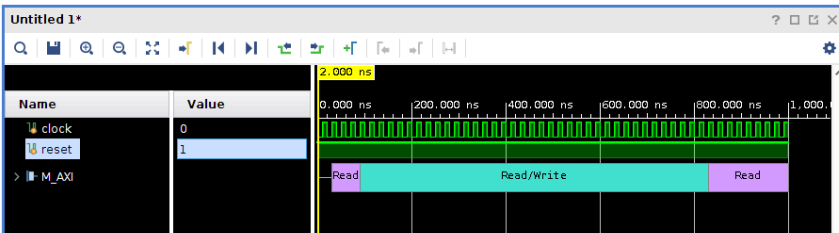

بلافاصله یک پنجره جدید Waveform باز میشود. در این صفحه جدید تنها سیگنالها clock و reset به صورت پیش فرض قابل مشاهده هستند.

اضافه کردن اینترفیسها به پنجره Waveform

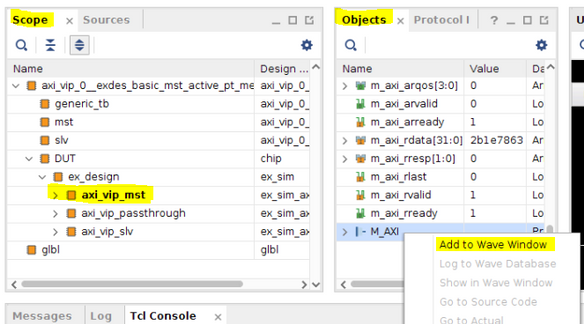

حالا نوبت اضافه کردن اینترفیسها است. پس اینترفیس AXI بین Master AXI VIP و Pass-through AXI VIP را به پنجره Waveform اضافه میکنیم.

برای اینکار در پنجره Scope ماژول Master AXI VIP جستجو میکنیم. (یعنی ماژول axi_vip_mst را در زیر بخش DUT/ex_design جستجو میکنیم. در ادامه میتوانیم از طریق پنجره Objects به تمامی پورتهای IP دسترسی داشته باشیم. در این پنجره به دنبال اینترفیس M_AXI میگردیم و با کلیک روی آن، این اینترفیس را به پنجره Waveform اضافه میکنیم.

بعد از اجرای مراحل بالا شما میتوانید، تراکنشهای AXI را در پنجره Waveform مشاهده کنید.

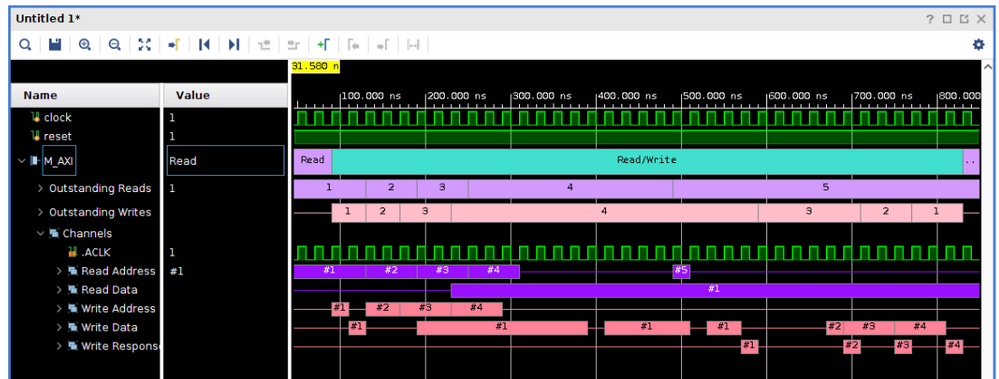

تقریباً تمامی اطلاعات مورد نیازمان درون پنجره Waveform وجود دارد. همانطور که در شکل نیز مشخص است در 1us اول، هر دو تراکنش خواندن و نوشتن انجام شده است.

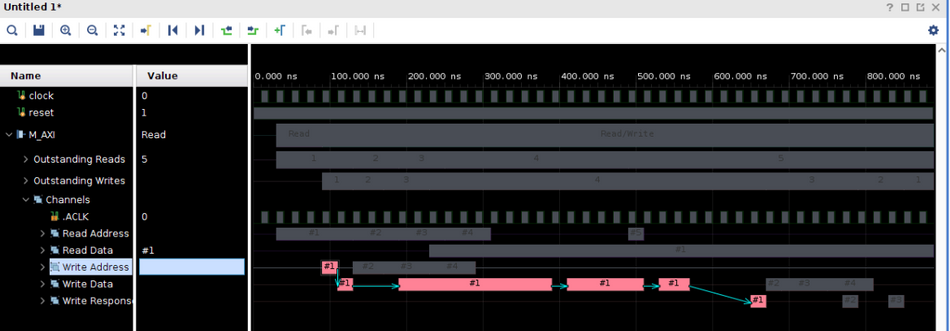

اگر در طول پنجره Waveform پیشروی کنیم و اینترفیس M_AXI را با وسواس بیشتری بررسی کنیم. تمام جزئیات مربوط به تراکنشها را مشاهده میکنیم. برخی از این جزئیات رو در ادامه برای شما لیست کردم.

شماره درج شده روی کانالها مطابق با شمارههای تراکنشهاست. ما میتوانیم ببینیم که پنج تراکنش خواندن روی کانالهای خواندن اتفاق افتاده است (صورتی رنگ) و چهار تراکنش روی کانالهای نوشتن رخ داده است.

پیشنهاد میکنم روی یک تراکنش خاص کلیک کنید، به این ترتیب شما میتوانید چگونگی انجام تراکنش را مشاهده کنید. برای مثال، اگر روی اولین تراکنش در کانال نوشتن کلیک کنیم، میبینیم که این تراکنش، به صورت burst انجام میشود. به این ترتیب که:

- ابتدا تراکنش با تعیین آدرس روی کانال نوشتن آدرس آغاز میشود.

- سپس دادههای Burst روی کانال نوشتن دیتا ارسال میشوند.

- در نهایت، در صورت موفقیت آمیز بودن عملیات نوشتن، Slave با ارسال یک کد در کانال نوشتن پاسخ، این مسأله را اعلام میکند.

جمع بندی

مطلبی که مطالعه کردید، بخش دوم از سری مقالات آموزشی AXI بود. در این آموزش مسأله شبیه سازی اینترفیس AXI را پوشش دادیم. با توجه به پیشنهاد Xilinx بهترین روش برای بازبینی و بررسی صحت عملکرد و فانکشنالیتی ماژولهای AXI Master و AXI Slave در یک طرح RTL استفاده از AXI VIP است.

این IP Core از یک مد دیگر تحت عنوان Path-through نیز پشتیبانی میکند، این مد به صورت کاملاً شفاف و ترنسپرنت برای کاربر این امکان را فراهم میآورد تا اطلاعات و ظرفیت خروجی تراکنش را مانیتور کند. به طور کلی AXI VIP با ارائه تست بنچها و مثالهای نمونه امکان تست عملکرد و قابلیتهای AXI3 ، AXI4 و AXI4-Lite را به سادگی فراهم میآورد. این مثالها میتوانند به عنوان یک نقطه شروع برای ساخت تست بنچهای کاملاً سفارشی برای طراحیهای مجهز به اینترفیس AXI3 ، AXI4 و AXI4-Lite مورد استفاده قرار بگیرند.

این IP Core نیازی به لایسنس ندارد و میتواند به صورت رایگان مورد استفاده قرار بگیرد.

منبع: با اقتباس از وبلاگ Xilinx