پیاده سازی الگوریتمهای پیچیده

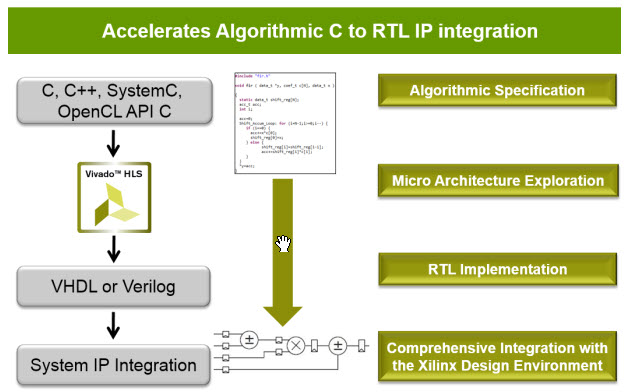

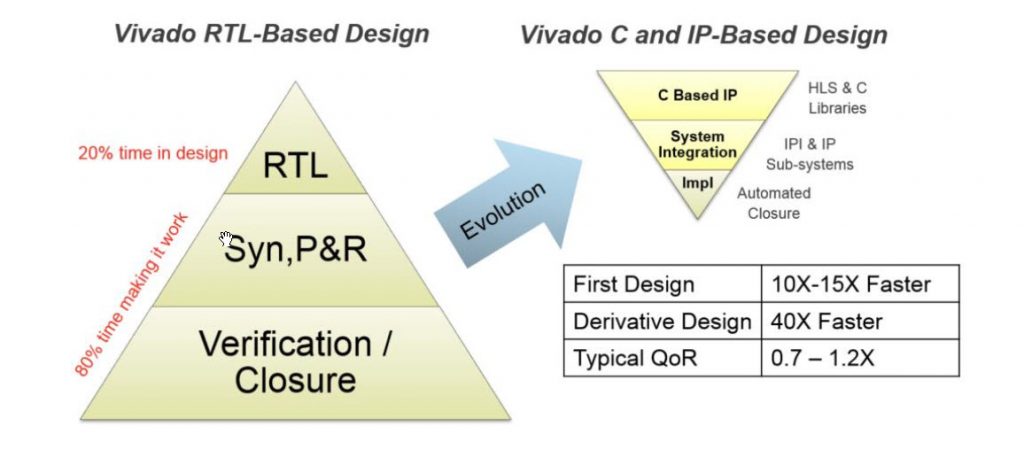

الگوریتمهای پیشرفتهای که امروزه در اپلیکیشنهای بیسیم و صنایع پزشکی و دفاعی مورد استفاده قرار میگیرند، پیچیدهتر از گذشته هستند. ابزار Vivado HLS به عنوان یک بروزرسانی کاربردی برای محیط توسعه Vivado، امکان ساخت IP های سفارشی از این الگوریتمها را با زبانهای سطح بالاتر و استفاده مستقیم از آنها در تراشههای قابل پیکره بندی FPGA را مهیا کرده است.

8 در مورد “ابزار طراحی VIVADO HLS”

چطور xilinx hls رو دانلود کنم؟ از سایت رسمی که سعی به دانلود میکنم بخاطر کشور ایران اصلا درست نمیتونم ثبت نام کنم، کاش فایل برنامه رو قرار بدید

سلام

کلیه نرم افزارهای Xilinx در سایتهای ایرانی قابل دانلود هستند.

برای دانلود کلیه نرم افزارها از سایت Xilinx بایدبه این صورت عمل کنید.

۱- با استفاده از VPN وارد سایت Xilinx شوید.

۲- با یک ایمیل و نام مستعار یک اکانت بسازید، برای ایمیل و نام در گوگل عبارت fake user name را جستجو کنید، تا یک نام کاربری به همراه آدرس، شغل ، کدپستی و ایمیل در اختیارتون قرار بده، (از gmail استفاده نکنید)

به بخش دانلودها برید و بدون اینکه VPN قطع شود. هر برنامه ای را که تمایل دارید دانلود کنید.

سلام. ممنون بابت مطالب مفیدتان. من چندتا سوال بپرسم.

در اولین تصویر بخش “معرفی ابزار Vivado HLS” یک تصویر قرار داده اید با عنوان “Accelerates Algoritmic C to RTL IP integration” که در آن زبان های قابل پیاده سازی برای HLS را نوشته اید. در زیر نام زیان های C و C++ و System C نام OpenCL API C هم قرار دارد! یعنی ابزار HLS قابلیت استفاده از کتابخانه ها و API های openCL را هم دارند؟

آیا ابزار HLS قابلیت پیاده سازی برروی FPGA که فقط بخش logic هست را نیز دارد؟ یا اینکه باید یک قسمت PS باشد مثل zynq یا microblaze و اینکه نیاز به پیاده سازی لینوکس (petalinux) برروی سخت افزار هم هست؟

ابزار SDAccel همان HLS هست؟

درود فراوان بر شما

دقتی که برای خواندن مطالب به خرج دادید قابل تقدیر است، امیدوام همواره سرحال و پر انرژی در مسیر پیشرفت باشید.

اما پاسخ سوألات:

۱- بله به جز System C که در نسخههای جدید حذف شده سایر زبانها همچنان پشتیبانی میشود.

۲- پاسخ به سوألتون در مورد OpenCL یک مقدار پیچیده است. ابزار Vivado HLS برای ساخت شتاب دهنده و IP Core استفاده میشه، قبل از معرفی Vitis این ابزار علاوه بر Vivado در SDx و SDAccel هم قابل فراخوانی بود. در SDAccel امکان استفاده از OpenCL وجود داشت و اگر بخشی از کدی که برای CPU در کامپیوتر نوشته شده بود برای اجرا به سمت FPGA ارسال میشد، به صورت اتوماتیک Vivado HLS درون SDAceel فراخوانی میشد و کدهای نرم افزاری را با ملاحظاتی برای پیاده سازی روی FPGA سنتز میکرد. اکنون که SDx و SDAccel با Vitis جایگزین شده این فرایند در Vitis اتفاق میافتد. پس به نوعی میشه گفت پاسخ سوألتون بله است اما با کلی شرط و شروط …

۳- در واقع تنها قابلیت Vivado/Vitis HLS پیاده سازی روی بخش لاجیک FPGA است و Vivado HLS اصلا کاری با arm درون تراشههای Zynq و یا MicroBlaze ندارد.

۴- داستان پتالینوکس به صورت کلی چیز دیگری است. پتالینوکس ابزاری برای توسعه لینوکس روی پردازندههای نرم یا سخت افزاری تولید Xilinx است.

۵- طبیعتاً جواب سوال آخر و حدس زدید. SDAccel و Vivado HLS به طور کلی با هم تفاوت دارند و کارکرد آن ها نیز متفاوت است.

سلام. خیلی ممنون بابت توضیحات کامل تان.

ابزار vivado HLS در نسخه 2017.4 شرکت xilinx که استفاده کرده ام بود، اما فکر کنم در نسخه های جدید دیگر موجود نیست!

لطفا در این باره راهنمایی می کنید.

سلام حمید عزیز،

از اینکه مطالب این صفحه نظرتون و جلب کرده خوشحالیم.

ابزار Vivado HLS همچنان در پکیج نصبی Xilinx ارائه میشود.

اگر هنگام نصب پکیج کامل شرکت Xilinx که Vitis نام داره، کل پکیج و نصب کنید به جای Vivado HLS ابزار Vitis HLS نصب میشه و اگر فقط مجموعه Vivado را نصب کنید همچنان Vivado HLS به عنوان یک بروزرسانی برای Vivado نصب میشود.

سلام. این مقاله و توضیحات بسیار مفید هستند.

توضیحاتی که دادید خیلی عالی است.

همچنان دنبال کننده سایت شما هستیم.

ممنون

سلام بر شما

از اظهار لطفتون سپاسگزارم