مقدمه

در الکترونیک دیجیتال لچ (latch) عنصری است که برای انجام عملیات نمونه برداری و نگه داری (sample and hold) مقادیر باینری مورد استفاده قرار میگیرد، و عملکردی مشابه فلیپ فلاپ (flip-flop) یا رجیستر (register) دارد، اما برخلاف فلیپ فلاپها، که حساس به لبه هستند و با لبه بالا رونده و یا پایین رونده کلاک نمونه برداری میکنند، لچها حساس به سطح هستند. در این مقاله از پایگاه دانش هگزالینکس در مورد لچ و چگونگی شکل گیری آن صحبت خواهیم کرد.

برای اینکه نحوه عملکرد یک لچ دیجیتال را به خاطر بسپارید، بد نیست مکانیزم باز و بسته شدن قفل یک درب را در نظر بگیرید. مشابه مکانیزمی که در شکل زیر میبینید.

هنگامی که اهرم کشویی قفل جمع شود، درب باز میشود و هر چیزی که پشت درب باشد از آن عبور میکند. اما به محض اینکه اهرم بسته شود، قفل و درب بسته میشوند و همه چیز متوقف میشود.

لچهای شفاف نوع D

کارکرد لچهای دیجیتال کاملاً مشابه کارکرد همتای آنالوگشان (قفل درب) است. زمانی که باز باشند، مقداری که در ورودی قرار داشته باشد به خروجی منتقل میشود، و زمانی که بسته باشند، هر مقداری که تا پیش از بسته شدن به خروجی منتقل شده باشد، روی خروجی باقی میماند.

با توجه مدلی که برای لچها و فلیپ فلاپها در مستندات Xilinx ارائه شده است، شماتیک زیر رفتار یک لچ نوع D در FPGA های این شرکت را نشان میدهد. در این شماتیک دادههای ورودی روی پورت D و دادههای خروجی روی پورت Q قرار میگیرند.

برای شروع مقادیر قرار گرفته روی ورودیها و گیتهای منطقی و تغییرات آنها در انیمیشن زیر را بررسی کنید. باکمی دقت، متوجه خواهید شد مقادیر قرار گرفته روی ورودی D زمانی که ورودی E فعال باشد (مقدار ‘1’) روی خروجی Q انتشار مییابند.

در عمل مادامی که ورودی فعال ساز (E) فعال باشد ما میتوانیم بگوییم که لچ ناپیدا (transparent latch) در مدار داریم. گویی هیچ عنصر منطقی در این شرایط وجود ندارد و مدار شبیه یک سیم است و به همین دلیل است که در ادبیات Xilinx لچ نوع D اغلب به عنوان لچ ناپیدا یا شفاف نام گذاری میشود.

در نقطه مقابل وقتی مقدار ‘0’ به ورودی E اعمال شود، خروجی Q هیچ عکس العملی به تغییرات روی D نشان نخواهد داد. در این حالت مقدار روی خروجی ثابت میشود و یا به بیان دقیق تر لچ میشود، و وضعیت Q تا زمانی که مجدداً ‘1’ شود بدون تغییر باقی میماند.

همانطور که در جدول زیر میبینید با یک مقایسه ساده مشخص میشود که جدول درستی برای لچهای ناپیدا مشابه جدول درستی فلیپ فلاپهایی است که ریست ندارند. با توجه به این جدول درستی میتوان فرض کرد لچ در لبه پایین رونده ورودی فعال ساز E، از ورودیهای D نمونه برداری میکند. این مسأله باعث میشود مادامی که سیگنال فعال ساز E یا همان کلاک ‘1’ است مقدار ورودی در خروجی منتشر شود، در حالی که فلیپ فلاپها چنین خاصیتی ندارند.

همانطور که در جدول روبرو میبینید با یک مقایسه ساده مشخص میشود که جدول درستی برای لچهای ناپیدا مشابه جدول درستی فلیپ فلاپهایی است که ریست ندارند. با توجه به این جدول درستی میتوان فرض کرد لچ در لبه پایین رونده ورودی فعال ساز E، از ورودیهای D نمونه برداری میکند. این مسأله باعث میشود مادامی که سیگنال فعال ساز E یا همان کلاک ‘1’ است مقدار ورودی در خروجی منتشر شود، در حالی که فلیپ فلاپها چنین خاصیتی ندارند.

| Q | E | D |

|---|---|---|

| 1 | 1 | 1 |

| 0 | 0 | 1 |

| Latched D value | 1 | 0 |

| Latched D value | 0 | 0 |

استنتاج لچ در کدهای HDL

اگر واقعاً نیاز به استفاده از یک لچ در کدهای HDL دارید، کد زیر این کار را برای شما انجام میدهد.

process(enable, d)

begin

if enable = '1' then

q <= d;

end if;

end process;

اما بیشتر لچها به صورت اتفاقی و بدون برنامه ریزی قبلی استنتاج میشوند، و این بدین معناست که یک اشتباهی در یکی از پروسسهای (process) کد VHDL شما وجود دارد.

کد زیر چگونگی شکل گیری تصادفی یک لچ را نشان میدهد. احتمالاً طراح قصد ایجاد یک process حساس لبه داشته است ولی فراموش کرده از عبارت شرطی if clk'event and clk = '1' then و یا if rising_edge(clk) then استفاده کند.

process(clk)

begin

if clk = '1' then

q <= d;

end if;

end process;

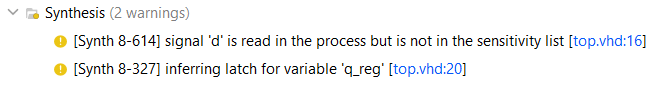

اگر کد فوق در محیط توسعه VIVADO سنتز شود، پیغام اخطاری با شماره [Synth 8-327] مبنی بر تولید و استنتاج لچ در کد شما گزارش میشود و در ادامه نیز معمولاً پیغام دیگری با شماره [Synth 8-614] برای توصیف دلیل تولید لچ در کنسول نمایش داده میشود.

خطای مرسوم دیگری که ممکن است باعث تولید لچ از کدها شود مربوط به عدم استفاده از کلید واژه else در جملات شرطی if هنگام استفاده از پروسسهای process ترکیبی در کدهای HDL میباشد. در مثال زیر به دلیل این که به ازای شرط read_data=’0’ هیچ مقداری برای خروجی data_out تولید نمیشود به جای فلیپ فلاپ یک لچ استنتاج میشود.

process(read_data, fifo_out)

begin

if read_data = '1' then

data_out <= fifo_out;

end if;

end process;

همانطور که احتمالاً به سادگی میتوان حدس زد، راه حل مناسب برای رفع این مشکل استفاده از کلید واژه else و مقدار دهی data_out است. به عنوان یک پیشنهاد همیشه این نکته را مد نظر داشته باشید که اگر برای تمامی ترکیبهای سیگنال کنترلی یک process به صراحت مقادیر خروجی را تعریف کنید، هیچ گاه لچ تولید نمیشود.

چرا نباید از لچها استفاده کنیم. مشکل کجاست؟

معمولاً تمامی ابزارهای سنتز در رابطه با تولید لچ در پیاده سازی مدارات روی FPGA اخطار میدهند، چون هیچ دلیلی برای استفاده از لچ وجود ندارد (البته استنثناء نیز وجود دارد). هر چند من تاکنون در طول دوران کاری حرفهایی خودم تا نیازی به استفاده از لچ نداشتهام.

در حالت کلی لچ ها همان کاری را انجام میدهند که ما از فلیپ فلاپها انتظار داریم، و در عین حال از نقطه نظر زمان بندی قابلیتهای کمتری دارند. برای اینکه محدودیتهای ناشی از استفاده از لچها را بهتر درک کنید اجازه بدهید مثال زیر را با هم مرور کنیم.

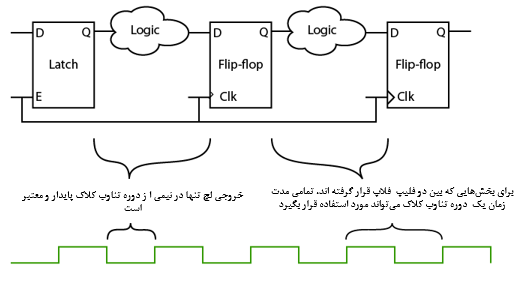

در بخش ابتدایی (نیمه سمت چپ) مثال بالا، یک لچ وجود دارد که خروجی آن از طریق یک مدار ترکیبی به یک فلیپ فلاپ میرسد.

ما از اینکه قبل از لچ دقیقاً چه چیزی وجود دارد و ورودی آن چگونه تولید میشود اطلاعی نداریم، از این رو باید فرض کنیم که ورودی آن میتواند در هر لحظه تغییر کند. با توجه توضیحاتی که تا به اینجا داده شد، تنها زمانی که خروجی لچ پایدار میشود در طول نیمه اول سیکل کلاک است زمانی که مقدار کلاک ‘0’ (بعد از لبه پایین رونده) است.

بخش دوم شماتیک بالا (نیمه سمت راست)، دو فلیپ فلاپ و مدار ترکیبی بین آنها را نشان میدهد. از آنجایی که هر دو فلیپ فلاپ نمونه برداری از داده ورودی را در لحظه وقوع لبه بالا رونده کلاک انجام میدهند سیگنال به اندازه تمام پریود کلاک برای انتشار درون مدارات ترکیبی زمان دارد. در حالی که مدت زمان انتشار داده در مدار ترکیبی بین لچ و فلیپ فلاپ تنها نصف پریود کلاک بود.

در عمل لچها انعطاف پذیری ابزار پیاده سازی را در زمان اجرای گام place & route به شدت محدود میکنند و برآورده شدن ملاحظات زمان بندی را سخت میکنند.

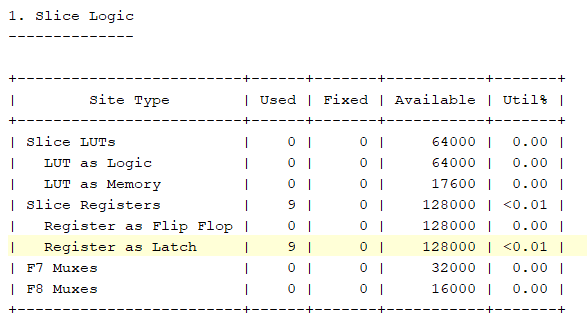

علاوه بر این، در تراشههای FPGA پیاده سازی هر دو عنصر لچ و فلیپ فلاپ با استفاده از یک عنصر یا رجیستر قابل پیکره بندی واحد درون CLB ها انجام میشود. این مسأله همانطور که در شکل زیر هم میبینید با توجه به گزارشهای تولید شده در محیط توسعه Vivado نیز به سادگی قابل تشخیص است.

توضیحات فوق نشان میدهد که برخلاف تصوراتی که اغلب مطرح میشود، استفاده از لچها باعث صرفه جویی در منابع مصرفی روی تراشه نمیشود زیرا از یک عنصر سخت افزاری واحد و قابل پیکره بندی درون CLB ها برای تولید فلیپ فلاپ و یا لچ استفاده میشود.

جمع بندی

در این نوشتار در رابطه با لچها و چگونگی شکل گیری آنها توضیحات مختصری ارائه شد. در اکثر موارد حتی در صورت سنتز لچ به جای فلیپ فلاپ بازهم مدارات پیاده سازی شده به خوبی کار میکنند، حتی اگر مدار تولیدی مدار مد نظر شما نباشند. لچها باعث افزایش سربار و ابجاد محدودیت برای ابزار پیاده سازی هنگام مسیریابی درون تراشه میشوند در حالی که هیچ مزیتی نسبت به فلیپ فلاپها برای طرح به همراه ندارند. از این رو پیشنهاد با کمی دقت در کد نویسی از شکل گیری آنها جلوگیری کنید.