مقدمه

یک فیلتر FIR تقریباً میتواند برای فیلتر کردن هر فرکانسی در حوزه دیجیتال به کار گرفته شود و برای طراحی و پیاده سازی آن میتوان از طیف وسیعی از نرم افزارها استفاده کرد که هر کدام ویژگیها و مزایای خاص خودشان را دارند. در این آموزش از پایگاه دانش هگزالینکس قصد داریم مسیر پیاده سازی و طراحی یک فیلتر FIR با ابزار System Generator for DSP را همراه با شما مرور کنیم. اگر علاقمند به پیاده سازی الگوریتمهای پردازش سیگنال در FPGA هستید، تا انتها ما را همراهی کنید.

این یک مقاله آموزشی کامل در رابطه با پیاده سازی فیلترهای دیجیتال روی FPGA نیست و فرض بر این است که شما با مفاهیم اولیه آن آشنا هستید. نرم افزار Matlab و محیط Simulink را میشناسید. اما اگر تجربه کار با آنها را ندارید، توضیحات به شکلی است که مطمئناً با کمی تلاش موفق به اجرای گام به گام آن خواهید شد.

پیش زمینه

فرض کنیم به تازگی مشغول کار در شرکتی شدهاید که کار اصلی آن پیاده سازی الگوریتمهای پردازش سیگنال است. شرکت در حال کار روی فیلترهای دیجیتال است و تصمیم دارد در محصول جدیدش فیلترهای آنالوگ قدیمی را با فیلترهای دیجیتال جدید جایگزین کند. هدف از این جایگزینی هم بهبود عملکرد سیستم و کاهش هزینه تمام شده محصول است. این جایگزینی مزایای رقابتی قابل ملاحظهای نیز به همراه دارد و احتمالاً باعث محبوبیت مضاعف این محصول جدید در بازار میشود. براساس طراحیهای صورت گرفته، مشخصات این فیلتر دیجیتال میان گذر، تک کانال و تک نرخ به شرح زیر است.

- فرکانس نمونه برداری: (Sampling Frequency = 1.5MHz)

- فرکانس قطع اول: (FStop 1 = 270KHz)

- فرکانس گذر اول: (FPass 1 = 300KHz)

- فرکانس گذر دوم: (FPass 2 = 450KHz)

- فرکانس قطع دوم: (FStop 2= 470KHz)

- تضعیف در هر دو سمت: (Att. = 54dB)

- ریپل باند گذر: (Pass Band Ripple = 1)

اگر با این پارامترها و مشخصهها آشنا نیستید به مقاله مقدمهای بر فیلترها مراجعه کنید.

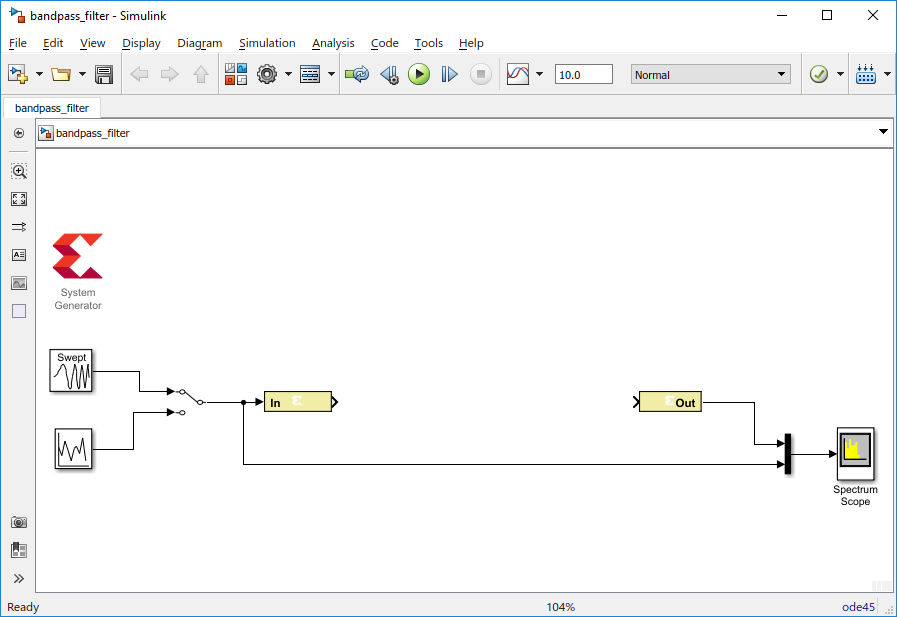

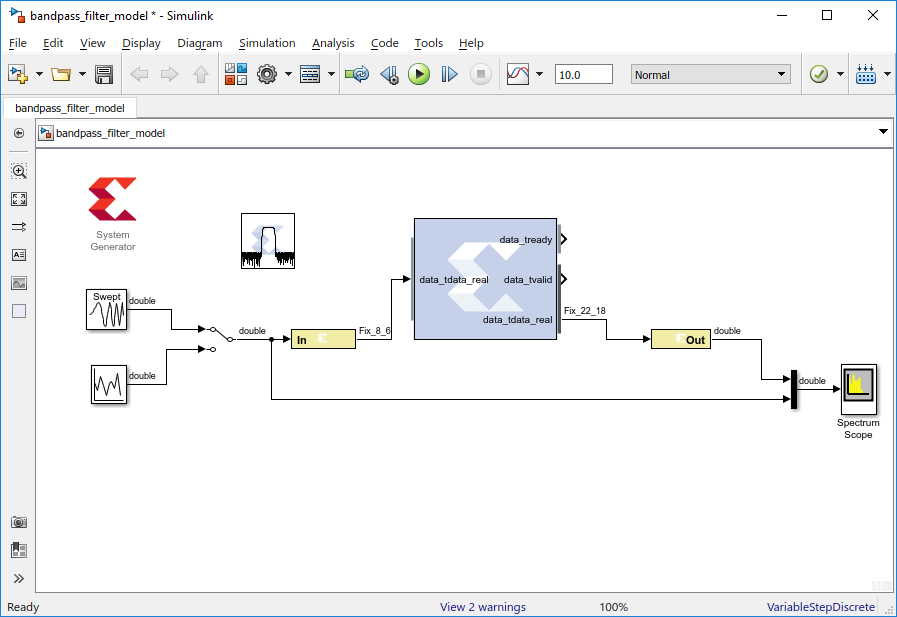

شرکت برای عملیاتی کردن این فیلتر تصمیم گرفته است از تراشه FPGA به عنوان بستر پیاده سازی استفاده کند و مدیرتان از شما خواسته است مسئولیت پیاده سازی این فیلتر را بر عهده بگیرید. مدیرتان با آگاهی از این موضوع که شما به اندازه کافی به نرم افزار Matlab مسلط هستید و تجربه کار با ابزار Simulink را دارید، یک مدل اولیه به صوت زیر در اختیار شما قرار داده است و انتظار دارد بر اساس این تعریف اولیه کارتان را شروع کنید و به نحو مطلوب به پایان برسانید.

این مدل اولیه بسیار کارآمد است زیرا شما میتوانید از آن برای شبیه سازی طراحی خودتان استفاده کنید. سیگنالهای ورودی و خروجی به سادگی از این مدل قابل استخراج هستند. با توجه به توضیحاتی که به شما داده شده است، انتظار میرود طرح نهایی با استفاده از دیتای Random (تصادفی) و همینطور یک سیگنال Chirp تست و شبیه سازی شود. در این مدل برای تولید این دو سیگنال از بلوکهای Random Source و Chirp در Simulink استفاده شده است. یک سوئیچ انتخاب گر نیز برای انتخاب بین این دو ورودی در مدل اولیه در نظر گرفته شده است.

از سوی دیگر برای آنالیز خروجی فیلتر باید طیف فرکانسی سیگنال خروجی بررسی شود. یعنی کافی است در انتهای کار پاسخ فرکانسی این فیلتر ممیز ثابت ترسیم و با ورودی اصلی شود. در این مدل با استفاده از یک بلوک Spectrum Scope و یک بلوک Mux سیگنال ورودی و سیگنال خروجی فیلتر در یک صفحه نمایش داده میشوند تا شما بتوانید آنها را باهم مقایسه کنید. خب حالا سؤال اینجاست اگر شما واقعاً در چنین موقعیتی قرار بگیرید، از کجا شروع میکنید؟

اگر فرض کنیم که دانش شما در حوزه پردازش سیگنال و پیاده سازی این نوع از الگوریتمها با استفاده از زبانهای HDL نسبتاً محدود است، در این صورت استفاده از ابزار System Generator for DSP میتواند گزینه مناسبی برای شما باشد. در ادامه این آموزش کلیه مراحلی را که میتواند توسط شما برای طراحی و پیاده سازی مورد استفاده قرار گیرد، گام به گام اجرا میکنیم.

طراحی و پیاده سازی فیلتر FIR

ابزارهای مورد نیاز برای طراحی و پیاده سازی عبارتند از:

- نرم افزار Matlab و ابزار FDATools برای طراحی فیلتر

- ابزار Simulink و System Generator for DSP برای مدل سازی و تست فیلتر

فراموش نکنید که نسخه Matlab و System Generator for DSP باید باهم سازگار باشند و System Generator for DSP باید پیش از شروع کار پیکره بندی شده باشد.

در این آموزش از نسخه 2017b نرم افزار Matlab و نسخه 2018.2 محیط توسعه Vivado که ابزار System Generator for DSP همراه با آن نصب می شود، استفاده شده است. اگر نسخه ابزارهای شما متفاوت است ممکن است تصاویری که مشاهده میکنید با تصاویر ما متفاوت باشد. اما به طور کلی روال کار هیچ تفاوتی ندارد.

همانطور که اشاره شد، برای شبیه سازی و ارزیابی عملکرد فیلتر از دو سیگنال تست استفاده میکنیم. مشخصات دقیق این دو سیگنال تست به این صورت است:

- یک سیگنال Chirp که فرکانسش بین فرکانس صفر تا 750MHz تغییر میکند.

- یک سیگنال Random با توزیع یکنواخت بین صفر تا یک، انتخاب توزیع یکنواخت برای تست فیلتر ممیز ثابت نسبت به سایر توزیع ها بهتر است، زیرا کرانهای آن محدود است.

فراید طراحی و ارزیابی فیلتر FIR در سه گام انجام میشود.

- طراحی فیلتر در Matlab با استفاده از ابزار FDA Tools و تولید ضرائب فیلتر

- مدل سازی و ساخت فیلتر در Simulink

- شبیه سازی و تست نرم افزاری فیلتر

قبل از شروع کار فایل اولیه مربوط به مدل را از اینجا دانلود کنید و یک جای مناسب روی کامپیوترتان ذخیره کنید. این فایل bandpass_filter.slx نام دارد.

گام اول: طراحی فیلتر

۱- نرم افزار Matlab یا بهتره بگم System Generator for DSP را اجرا کنید.

۲- پوشه کاری Matlab را به آدرسی که فایل bandpass_filter.slx در آن ذخیره شده است، تغییر دهید.

۳- با کلیک روی این فایل و یا با تایپ نام آن در صفحه Command این مدل را اجرا کنید و منتظر بمانید تا صفحه Simulink به شما نمایش داده شود.

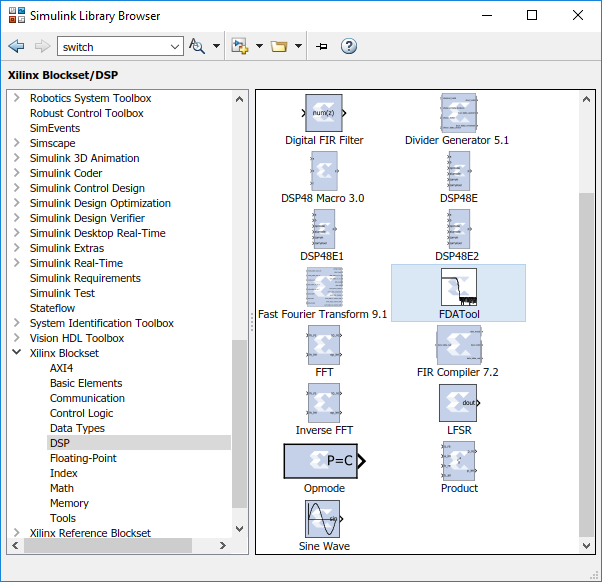

۴- با کلیک روی گزینه Library Browser در نوار ابزار، پنجره کتابخانههای Simulink را فراخوانی کنید.

۵- از پنجره سمت چپ و از لیست کتابخانهها گزینه Xilinx Blockset > DSP را انتخاب کنید و در پنجره سمت راست بلوک FDATool را پیدا کنید. برای اضافه کردن این بلوک به مدل میتوانید از منوی راست کلیک گزینه add block to model را نتخاب کنید و یا از کلیدهای ترکیبی Ctrl+I استفاده کنید.

۶- پنجره کتابخانه را ببندید و به صفحه مدل Simulink باز گردید.

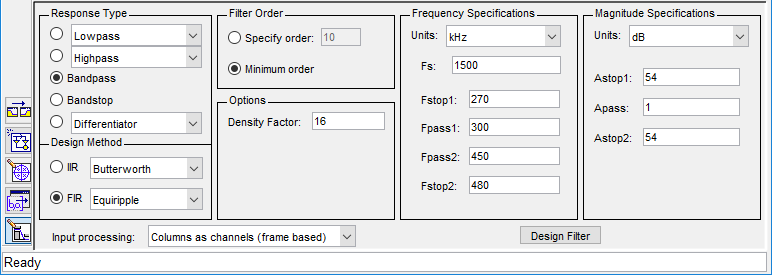

۷- با دوبار کلیک روی بلوک FDATool پنجره تنظیمات آن را فراخوانی کنید و با پارامترهای فیلتر را به صورت زیر روی آن اعمال میکنید.

Response Type: Bandpass Units: KHz Sampling Frequency (Fs) = 1.5 MHz Fstop 1 = 270 kHz Fpass 1 = 300 kHz Fpass 2 = 450 kHz Fstop 2 = 480 kHz Attenuation on both sides of the passband = 54 dB (Astop1 and Astop2) Pass band ripple = 1 (Apass)

بعد از تنظیم پارامترها پنجره تنظیمات FDATool مشابه شکل زیر خواهد بود.

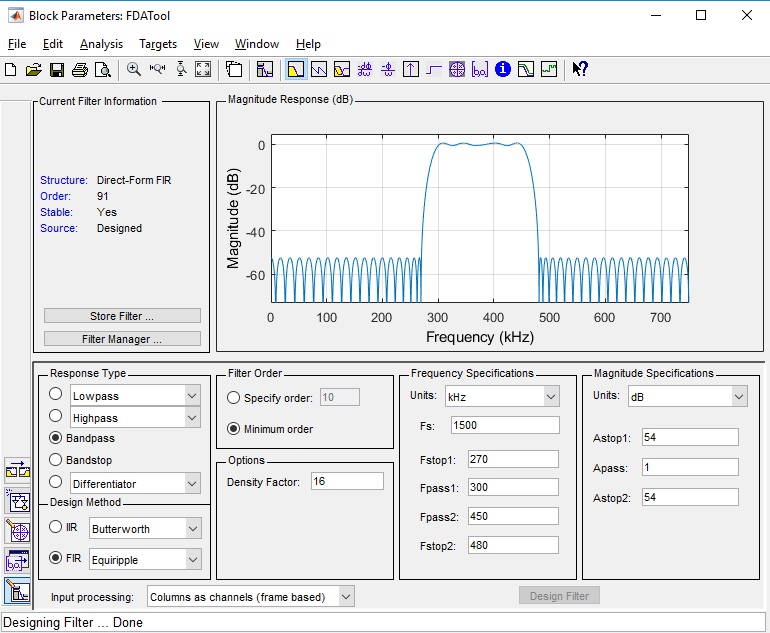

۸- روی گزینه Design Filter کلیک کنید. تا ابزار فیلتر مورد نظر شما را طراحی کند.

با اتمام کار طراحی پاسخ فرکانسی فیلتر، بروز میشود و نتیجه کار شکل زیر خواهد بود.

حالا با توجه به طراحی انجام شده و اطلاعات قابل مشاهده در این صفحه میتوانید مرتبه فیلتر را حدس بزنید؟ پاسخ خود را در کامنتهای ذیل همین مطلب برای ما بنویسید.

بعد از اتمام فرایند طراحی در Matlab به تنها چیزی که نیاز داریم گرفتن یک خروجی از ضرائب فیلتر است، پس در ادامه از ضرائب تولید شده یک خروجی مناسب تولید کنید.

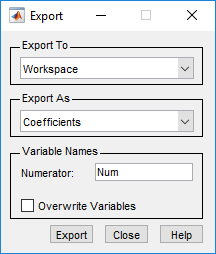

۹- روی گزینه Export در منوی فایل کلیک کنید تا پنجره تنظیمات آن برای شما فعال شود. در فیلد Numerator عبارت Num را وارد کنید تا ضرائب با نام Num به محیط کاری Matlab ارسال شوند. سایر تنظیمات پیش فرض را بپذیرید و روی Export کلیک کنید.

۱۰- پنجره تنظیمات FDATool را ببندید و مدل خود را ذخیره کنید.

حالا اگر به صفحه Workspace در Matlab نگاهی بیاندازید، متغیر Num را در لیست متغیرها مشاهده خواهید کرد. با تایپ عبارت Num در صفحه Command میتوانید مقدار این ضرائب را نیز مشاهده کنید. بد نیست این ضرائب را کمی بیشتر بررسی کنید و مقدار مینیمم و ماکزیمم آن را چک کنید تا رنج دینامیکی ضرائب را متوجه شوید. به عنوان تمرین مقدار بزرگترین و کوچکترین ضریب را در کامنتهای انتهای این مطلب بنویسید، به نظر شما چرا آگاهی از رنج دینامیکی ضرائب برای ما مهم است؟

نکته:

برای بررسی این مقادیر از دستور min و max استفاده کنید.

کار ساخت فیلتر به اتمام رسید حالا شما یک فیلتر طراحی شده و آماده دارید و میتوانید کار پیاده سازی آن را آغاز کنید.

گام دوم: مدل سازی و ساخت فیلتر

برای پیاده سازی این فیلتر آسان ترین و چه بسا بهترین راه استفاده از IP Core های آماده Xilinx است که با جستجو در کتابخانه Xilinx Blockset قابل فراخوانی هستند. برای تکمیل مدل و ساخت فیلتر به صفحه Simulink برگردید و به صورت زیر عمل کنید.

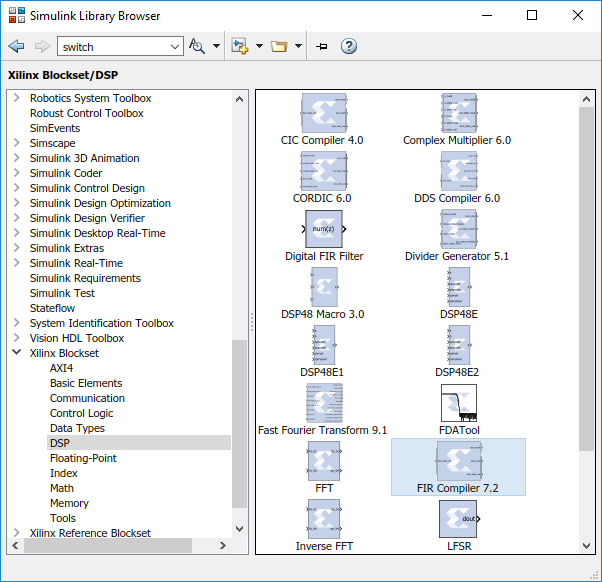

۱- با کلیک روی گزینه Library Browser در نوار ابزار پنجره کتابخانههای Simulink را فراخوانی کنید.

۲- از پنجره سمت چپ و از لیست کتابخانهها گزینه Xilinx Blockset > DSP را انتخاب کنید و در پنجره سمت راست بلوک فیلتر FIR که با عنوان FIR Compiler 7.2 قابل شناسایی است، به مدل خود اضافه کنید. (از منوی راست کلیک و یا از کلیدهای ترکیبی Ctrl+I کمک بگیرید).

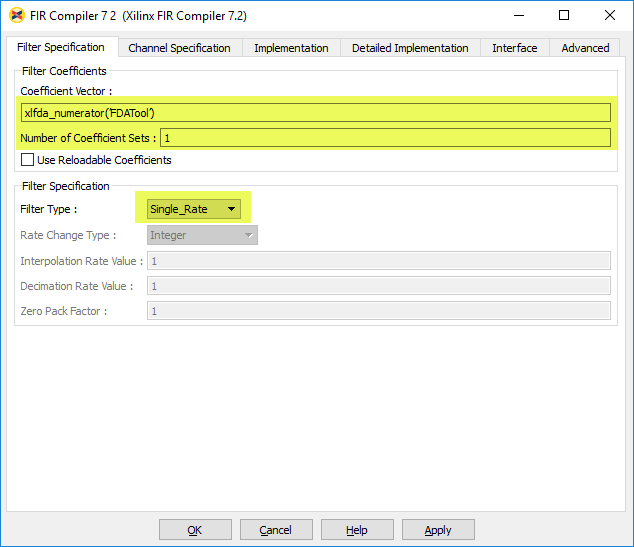

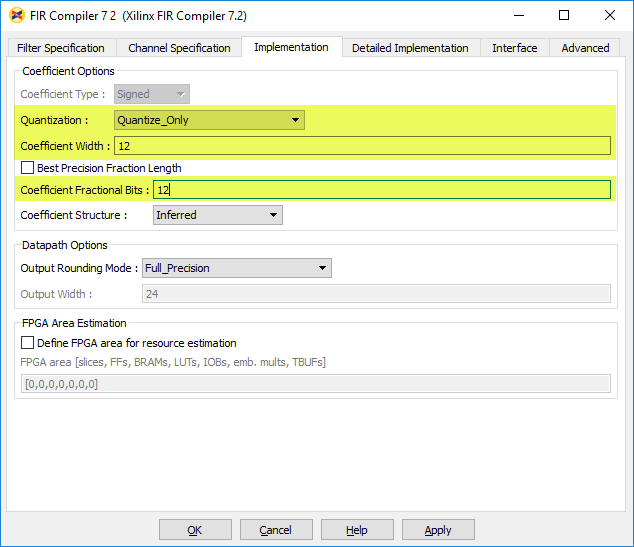

۳- در صفحه مدل با جابجایی و تغییر سایز بلوک صفحه خود را مرتب کنید. روی بلوک FIR دوبار کلیک کنید. در پنجره تنظیمات آن پارامترهای زیر را اعمال کنید و سپس روی OK کلیک کنید.

Filter Specification tab Coefficients : xlfda_numerator(‘FDATool’) Number of Coefficient Sets: 1 Filter type: Single_rate Implementation tab Coefficient Structure: Inferred Quantization: Quantize_only Coefficients Width: 12 Coefficients Fractional Bits: 12

اگر علاقمند به آشنایی با جزئیات بیشتر این IP Core هستید، سایر تبها را نیز بررسی کنید و پارامترهای پیش فرض را چک کنید. آیا میتوانید معماری مورد استفاده برای این فیلتر را شناسایی کنید؟ کار چندان سختی نیست کمی دقت کنید.

۴- ارتباط میان بلوک FIR و سایر بخشها در مدل را مشابه شکل زیر برقرار کنید.

از خروجی پورت Getway In برای تأمین ورودی فیلتر استفاده کنید، خروجی فیلتر را به ورودی پورت Gateway Out متصل کنید. خیلی کار پیچیدهای نیست. این دو پورت مرزهای بلوکهای قابل پیاده سازی را تعیین میکنند.

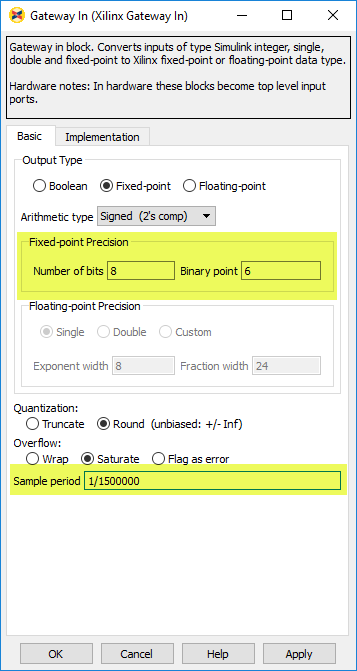

۵- روی پورت ورودی Gateway In دوبار کلیک کنید و در بخش Output Type پارامتر Fixed point را انتخاب کنید در فیلد Number of Bits تعداد بیتهای متغیر ورودی را برابر با ۸ و در فیلد Binary Point تعداد بیتهای اعشار را برابر با ۶ قرار دهید تا فرمت ممیز ثابت آن را روی FIX_8_6 تنظیم شود. مقدار پارامتر پریود نمونه برداری در فیلد sample period را برابر با 1/1500000 قرار دهید.

نکته:

به یاد دارید که در گام اول هنگام طراحی فیلتر FIR فرکانس نمونه برداری فیلتر را روی 1.5MHz تنظیم کردیم از این رو مقدار پریود نمونهها کاملاً مطابق با ملاحظات فیلتر تعیین شده است.

کار ساخت مدل در همین جا به پایان رسید. شما میتوانید با اجرای شبیه سازی، عملکرد طرح خود را ارزیابی کنید.

گام سوم: شبیه سازی و تست فیلتر

برای بررسی عملکرد فیلتر FIR باید طراحی را شبیه سازی کنید. پس مراحل زیر را با دقت اجرا کنید:

۱- با استفاده از سوئیچ انتخابگر منبع تولید سیگنال Chirp را به عنوان سیگنال ورودی تست انتخاب کنید.

۲- در نوار ابزار روی گزینه Start Simulation کلیک کنید و شبیه سازی را اجرا کنید.

۳- اگر صفحه اسپکتروم آنالایزر به صورت اتوماتیک فعال نشد. با دوبار کلیک روی آن، صفحه آنالایزر را باز کنید.

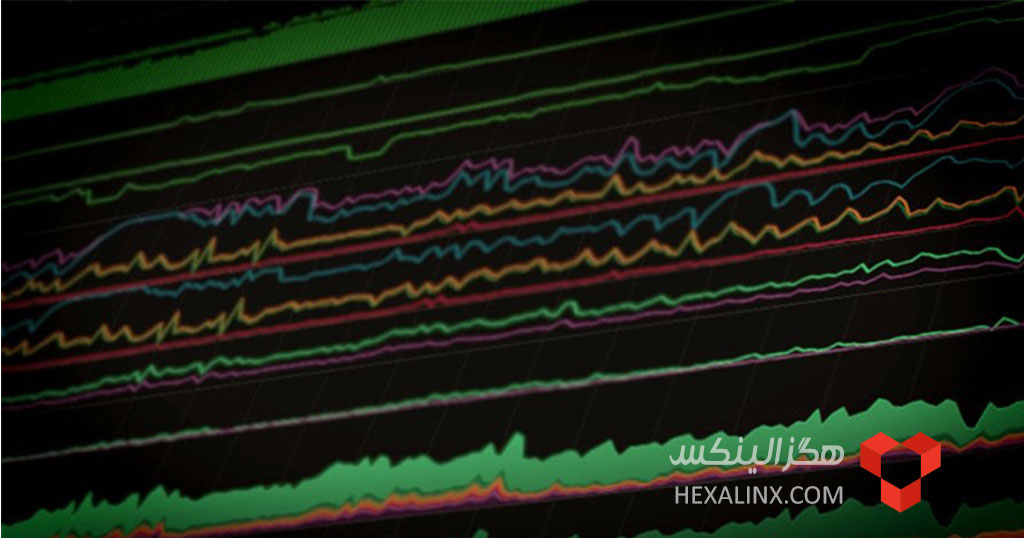

همانطور که مشاهده میکنید، سیگنال خروجی فیلتر که با رنگ زرد در صفحه اسپکتروم نمایش داده شده است در خارج از باند عبور به شکل محسوسی تضعیف شده است. سیگنال آبی رنگ هم ورودی Chirp است که مرتباً فرکانسش تغییر میکند و تنها زمانی که فرکانس آن دقیقاً درباند عبور فیلتر قرار بگیرد، بدون تضعیف به خروجی منتقل میشود.

۴- بدون اینکه اجرای شبیه سازی را متوقف کنید، با تغییر وضعیت سوئیچ منبع تولید سیگنال Random را به عنوان سیگنال ورودی تست انتخاب کنید و مجدداً صفحه اسپکتروم آنالایزر را بررسی کنید.

آیا میتوانید مشاهدات خود را توصیف کنید؟ به نظر میرسد موفق به فیلتر کردن سگنال ورودی شدهاید. به شما تبریک میگویم احتمالاً مدیرتان با شنیدن این خبر خوشحال میشود. اما دقت کنید که کار هنوز تمام نشده و شما باید طرح خود را پیاده سازی کنید و بعد روی سخت افزار تست کنید.

۵- با کلیک روی دکمه Stop در نوار ابزار شبیه سازی را متوقف کنید.

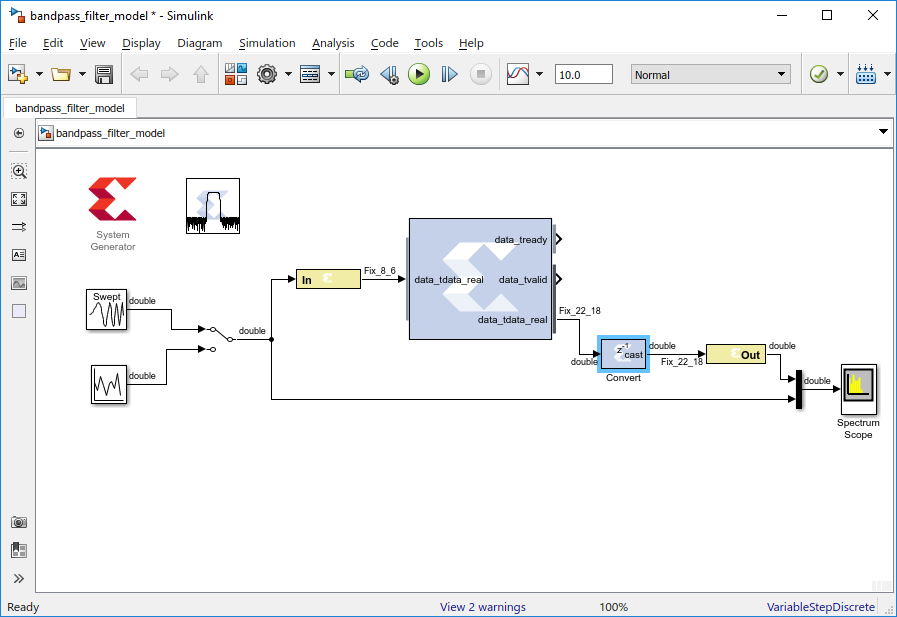

۶- به کتابخانههای Simulink برگردید و از سمت چپ گزینه Xilinx Blockset > Xilinx Basic Element را انتخاب کنید. سپس از پنجره سمت راست یک بلوک Convert به مدل خود اضافه کنید.

۷- این بلوک را بین خروجی فیلتر و پورت Gateway Out قرار دهید و مشابه شکل زیر اتصالات آن را برقرار کنید.

۸- در پنجره تنظیمات این بلوک پارامترهای زیر را اعمال کنید (FIX_8_6).

Output Type : Fixed-point Number of bits : 8 Binary point: 6 Quantization: Truncate Overflow: Wrap

۹- مجدداً شبیه سازی را اجرا کنید و مشاهدات خود در صفحه اسپکتروم را با اجرای قبلی مقایسه کنید. مشاهده میکنید که به ازای هر دو سیگنال ورودی Chirp و Random رنج دینامیکی تغییرات سیگنال خروجی محدود شده است. دلیل این مسأله کاهش تعداد بیتهای مورد استفاده برای نمایش خروجی فیلتر است. در بسیاری از موارد باید رشد بیت را کنترل کنیم و عرض بیت خروجی را مشابه عرض بیت ورودی تنظیم کنیم.

برای تست روی سخت افزار باید با استفاده از بلوک System Generator پروژه را سنتز و پیاده سازی کنید و سپس فایل بیت خروجی مناسب برای تراشه هدفتان را تولید کنید.

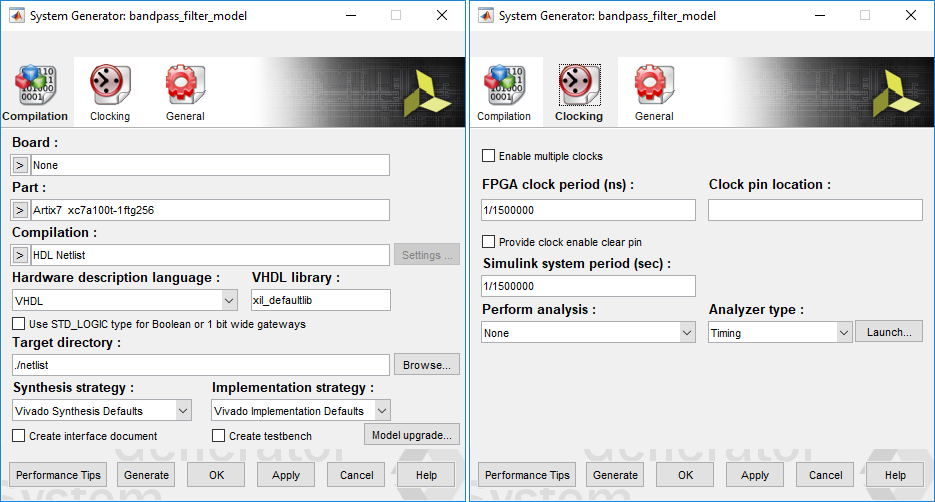

۱۰- اگر فایل پروژه خود را ذخیره نکردید. با کلیک روی گزینه Save آن را ذخیره کنید و سپس با دوبار کلیک روی System Generator Token که همان آیکون قرمز رنگ در سمت چپ تصویر است، پنجره تنظیمات سنتز و پیاده سازی را فراخوانی کنید.

در این پنجره کلیه تنظیمات مربوط به پروژه RTL نهایی در دسترس شماست و میتوانید با توجه به تراشه یا بورد هدف انتخابی طرح خود را پیاده سازی کنید. زبان RTL خروجی، کلاک کاری سیستم، استراتژیهای سنتز و پیاده سازی و همینطور آدرس پوشه پروژه به همراه بسیاری از گزینههای دیگر همگی توسط شما قابل کنترل است. علاوه بر این قادر به تولید تست بنچ و مستندات مربوط به اینترفیسهای طرح خود نیز هستید.

۱۱- فقط مطمئن شوید که مقدار پارامتر Simulink system period در صفحه Clocking روی 1/1500000 تنظیم شده باشد. سایر تنظیمات پیش فرض را بپذیرید و سپس روی apply کلیک کنید.

۱۲- روی Generate کلیک کنید تا خروجی تولید شود. ساخت خروجی ممکن است کمی طول بکشد و بعد از اتمام آن پیغام Generation Complete روی صفحه ظاهر میشود.

حالا شما یک پروژه کامل دارید که میتوانید با مراجعه به پوشه مربوطه روی کامپیوتر خود آن را اجرا و مدیریت کنید. شما میتوانید در ادامه با کمک Vivado فایل بیت خروجی را تولید و روی بورد نهایی تست کنی. در انتها متذکر میشوم که شما با هر سخت افزاری که در اختیار دارید میتوانید خروجی نهایی را روی بورد به صورت سخت افزاری تست کنید.

جمع بندی

بدون شک برای طراحی فیلتر FIR در FPGA راههای دیگری نیز وجود دارد که میتوانید با توجه تجربه و دانش خود از آنها استفاده کنید. ابزار System Generator for DSP یکی آسان ترین راهحلها برای نیل به این هدف است.

در این آموزش شما با نحوه فراخوانی ابزار FDATool و شیوه کار با آن برای طراحی یک فیلتر آشنا شدید. سپس با استفاده از گزینه Export یک خروجی از ضرائب فیلتر تهیه کردید و در نهایت به کمک بلوک FIR Compiler در محیط System Generator for DSP یک فیلتر قابل پیاده سازی روی سخت افزار طراحی کردید. شما میتوانید این طرح با توجه به دانش خودتان ویرایش کنید و برای مدل سازی الگوریتمهای پردازش سیگنال از آن استفاده کنید. در آموزشهای بعدی با استفاده از FIR Compiler IP Core و همینطور کدنویسی HDL از منظری دیگر مجدداً مسیر طراحی این فیلتر را بررسی خواهیم کرد.

منبع: Xilinx

4 دیدگاه برای “طراحی فیلتر FIR با ابزار System Generator for DSP”

سلام

وقتتون بخیر، من میخواهم از متلب نسخه جدید و Vitis Model Composer برای نسخههای 2025 استفاده کنم. لایسنسهای موجود در سایتهای دانلود و کرک، اجازهی اکسپورت از model Composer را نمیدهد، میخواستم بپرسم که شما فایل کرکش را دارید که به اشتراک بگذارید؟

یا اگر لینک دانلودی موجود است قرار بدهید؟

باتشکر

از نسخه های پایین تر استفاده کنید. چون جدا از مشکل لایسنس، استفاده از نسخه های خیلی جدید به دلیل وجود باگ ممکنه مشکل ایجاد کنه

مرتبه ی فیلتر 91 است

درود بر شما زهرای عزیز

پاسخ شما صحیح است. موفق باشید.