مقدمه

از Verilog و VHDL متنفرید، شما تنها نیستید. بالاخره بعد از درخواستهای فراوان توسعه دهندگان، شرکت Xilinx یک پلتفرم طراحی جدید برای کار و توسعه سیستم روی تراشههای FPGA معرفی کرد.

شرکت Xilinx در جریان کنفرانس سالیانه توسعه دهندگان XDF2019 از پلتفرم جدید نرم افزاری خودش تحت عنوان Vitis رو نمایی کرد. پلتفرمی که پنج سال برای توسعه آن زمان صرف شده و به طراحان اجازه میدهد به صورت مستقیم با استفاده از ابزارها و زبانهای توسعه مرسوم همچون پایتون و ++C روی معماری سخت افزاری تراشههای FPGA طراحی کنند.

در این آموزش از پایگاه دانش هگزالینکس سعی داریم نگاهی کوتاه به ابزار توسعه جدید Xilinx بیاندازیم و اولین پروژه خودمان را اجرا کنیم. اگر علاقمند به جزئیات این موضوع هستید، تا انتها با ما همراه باشید.

نصب Vitis

وقتی که کار با Vitis را آغاز میکنیم، اولین چیزی که توجه ما را جلب میکند، جایگزین شدن SDSoC ، SDAccel و حتی SDK با مجموعه نرم افزاری Vitis است. به عنوان یک ابزار یکپارچه، در واقع قرار است Vits برای توسعه یک سیستم نهفته دقیقاً مشابه SDK و یا شتاب دهی یک اپلیکیشن کاملا مشابه SDSoC و SDAccel بکارگرفته شود.

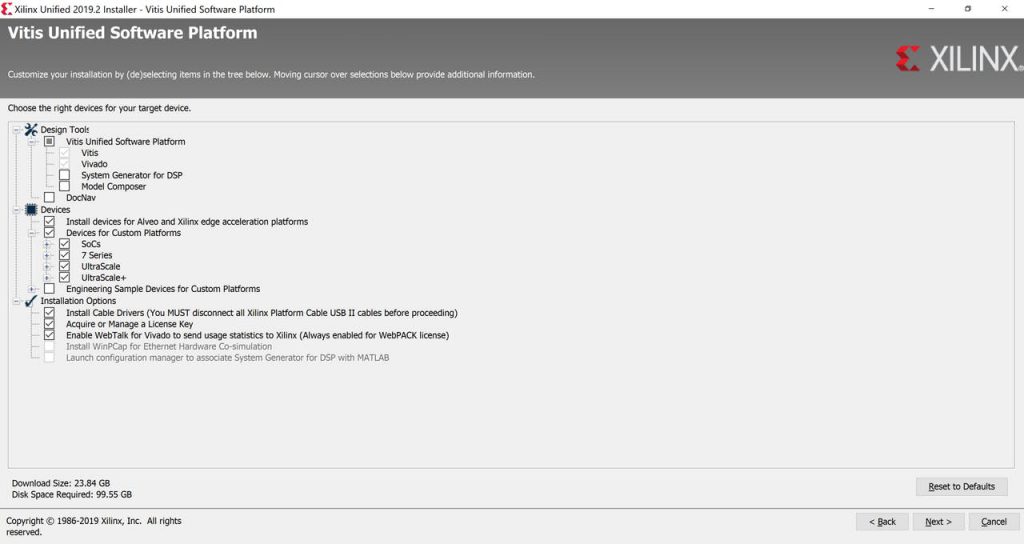

با توجه به اینکه دقیقا به دنبال چه چیزی هستیم میتوانیم بسته نصبی را به شکلهای متفاوتی سفارشی کنیم.

توسعه اپلیکیشنهای شتاب دهی نیازمند سیستم عامل لینوکس با حجم قابل توجهی از حافظه RAM است. حداقل 32GB یا حتی 64GB حافظه نیاز است. از سوی دیگر، توسعه یک سیستم نهفته روی هر دو سیستم عامل لینوکس و ویندوز امکان پذیر است. البته بازهم حافظه مورد نیاز حداقل 32GB است.

هر دو نوع نصب به حدود 100GB فضا نیاز دارد. با نصب Vitis آخرین نسخه Vivado یعنی نسخه 2019.2 نیز نصب میشود و نیازی به نصب آن به صورت جداگانه نداریم. برای اطلاعات بیشتر به اینجا مراجعه کنید.

ساخت اولین پروژه با Vitis

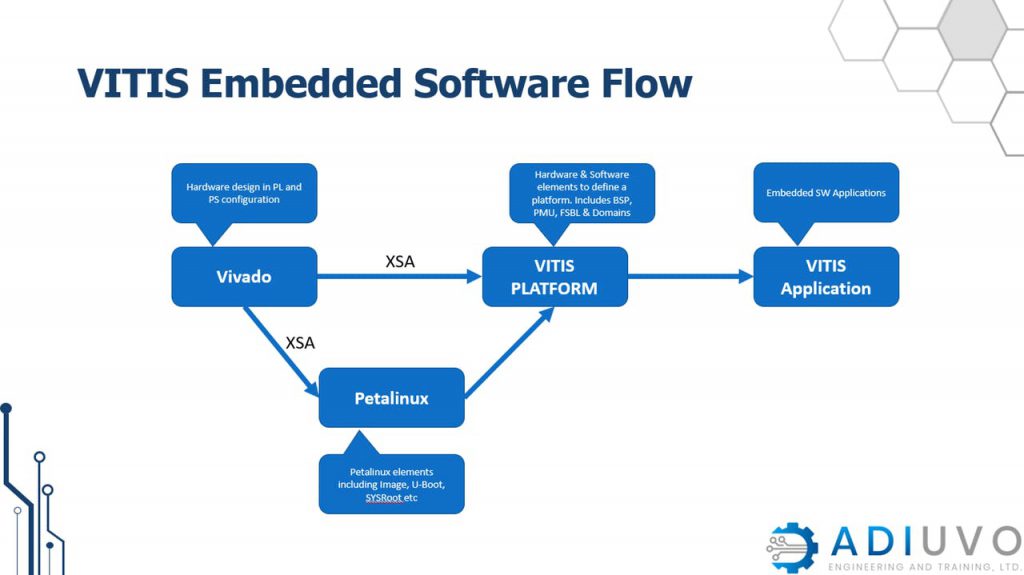

در ادامه قصد داریم با هم، نحوه توسعه یک سیستم نهفته در Vivado و سپس انتقال این پلتفرم به Vitis برای دیباگ و اجرا را بررسی کنیم. بدیهی است بعد از یادگیری کامل این جریان طراحی، میتوانیم کارمان را برای ساخت یک سیستم شتاب دهنده و طراحیهای پیچیده تر نیز گسترش دهیم.

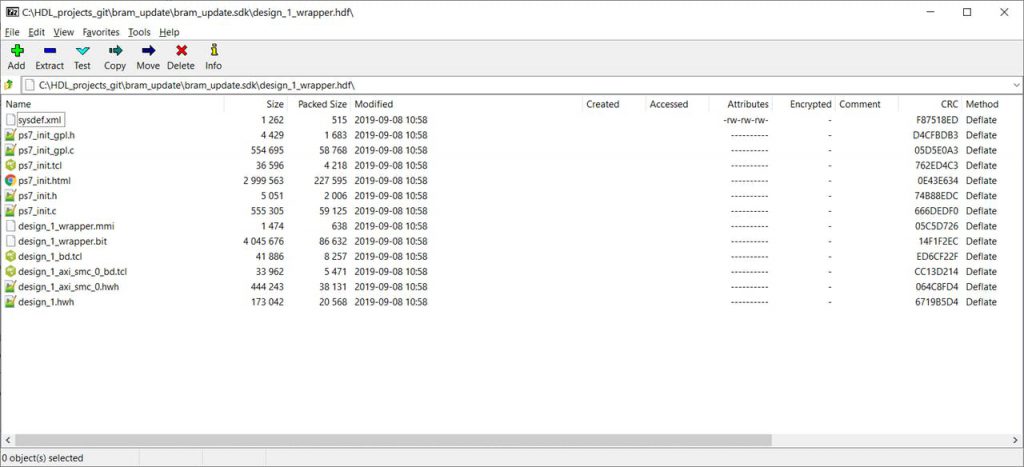

اولین تفاوت قابل توجه که نظر من را به خودش جلب کرد. فایلی بود که در زمان انتخاب گزینه export از Vivado خروجی میگرفتیم. در نسخههای قبلی، فایلی خروجی تحت عنوان Hardware Definition شناخته میشد. در حقیقت، فایل HDF، یک فایل فشرده شده است که حاوی فایل bit و تعاریف و پیکرهبندیهای PS و PL است.

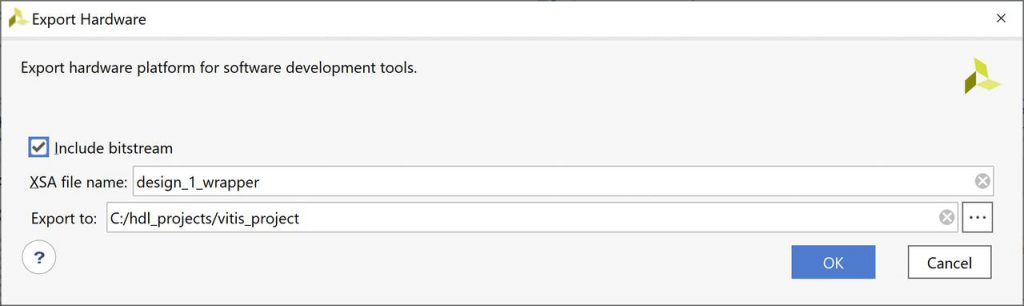

در این نسخه از Vivado فایل دیگری که حاوی کل معماری است، خروجی میشود. فایل جدید یک فایل با فرمت XSA است که مخفف Xilinx Shell Architecture است. ما از این فایل برای ساخت پلتفرم در Vitis و همینطور ساخت لینوکس نهفته در Petalinux استفاده میکنیم.

نحوه خروجی گرفتن از فایل ساخته شده در Vivado با گذشته تفاوت چندانی نکرده است و کافی است از منوی مربوطه گزینه Export Hardware انتخاب شود. برای این مثال من از بورد Ultra96 V2 استفاده کردم. در حالی که فقط PS پیکرهبندی شده و PL کاملاً خالی است.

مشابه فایل HDF، فایل XSA نیز یک فایل فشرده شده است که اطلاعات مورد نیاز برای پیکرهبندی سخت افزاری سیستم را در خود ذخیره کرده است.

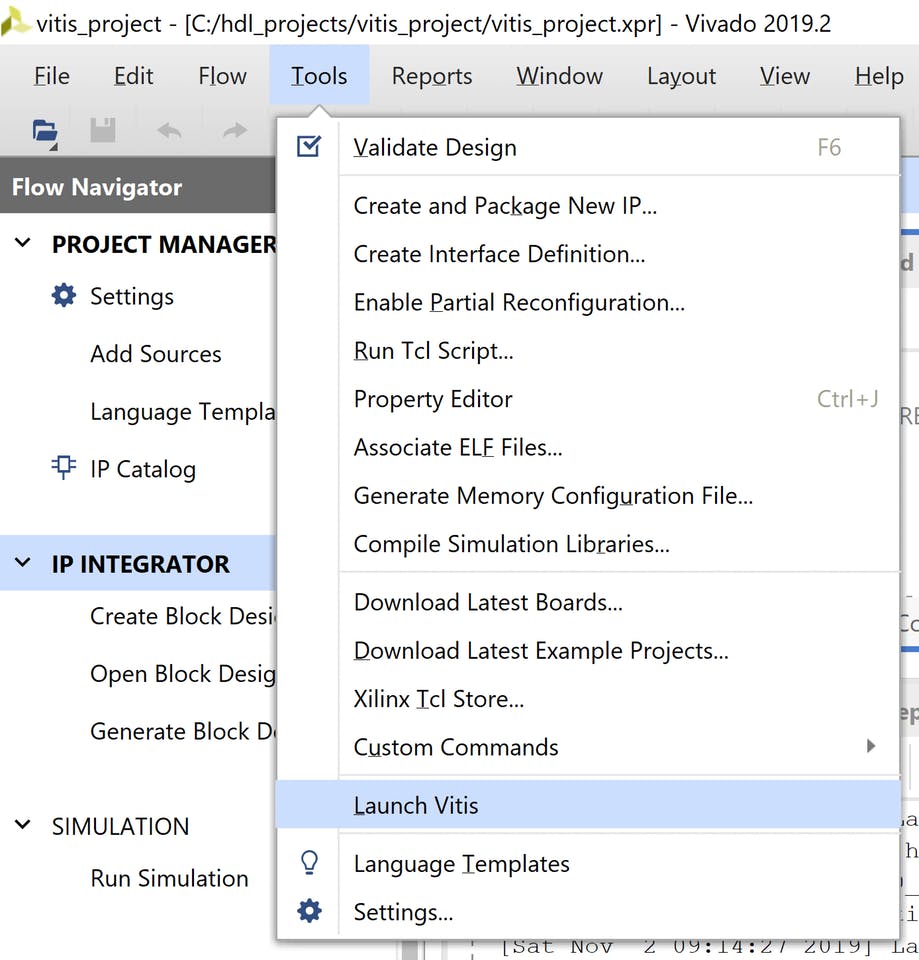

همچون قبل که SDK از داخل Vivado قابل فراخوانی بود. اینجا هم بعد از Export کردن XSA، ما میتوانیم Vitis را از درون Vivado اجرا کنیم. کافی است به منوی tools مراجعه کنیم و گزینه Launch Vitis را مشابه شکل زیر انتخاب کنیم.

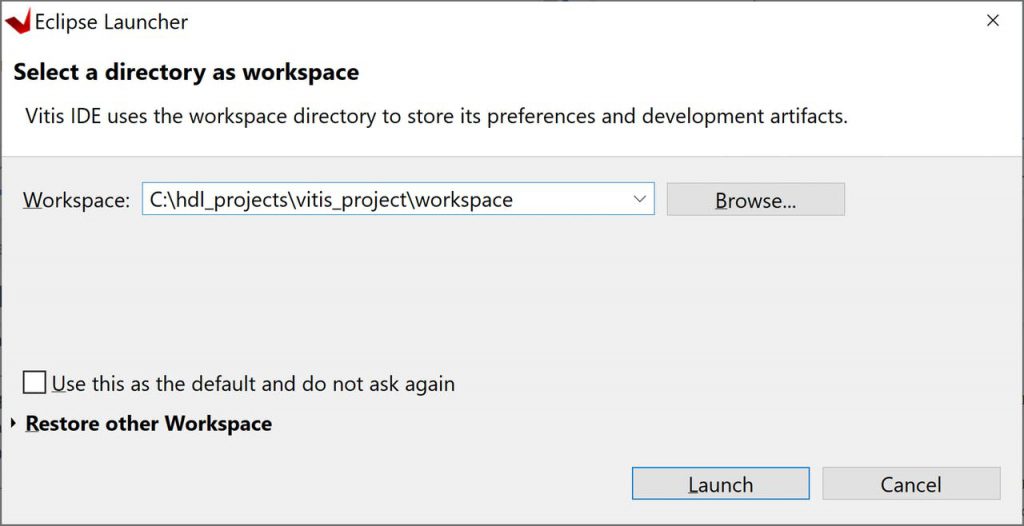

به محض فراخوانی Vitis از کاربر درخواست میشود تا یک workspace انتخاب کند.

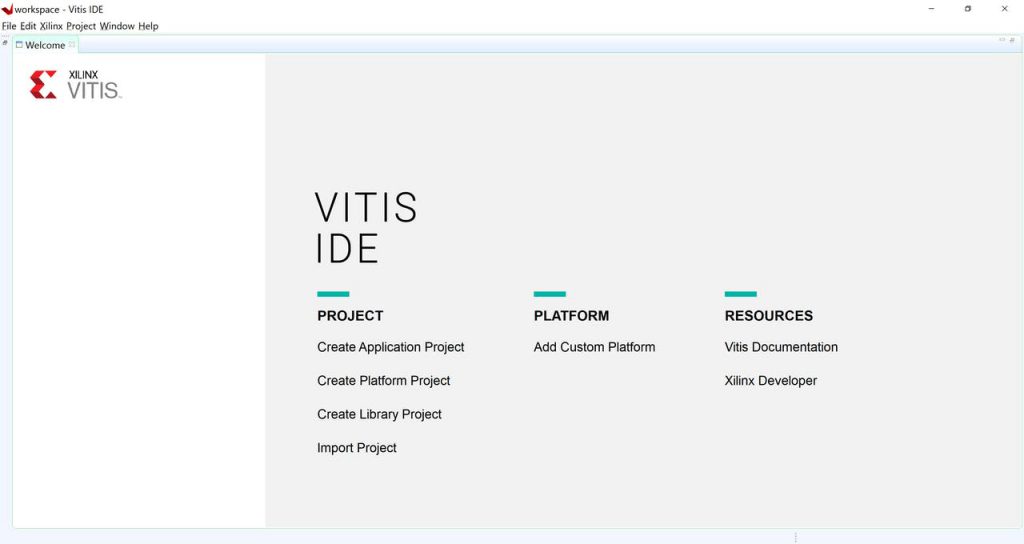

بعد از انتخاب workspace ، محیط گرافیکی خوشامد گویی Vitis نمایش داده میشود و به ما اجازه میدهد که یک application project یا platform project ایجاد کنیم.

دقیقاً اختلاف و وجه تمایز Vitis با SDK در اینجا مشخص میشود. در واقع Vitis جریان توسعه را به دو عنصر تقسیم میکند. یک پلتفرم (platform) که متشکل است از Hardware Definition، BSP ، Domain و یک اپلیکیشن (application).

این یعنی اپلیکشن به سادگی و به سرعت میتواند به یک پلتفرم دیگر منتقل شود. در اینجا ما فقط یک اپلیکشن ساده baremetal رو با هم تست میکنیم. اولین کاری که باید بکنیم ساخت یک پلتفرم است.

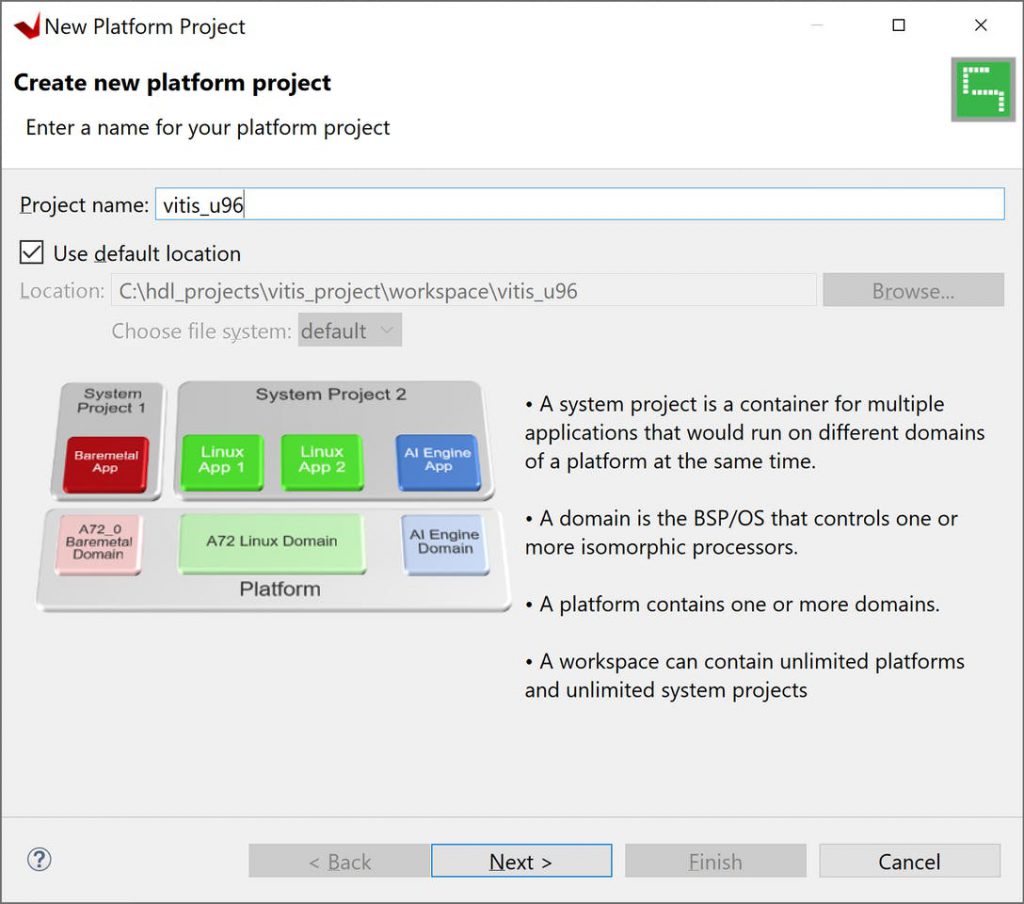

پس روی گزینه Create Platform Project کلیک میکنیم تا ویزاردی مشابه شکل زیر نمایش داده شود.

در این مرحله با دو روش برای تولید پلتفرم روبرو میشویم.

- فایل XSA ساخته شده در Viavdo را لود کنیم.

- و یا از یکی از پلتفرمهای آماده استفاده کنیم.

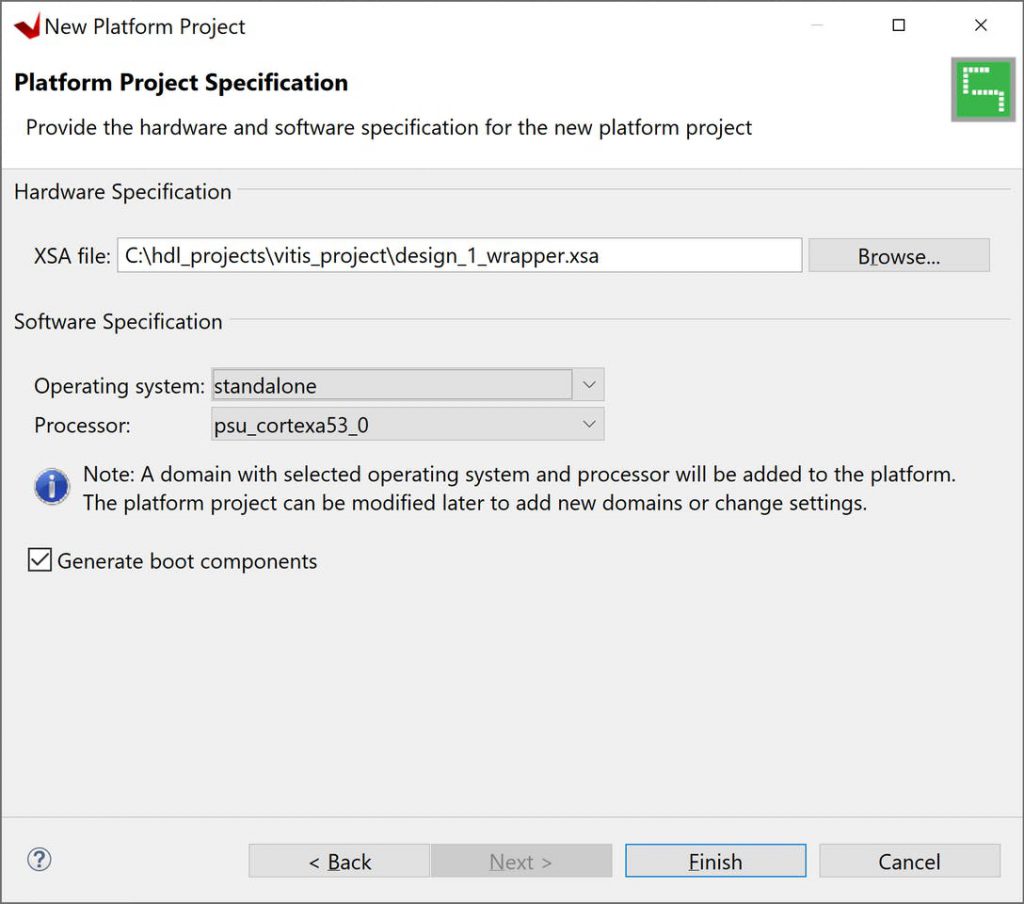

در این پروژه ما فایل XSA را که در پروژه Vivado ساختهایم، لود میکنیم و از پلتفرم خودمان استفاده میکنیم. در ادامه با انتخابهایی به صورت شکل زیر روبرو میشویم.

به صورت پیش فرض کامپوننتهای بوت مورد نیاز همچون FSBL و PMU با توجه به MPSoC انتخابی نیز ساخته میشوند.

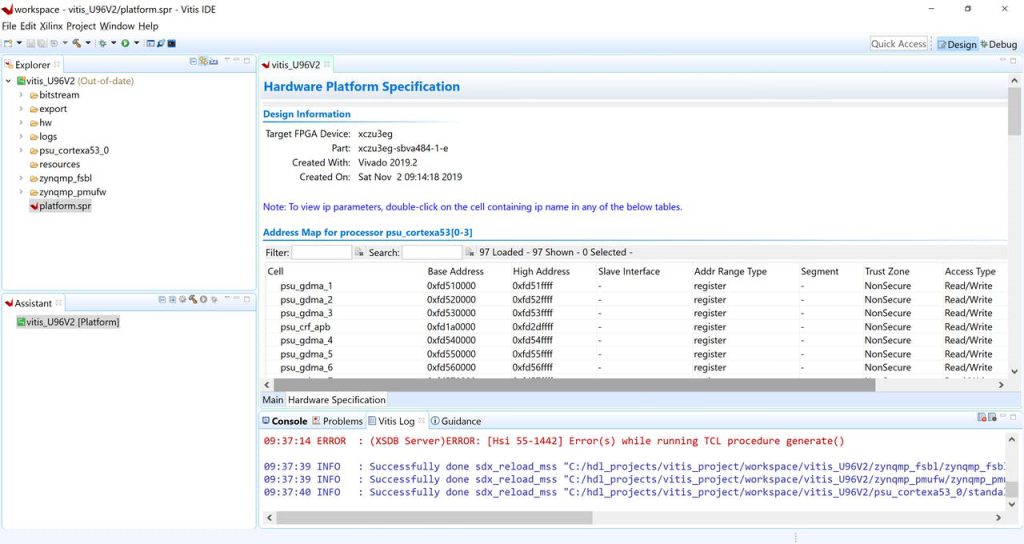

به این ترتیب ما یک پلتفرم Vitis برای فایل XSA خودمان تولید کردیم. همانطور که مشاهده میکنید برای طرح ما FSBL ،PMU و BSP به صورت اتوماتیک تولید شده است. در این مثال ما stdio را از PS_UART_0 به PS_UART_1 تغییر میدهیم چون بورد مورد استفاده ما ULTRA96 است.

برای این کار لازم است BSP را انتخاب کنیم و سپس تنظیمات BSP را ویرایش کنیم. توجه داشته باشیم که این کار را برای FSBL و PMU نیز باید تکرار کنیم تا امکان مشاهده خروجی پورت سریال فراهم شود.

بعد از تغییر تنظیمات BSP، در صورت تمایل به مشاهده جزئیات مربوط به Hardware Definition در برگه Hardware Specification در پایین صفحه پلتفرم کلیک کنید.

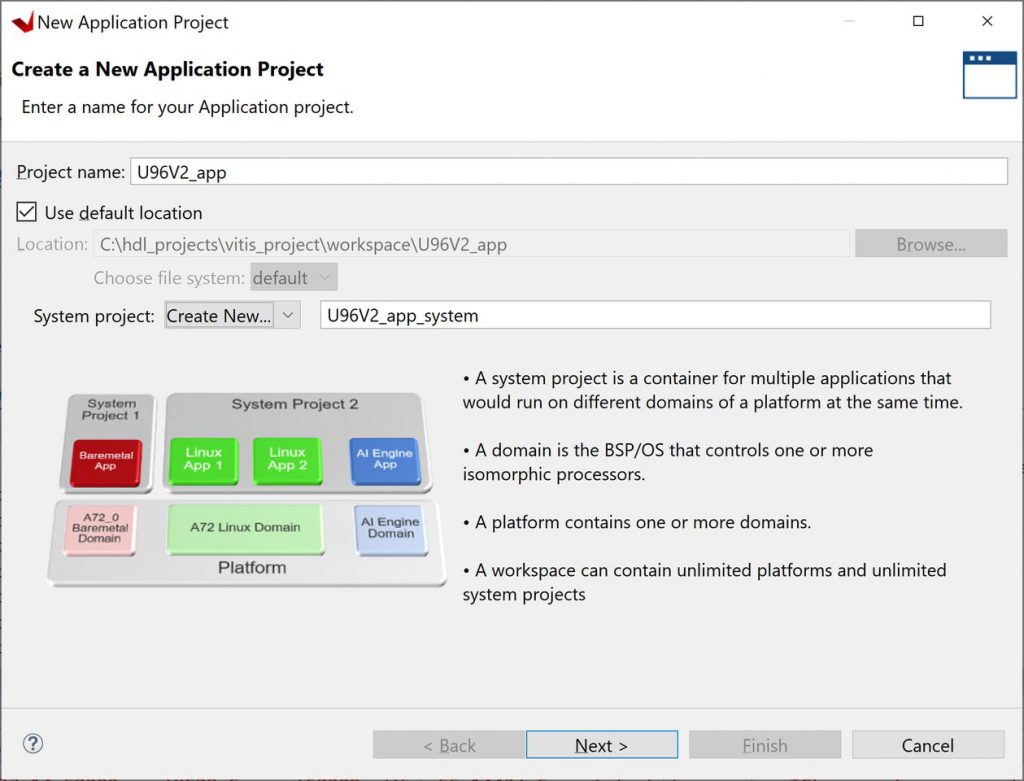

با آماده شدن پلتفرم اکنون آماده ساخت اولین اپلیکیشن نرم افزاری هستیم. برای این کار، گزینه new application از منوی فایل را انتخاب میکنیم. توجه کنیم که ما هنوز system project نداریم و در اینجا یک application project میسازیم.

یک system project در برگیرنده چندین application project است که همگی روی یک پلتفرم به صورت همزمان قابل اجرا هستند. مثلا اپلیکیشنهایی رو در نظر بگیرید که به صورت مجزا روی هستههای A53 یا R5 اجرا میشوند.

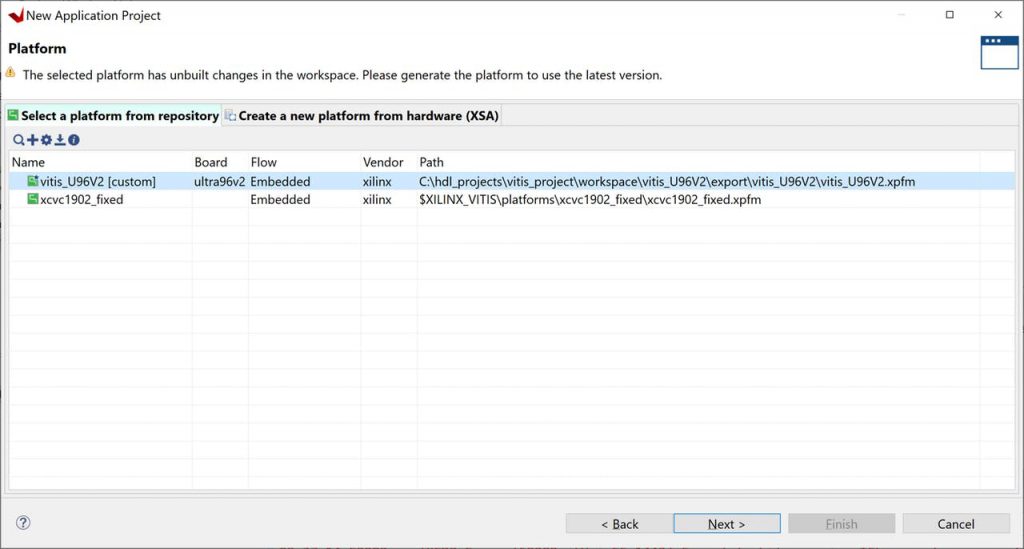

بعد از انتخاب نام مناسب برای application project ، باید پلتفرم را انتخاب کنیم. همانطور که در شکل زیر میبینید، نام پلتفرم Ultra 96 که با هم ساختیم در لیست انتخابها قابل مشاهده است. این پلتفرم را انتخاب میکنیم.

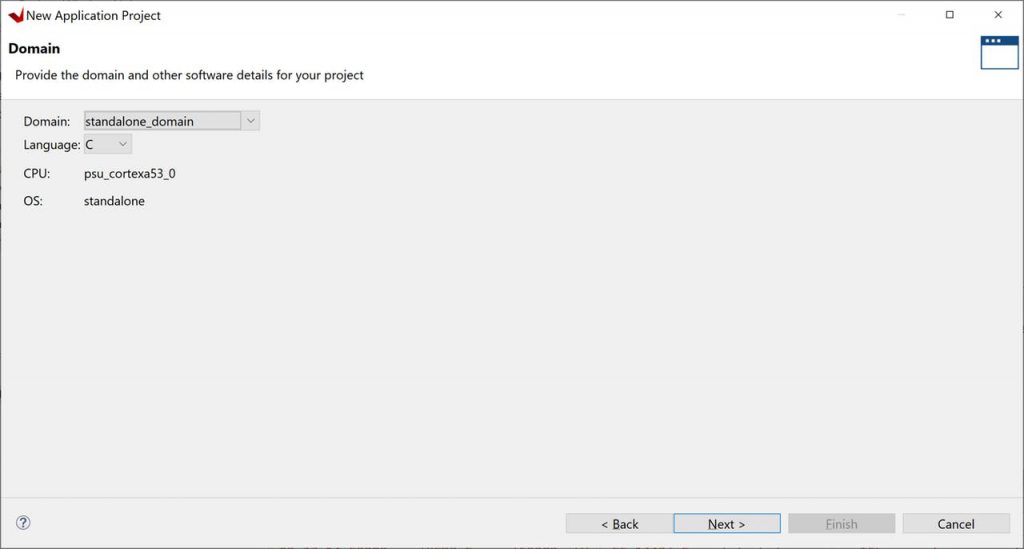

با انتخاب پلتفرم نوبت به انتخاب domain و language میرسد، به صورت پیش فرض گزینه standalone_domin و زبان برنامه نویسی C را انتخاب میکنیم.

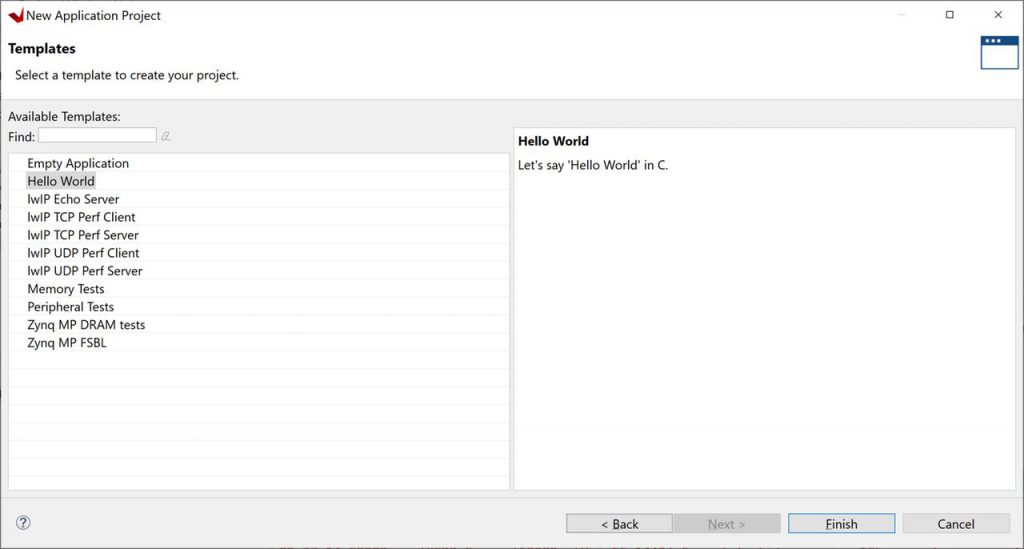

بعد از انتخاب domain و language ، در ادامه از ما خواسته میشود تا از بین اپلیکیشنهای موجود در صورت تمایل یکی را انتخاب کنیم. در این پروژه ما گزینه Hello World را انتخاب میکنیم.

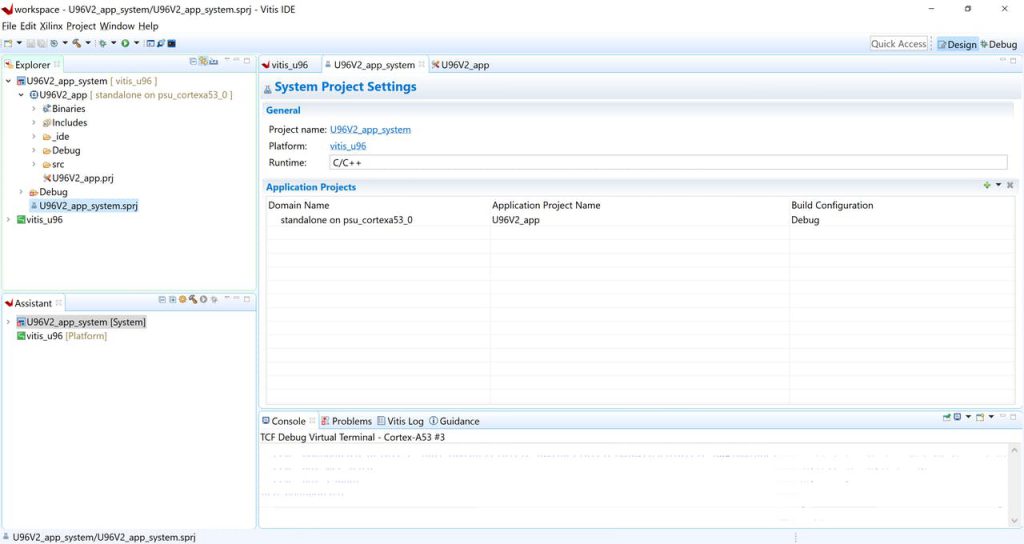

در انتهای کار شما هر دو پروژهای را که تحت عنوان application project و system project ساختهاید، در پنجره Explorer مشاهده میکنید.

در بخش system project ، شما قادرید application project را که تصمیم داریم روی هسته اول از APU اجرا کنیم، مشاهده کنید.

بعد از Build کردن این پروژه به سادگی میتوان با دانلود فایل ELF خروجی نتیجه کار را روی بورد Ultra96 مشاهده کرد.

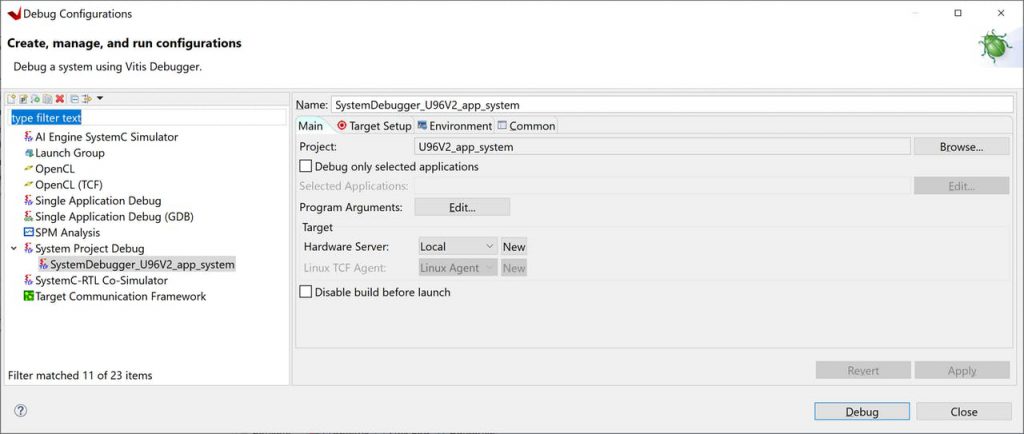

برای انجام این کار کافیست، گزینه Debug Configuration Options انتخاب کنیم. دقیقا مشابه کاری که قبلا در محیط SDK انجام میدادیم. به این ترتیب لیست تنظیمات و گزینههای مختلف برای ما نمایش داده میشود.

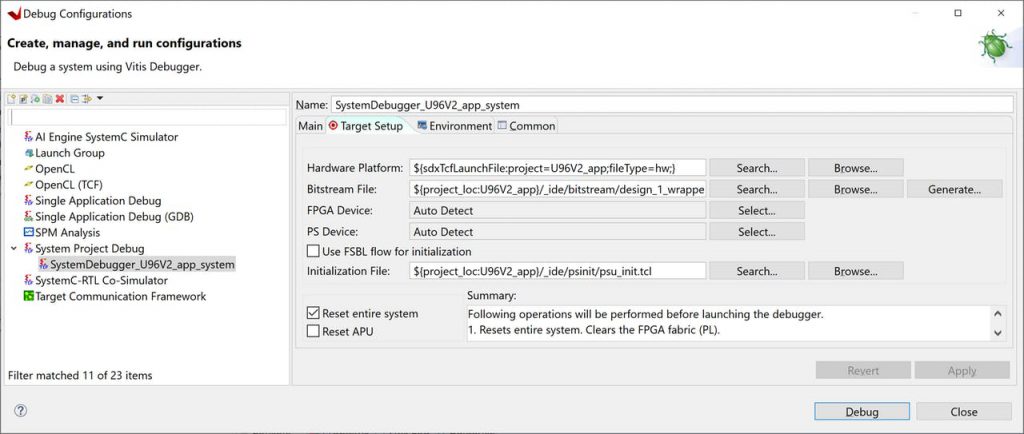

برای این مثال، با وجود اینکه امکان دیباگ ساده به صورت یک application تنها وجود دارد، گزینه دیگری را انتخاب میکنم و کار را با انتخاب System Project Debugger ادامه میدهم.

این کار باعث میشود تا دیباگ کل سیستم در صورت اجرای همزمان چندین اپلیکیشن برای ما امکان پذیر باشد. تنها تغییری که در این بخش روی تنظیمات پیش فرض انجام میدهیم غیر فعال کردن گزینه استفاده از FSBL در زمان راه اندازی اولیه است.

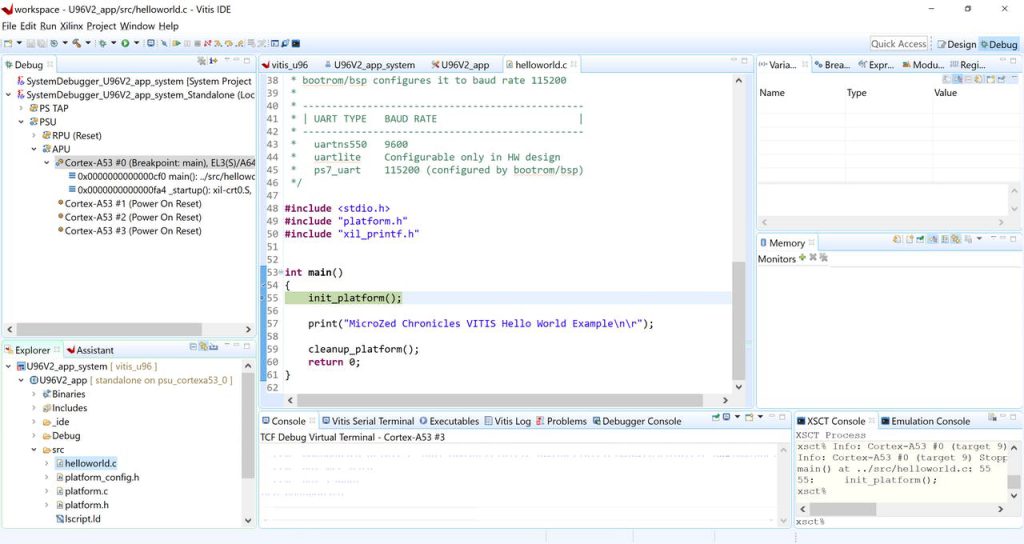

روی گزینه Debug کلیک میکنیم و دانلود اپلیکیشن آغاز میشود. بلافاصله Debug Perspective فعال میشود و ابزار آماده اجرای اپلیکیشن میشود.

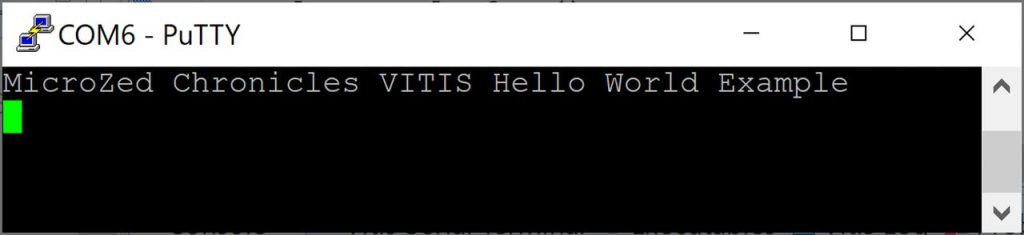

با اجرای برنامه پیغامی مشابه شکل زیر را در پنجره ترمینال به شما نمایش داده میشود.

این تازه شروع کار بود، امیدوارم برای پروژههای پیچیدهتر و بررسی سایر جنبههای vitis همچنان با ما همراه باشید.

منبع: hackster.io نوشته Adam Taylor