مقدمه

طراحی کلاک یکی از اساسی ترین جنبهها در طراحیهای مبتنی بر FPGA و به طور کلی کلیه سیستمهای منطقی قابلپیکرهبندی است. اگر اشتباه کنیم با مشکلات زیادی روبرو میشویم. در این حالت، طرح نهایی ما ممکن است در برآورده کردن الزامات زمانبندی با مشکل روبرو شود. شرایط ممکن است بدتر از این نیز باشد. عدم رعایت دستورالعملهای طراحی همچون نحوه جانمایی پینها و یا نحوه توزیع و استفاده از کلاک منجربه به چالشی جدی در پیادهسازی طرح میشود. برای کسب اطلاعات دقیق در این زمینه سری مقالات آموزشی مدیریت سیگنال کلاک را مطالعه بفرمایید.

البته کار همینجا تمام نمیشود. ممکن است نیاز داشته باشیم به جنبههای بسیار پیچیدهتر طراحی نیز توجه کنیم، مواردی که در آن طرح ما داری چندین حوزه کلاک متفاوت است. در این آموزش از پایگاه دانش هگزالینکس قصد داریم شما را با یک قابلیت ویژه در تراشههای FPGA آشنا کنیم. این قابلیت به لطف Clock Wizard IP در محیط توسعه Vivado برای ما محقق شده است. این قابلیت تحت عنوان مانیتور کردن کلاک یا clock monitoring شناخته میشود و میتواند در موقع لزوم عصای دست طراح باشد. اگر به این موضوع علاقمند هستید پس تا انتها با ما همراه باشید.

مانیتور کردن کلاک

خیلی عجله نکنید، حتی بعد از دستیابی به زمانبندی مطلوب و برآورده شدن الزامات طراحی و همینطور حصول اطمینان از انتقال مناسب کلاک بین نواحی مختلف کلاک، بازهم برای به آرامش رسیدن کمی زود است. در برخی از کاربردهای خاص که به لحاظ نوع ماموریت نیاز به قابلیت اطمینان و کنترل پذیری بسیار بالا دارند، لازم است از صحت عملکرد کلاک در زمان اجرا نیز اطمینان حاصل شود. یعنی برای جلوگیری از بروز هرگونه نقصان در عملکرد سیستم مجبوریم نوعی فرایند تست و بازبینی دائمی روی طرح در نظر بگیریم. پیادهسازی چنین فرایندی به یک راه حل نسبتاً نام آشنا به نام built in self test – BIST منجر میشود. با این رویکرد BIST به عنوان بخشی از طرح اصلی در نظر گرفته میشود.

اینجا دقیقا همان جایی است که قابلیت مانیتور کردن کلاک درون Clock Wizard IP Core، به کار ما میآید. با استفاده از قابلیت مانیتور کردن کلاک، ما قادر هستیم بررسی کنیم که آیا:

- کلاک مد نظر ما در سیستم متوقف شده است یا نه؟

- کلاک مد نظر ما در سیستم glitch دارد یا نه؟

- فرکانس کلاکهای مد نظر ما در سیستم از رنج مجاز تغییرات خارج میشود یا نه؟

با فعال کردن قابلیت مانیتور کردن کلاک در Clock Wizard ما امکان بررسی و مانیتور حداکثر چهار کلاک را خواهیم داشت. این کلاکها میتوانند

- مستقل باشند و برای تولید یک کلاک خروجی اضافی در Clock Wizard استفاده نشوند

- و یا به عنوان یکی از کلاکهای مورد استفاده در طرح از آنها برای ساخت کلاک دیگری در Clock Wizard استفاده شود.

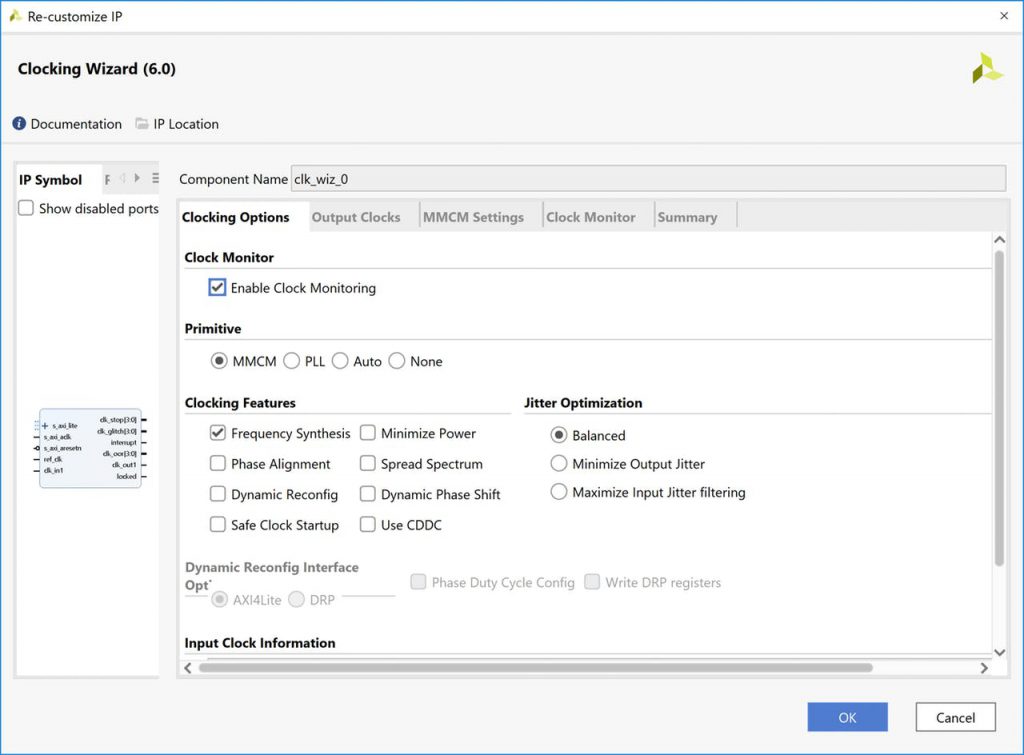

فرایند فعال کردن قابلیت مانیتور کردن کلاک در زمان سفارشی سازی Clock Wizard IP انجام میشود.

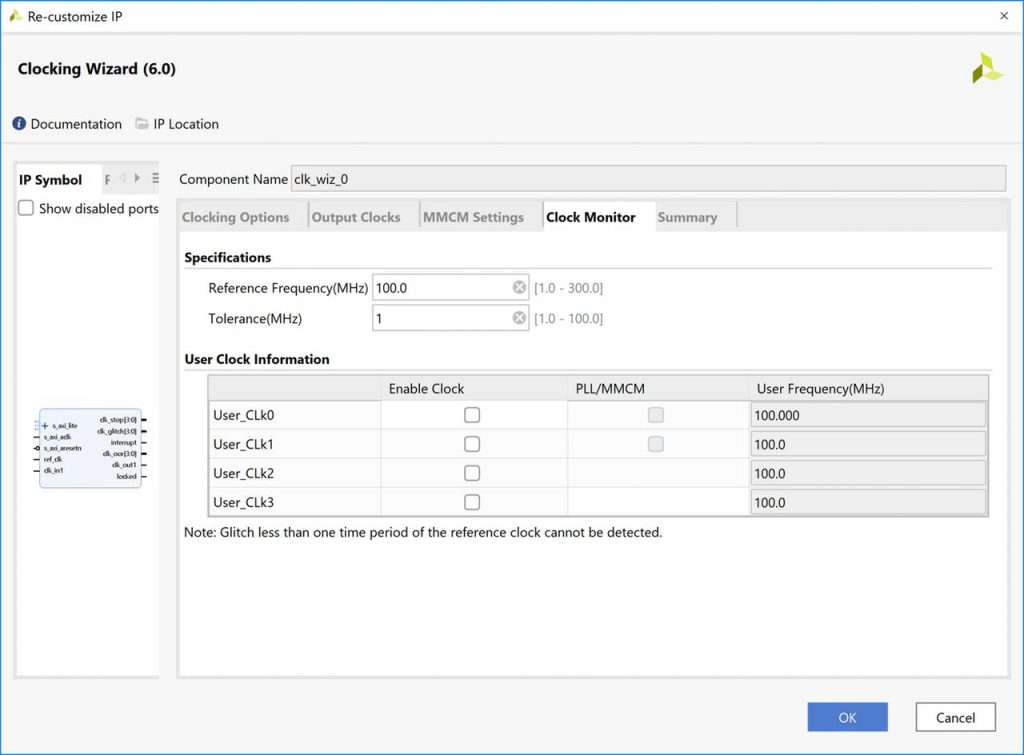

بعد از فعال کردن این گزینه در اولین برگه از صفحه تنظیمات IP، به برگه تنظیمات اصلی مانیتورنیگ کلاک میرویم و تنظیمات زیر را اعمال میکنیم.

- تعداد کلاکهایی که قصد داریم مانیتور کنیم.

- فرکانس کلاک مرجع

- و تلورانس کلاک

در واقع کلاک مرجع برای مانیتور کردن چهار کلاک دیگر به کار میرود و فرض بر این است که کلاک مرجع کاملا پایدار و بدون خطا است.

حتما به این نکته توجه داشته باشید که اگر تمایل به استفاده از یکی از کلاکهای مانیتور شده برای تولید کلاک جدیدی دارید، باید از پورتهای clk_0 و یا clk_1 استفاده کنید. همینطور گزینه PLL/MMCM نیز باید در ستون دوم انتخاب شود.

علاوه بر موارد فوق Clock Wizard شامل تعدادی خروجی گسسته نیز میباشد. از این خروجیهای گسسته برای افزایش خود کنترلی و تغیین آستانه هوشمندی سیستم، در زمان بروز خطا روی کلاک مانیتور شده استفاده میشود.

این خروجیهای گسسته برای مشخص کردن:

- کلاک متوقف شده (Clock_Stop)

- وجود پالسهای اضافی روی کلاک (Clock_Glitch)

- و یا افزایش غیر مجاز تلورانس کلاک (Clock_OutOfTolerance) مورد استفاده قرار میگیرند.

هر کدام از این خروجیها دارای ۴ بیت است. هر بیت متناسب با یکی از کلاکهای مانتیور شده است و در صورت بروز خطا فعال میشوند.

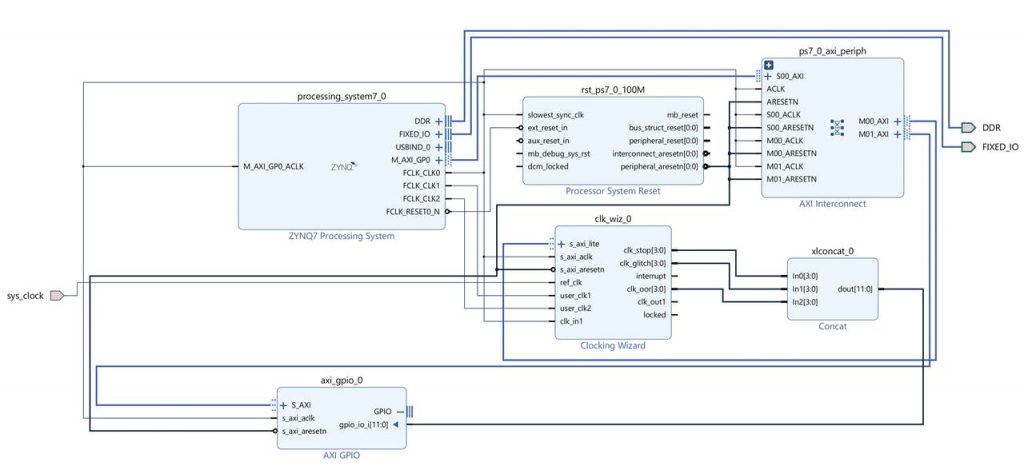

زمانی که قابلیت مانیتور کردن کلاک فعال باشد، به صورت اتوماتیک ماژول Clock Wizard یک اینترفیس AXI Lite را فراخوانی میکند. این اینترفیس به پردازنده یا سایر اینترفیسهای AXI Master امکان مانیتور کردن وضعیت کلاک را با استفاده از سایر اینترفیسهای AXI فراهم میآورد.

برای کمک به طراحی یک سیستم مطمئن و کاملا واکنش گرا، امکان فعال سازی وقفه نیز وجود دارد. این قابلیت اضافی با استفاده از اینترفیس AXI فعال میشود. نحوه پیکرهبندی به این صورت است که با استفاده از یک اینترفیس AXI به IP میگوییم در زمان بروز رخداد خطا، یک وقفه تولید کند.

جمع بندی

توانایی در مانیتور کردن کلاکها در سیستم یک مزیت بسیار کاربردی است. این قابلیت به طراح اجازه میدهد تا از در دسترس بودن کلاکهای خارجی پیش از استفاده درون سیستم اطمینان حاصل کند. یک مثال خوب در این رابطه حالتی است که در آن مجبوریم بنابر شرایط خاص طراحی بین دو یا چند کلاک ورودی انتخاب انجام دهیم.

منبع: hackster.io نوشته Adam Taylor