مقدمه

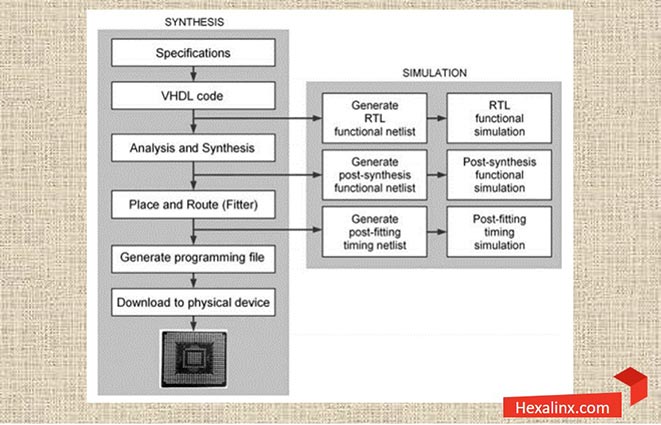

آشنایی با جریان طراحی در FPGA اولین درسی که در دورههای مقدماتی FPGA ارائه میشود. در این مطلب کوتاه از پایگاه دانش هگزالینکس قصد داریم شما را با گامهای مورد نیاز برای یک طراحی خوب در FPGA آشنا کنیم. در ادامه فهرستی از گامهای مورد نیاز برای اجرای صفر تا صد یک پروژه روی FPGA توضیح داده میشود. پس تا انتها با ما همراه باشید.

گامهای طراحی

گام اول

گام اول طراحی دیجیتال عملکرد مورد انتظار سیستم توسط مهندس طراح است. برای طراحی مناسب دو دسته اطلاعات نیاز داریم.

- دانشهای آکادمیک طراحی دیجیتال و

- شناخت کافی از معماری و قابلیتهای تراشه هدف

علاوه بر این الزامات پروژه و محدودیت های آن نیز باید در نظر گرفته شود. در عمل این گام مهمترین گام طراحی است در حالی کمتر به آن توجه میشود.

گام دوم

گام دوم کد نویسی به زبان VHDL و یا Verilog است. در این گام طراح علاوه بر تسلط به زبان توصیف سخت افزاری باید با اصول استفاده از IPCore ها، نحوه به اشتراک گذاری منابع، نحوه فراخوانی عناصر پایه موجود در تراشه نظیر بلوکهای ضرب کننده و بافرهای کلاک و غیره آشنا باشد. وجه تمایز یک برنامه نویس خوب با برنامه نویس معمولی دقیقا در این گام نمایان می شود. این گام عملا دومین گام مهم در طراحی است.

گام سوم

گام سوم به کدنویسی و طراحی testbench اختصاص دارد. در طراحیهای دیجیتال پیچیده، طراحی testbench به اندازه طراحی خود سیستم پرچالش و مهم است. به صورت پیش فرض به محض اینکه حرف از تست مدار به میان میآید، فکر میکنیم وظیفه ما اثبات عملکرد صحیح مدار است. در حالی که این باور کاملا اشتباه است. در حقیقت ما با نوشتن testbench و انجام شبیه سازیهای سخت گیرانه به دنبال پیدا کردن خطاهای احتمالی سیستم هستیم و تنها زمانی میتوانیم از صحت کارکرد سیستم اطمینان حاصل کنیم که هیچ خطایی پیدا نکنیم. فراموش نکنیم، توانمندی در نوشتن testbench خوب یک هنر است. این قضیه به حدی مهم است که زبانهایی همچون System Verilog و System C به طور اختصاصی برای این منظور توسعه داده شدهاند.

در طراحیهای دیجیتال پیچیده، طراحی testbench به اندازه طراحی خود سیستم پرچالش و مهم است

گام چهارم

گام چهارم کامپایل یا سنتز کدها توسط ابزار سنتز است. خروجی این مرحله نتلیست سنتز نام دارد و توصیفی از منابع مورد نیاز برای پیادهسازی سیستم روی تراشه را تولید میکند. به صورت پیش فرض طراح هیچ نقشی در این گام ایفا نمی کند، مگر اینکه نیاز باشد با اعمال یکسری تنظیمات روی ابزار سنتز عملکرد آن را سفارشی کند. اعمال این تنظیمات غالبا نیاز به تسلط مهندس طراح به ابزار سنتز مورد استفاده دارد. طراح برای مسلط شدن به این تنظیمات نیازمند اجرای پروژههای عملی متعدد و صرف زمان کافی است.

گام پنجم

گام پنجم بازهم به شبیهسازی کارکرد مدار اختصاص دارد ولی تقریبا هیچ گاه توسط مهندسان طراح در یک پروژه عملی اجرا نمیشود. این گام بیشتر در پروژههای آکادمیک و دانشگاهی جهت شبیه سازی عملکرد سیستم بعد از سنتز اجرا میشود. به صورت کلی بعد از سنتز با اعمال تاخیر ذاتی گیتها و ریست اولیه به سیستم رفتار طرح تا حدودی دستخوش تغییر میشود. از این رو نتایج شبیهسازی در این گام تا حدودی با نتایج بدست آمده در گام سوم متفاوت است.

گام ششم

گام ششم پیادهسازی طرح توسط ابزارهای پیادهسازی است، ابزارهای پیادهسازی منحصرا توسط شرکتهای سازنده FPGA تولید میشوند. این ابزارها با توجه به تکنولوژی ساخت تراشه و یکسری الگوریتم هوشمند اقدام به پیادهسازی مدارات دیجیتال روی تراشه هدف میکنند. فرایند پیاده سازی در سه فاز انجام میشود.

- در فاز اول نت لیستهای تولید شده در گام چهارم در قالب یک نت لیست واحد با هم ترکیب میشوند.

- سپس در فاز دوم عمل نگاشت این نت لیست به منابع داخل تراشه انجام میشود و

- در فاز سوم جانمایی مناسب منابع روی تراشه و مسیریابی بین آنها انجام میشود.

همچون مرحله سنتز هر سه فاز پیادهسازی به صورت اتوماتیک توسط ابزار پیادهسازی اجرا میشود. البته یک تفاوت بسیار مهم وجود دارد. پیادهسازی مدارات روی تراشه با توجه به یکسری استراتژی صورت می پذیرد، که جزئیات این استراتژیها توسط طراح قابل کنترل است. در اکثر موارد پیادهسازی با تنظیمات پیش فرض با موفقیت همراه است، اما در صورتی که نتایج مطلوب حاصل نشود، کار کمی سخت می شود.

تعیین موقعیت پورت های سیستم روی پین های تراشه نیز در گام ششم انجام می شود.

طراحان حرفهای در گام پیادهسازی با تعریف یکسری قیود ابزار پیادهسازی را به صورت سفارشی راهنمایی میکنند، تا در نهایت بهترین جانمایی و مسیریابی ممکن حاصل شود. دو پارامتر مهم برای سنجش موفقیت یا عدم موفقیت در گام پیاده سازی وجود دارد.

- اولی دستیابی به فرکانس کاری مطلوب و

- دومی به حداقل رساندن منابع مصرفی روی تراشه است.

به طور کلی گستره وسیعی از تنظیمات باید در این گام انجام شود، و طراح باید با دقت عملکرد و کارایی مورد نظرش را برای ابزار توصیف کند تا خروجی کار مطلوب باشد، این گام سومین گام مهم در طراحی است.

گام هفتم

در گام هفتم طراح برای سنجش صحت عملکرد سیستم بعد از اتمام فاز جانمایی و مسیریابی، اقدام به شبیه سازی زمانی سیستم میکند. در این شبیه سازی رفتار واقعی سیستم روی تراشه در محیط نرم افزاری بررسی میشود. مثالهای متعددی وجود دارد که در آن با وجود عملکرد صحیح مدار در گام سوم، در این گام پاسخ مطلوب حاصل نمیشود. دلیل آن نیز غالبا زیاد بودن تاخیرهای موجود در سیستم است. بخش قابل ملاحظهای از این تاخیرها به دلیل جانمایی نامناسب و طولانی بودن مسیرهای ارتباطی بین عناصر است. در صورت بروز چنین مشکلی عملا کل طرح زیر سوال میرود و لازم است یک بازنگری کامل روی مسیرهای بحرانی و گلوگاههای طراحی صورت بپذیرد.

گام هفتم اغلب توسط طراحان با تجربه که تا حدود زیادی به صحت عملکرد سیستم اطمینان دارند، اجرا نمیشود، دلیل اصلی آن نیز کند بودن بیش از حد پروسه شبیه سازی زمانی است، برای مدارهای با پیچیدگی متوسط ممکن است این شبیه سازی یک روز کامل زمان نیاز داشته باشد.

گام هشتم

گام هشتم به تولید بیت فایل خروجی و پیکرهبندی تراشه FPGA اختصاص دارد. تنظیماتی که طراح در این بخش انجام میدهد نسبتا محدود است و غالبا در ارتباط با فرمت فایل پیکرهبندی خروجی است. در این گام کاربر با توجه به نوع تراشه FPGA فرمت فایل خروجی را انتخاب و به صورت اتوماتیک با چند کلیکُ فایل را روی تراشه پیکرهبندی یا در اصطلاح دانلود می کند.

از آنجایی که تراشههای FPGA دارای حافطه دائمی نیستند معمولا از یک حافظه جانبی برای ذخیزه سازی فایل پیکرهبندی و انتقال آن به FPGA استفاده می شود. از این رو انتظار میرود مهندس طراح فایل مناسب برای حافظههای فلش جانبی را نیز تولید کند.

گام نهم

اگر خوش شانس باشیم و همه فرضیات طراحی را درست اجرا کرده باشیم، نیازی به اجرای گام نهم نداریم. در پروژه های کوچک که تعداد فانکشنهای سیستم محدود است و یک عملکرد نه چندان پیچیده مورد نیاز است، میتوانیم به خوش شانسی خودمان امیدورام باشیم. اما اگر فقط کمی تعداد ورودی خروجی ها و سیگنال های کنترلی سیستم افزایش پیدا کند، بروز خطا کاملا اجتناب ناپذیر می شود. به این ترتیب برای پیدا کردن منشا خطا چاره ای به جز اجرای گام نهم نداریم. در گام نهم طراح با توجه به شناخت خودش از سیستم اقدام به خطایابی سخت افزاری می کند. یعنی با بررسی و مانیتور کردن مدارات پیاده سازی شده روی FPGA به دنبال دلیل بروز خطا میگردد.

موفقیت در این مرحله به معنای اتمام کامل کار طراحی و پیادهسازی یک پروژه است. دو IPCore معروف ILA و VIO به عنوان مهمترین ابزارهای خطایابی Xilinx به شکل گستردهای در این گام مورد استفاده قرار میگیرند.

منبع: Pedroni

1 دیدگاه برای “جریان طراحی در FPGA”

عالی