مقدمه

در بخش اول در رابطه با منابع مدیریت کلاک در تراشههای FPGA صحبت کردیم. در این بخش روی مسیرهای اختصاصی و شبکه توزیع کلاک در FPGA و جزئیات آن تمرکز خواهیم کرد. برای تکمیل شدن بحث قبلی برخی از جزئیات را که مجالی برای توضیح بیشتر در رابطه با آنها فراهم نشد، نیز بیان خواهیم کرد.

به جز منابع مدیریت کننده کلاک که غالباً برای تولید سیگنالهای جدید از روی کلاک ورودی به تراشه به کار گرفته میشوند، گروه دیگری از منابع نیز برای توزیع و انتشار مناسب کلاک درون تراشههای FPGA وجود دارد که عملاً ساختار درخت کلاک درون تراشه را شکل میدهند.

در ابتدای کار قرار نبود مقاله مدیریت سیگنال کلاک در دو بخش منتشر شود، اما با شروع کار نگارش به یکباره همه چیز تغییر کرد. تا پیش از اینکه قلم و کاغذ را در دست بگیریم و شروع به نوشتن کنیم، فکر میکردیم که همه چیز را در ارتباط با شبکه توزیع کلاک و بلوکهای مدیریت کننده کلاک در نسلهای مختلف تراشههای شرکت Xilinx میشناسیم. اما هر چه بیشتر نوشتیم، ابهامات بیشتر شد، متن طولانی تر شد و از انسجام آن کاسته شد. از این رو بعد از انتشار بخش اول این مقاله، تصمیم گرفتیم کمی برای انتشار بخش دوم آن تأمل و دقت بیشتری انجام دهیم و حداقل مواردی را که برای خودمان شفاف نبود، بیشتر بررسی کنیم. این بررسیها در نهایت منجربه به اصلاح برخی از نکات در متن مقاله قبلی شد که شاید کمی نادقیق بیان شده بودند. علاوه بر این به صورت جزیي مطالب بخش اول نیز بروز رسانی شد. روی هم رفته اگر طولانی شدن فاصله زمانی انتشار این دو بخش برای شما هم محسوس بوده است، پیشنهاد میکنیم ابتدا بخش اول را مطالعه کنید و در ادامه برای تکمیل مطلب به این جا برگردید.

کلاکهای محلی و سرتاسری

از نقطه نظر کلاک، بعد از معرفی خانواده Virtex-4، تراشههای FPGA شرکت Xilinx، به تعدادی ناحیه کلاک تقسیم میشوند. این نواحی برای مدیریت بهتر سیگنال کلاک ایجاد شدند و تعداد آنها با توجه به سایز تراشه در نسلهای مختلف، متفاوت است. همینطور شیوه تقسیم بندی فضای درونی هر FPGA به نواحی کلاک طی نسلهای مختلف دستخوش تغییر شده است. معرفی مفهومی به نام ناحیه کلاک باعث شکل گیری مفاهیم دیگری نیز شد که یکی از آنها مفهومی به نام کلاکهای محلی یا Regional Clock است. در حالی که تا پیش از تراشههای Virtex-4 تمامی منابع کلاک درون تراشه، تحت عنوان منابع سرتاسری یا Global شناخته میشدند.

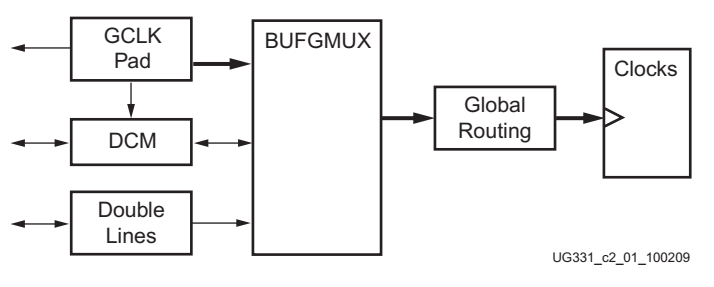

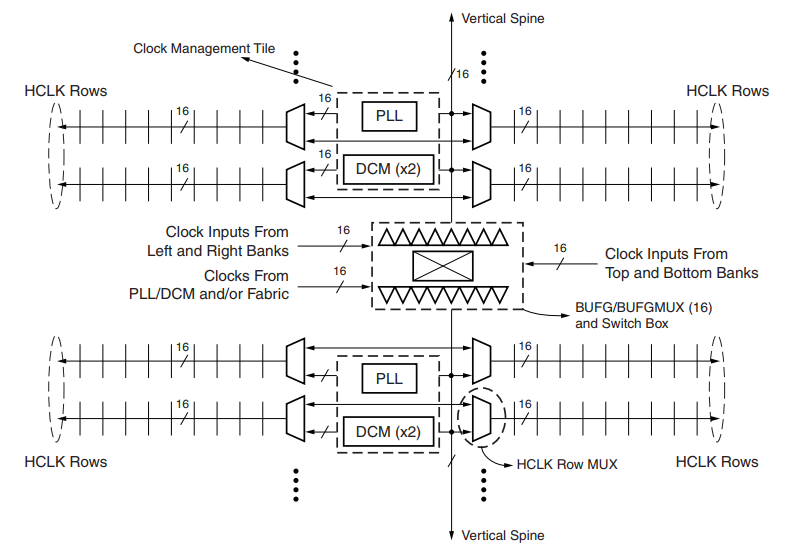

اما پیش از ورود به بحث اصلی و موشکافی موضوع، بد نیست نگاهی به نحوه توزیع کلاک درون تراشههای قدیمی Spartan-3 بیاندازیم. در این تراشهها کلیه منابع کلاک درون تراشه سرتاسری بودند و از سه بخش اصلی تشکیل میشدند، که در شکل زیر نیز نشان داده شده است.

- پینهای اختصاصی و سرتاسری ورودی کلاک تحت عنوان GCLK

- بافرها و مالتی پلکسرهای سرتاسری کلاک تحت عنوان BUFGMAX و

- مسیرهای سرتاسری توزیع کلاک تحت عنوان Global Routing

مسیرهای اصلی کلاک در شکل فوق کمی پررنگ تر کشیده شدهاند، جریان توزیع کلاک از پینهای کلاک سرتاسری (GCLK) شروع میشود و در ادامه به سمت بافرهای کلاک سرتاسری (BUFGMUX) امتداد پیدا میکند و در نهایت از طریق این بافرها و با کمک مسیرهای کلاک سرتاسری به سمت عناصر سنکرون همچون فلیپ فلاپ ها ختم میشود. پینهای GCLK در کنار کارکرد خاصی که داشتند، میتوانستند به عنوان ورودی خروجیهای همه منظوره نیز مورد استفاده قرار بگیرند. بعلاوه اینکه بلوکهای DCM میتوانستند در صورت نیاز بین پینهای ورودی و بافرها قرار بگیرند، نکته جالب اینجاست که در این تراشهها بلوکهای DCM امکان دریافت سیگنال کلاک از سایر منابع همه منظوره درون تراشه را نیز دارا بودند. بافرهای سرتاسری که تعداد آنها ۲۴ عدد بود، نیز میتوانستند در کنار عملیات ساده بافرینگ به عنوان یک مالتی پلکسر وظیفه سوییچ کردن بین دو کلاک را نیز به خوبی ایفا کنند.

در این تراشهها تنها مسیری که از بافرهای سرتاسری به پایه کلاک فلیپ فلاپها منتهی میشد، مسیرهای سرتاسری کلاک بود. هرچند سایر منابع و مسیرهای همه منظوره درون تراشه نیز میتوانستند برای تولید و هدایت کلاک به سمت فلیپ فلاپها مورد استفاده قرار بگیرند، اما این کار به دلیل افزایش چشمگیر جیتر و کجی کلاک روی مسیرهای همه منظوره درون تراشه به هیچ وجه توصیه نمیشد.

شبکه توزیع کلاک

شبکه توزیع کلاک در تراشههای Virtex-4 ، Virtex-5 ، Virtex-6 و حتی Spartan-6 تا حدود زیادی مشابه هم میباشد. در عمل دو نوع شبکه توزیع کلاک در این تراشهها وجود دارد.

- شبکه کلاک سرتاسری که مسیرهایی با تأخیر کم و اختصاصی بین کلاک و سایر منابع درون تراشه ایجاد میکند.

- شبکه کلاک محلی که کلاکهایی بسیار کارآمد و دقیق با حداقل کجی را برای یک یا چند ناحیه کلاک و همینطور منابع ورودی خروجی (IOs) در همان نواحی کلاک فراهم میکند.

اطلاعاتی که در ادامه ارائه میشود مربوط به سه خانواده Virtex-4 ، Virtex-5 ، Virtex-6 و همینطور تراشههای Spartan-6 است، خانوادههای 7Series و UltraScale هم در بخشهای پایانی مقاله به شکل مجزا بررسی میشوند.

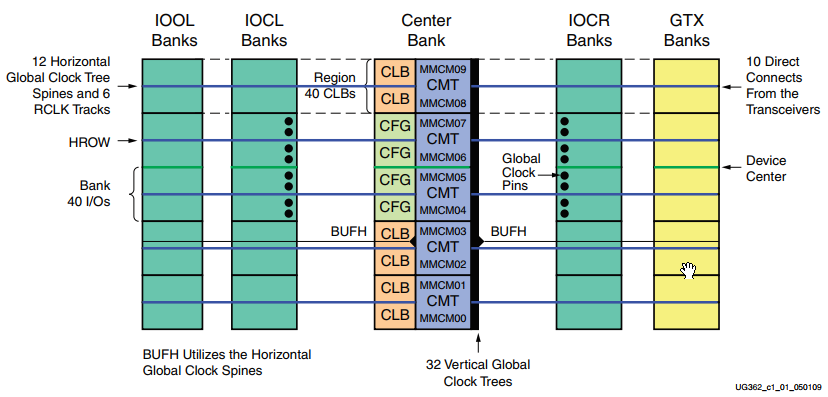

کلاکهای سرتاسری

تمامی تراشههای فوق دارای ۳۲ مسیر کلاک سرتاسری میباشند که به کمک آنها سیگنال کلاک با حداقل کجی، به تمام عناصر سنکرون مثل CLB ها ، block RAM ها و IO ها در سرتاسر قطعه هدایت میشود. حداکثر مسیرهای کلاک قابل استفاده در هر ناحیه در این تراشهها با هم متفاوت است. این بدان معناست که تعداد کلاکهای متفاوت قابل استفاده در یک ناحیه کلاک محدود است، و جزئیات آن به شرح زیر است.

- در تراشههای Virtex-4 ، در هر ناحیه کلاک ۸ مسیر از ۳۲ مسیر سرتاسری میتواند مورد استفاده قرار بگیرد.

- در تراشههای Virtex-5 ، در هر ناحیه کلاک ۱۰ مسیر از ۳۲ مسیر سرتاسری میتواند مورد استفاده قرار بگیرد.

- در تراشههای Virtex-6 ، در هر ناحیه کلاک ۱۲ مسیر از ۳۲ مسیر سرتاسری میتواند مورد استفاده قرار بگیرد.

تنها راه دسترسی به مسیرهای کلاک سرتاسری فقط و تنها فقط از طریق بافرهای سرتاسری میباشد، این بافرهای سرتاسری میتوانند به عنوان مالتی پلکسر کلاک و یا یک مدار کنترلی برای فعال یا غیرفعال کردن مسیرهای کلاک نیز استفاده بشوند. ورودی بافرهای سرتاسری هم عموماً توسط بلوکهای DCM یا MMCM تأمین میشوند.

برای اینکه درک صحیحی از شبکه کلاک و نحوه توزیع کلاک درون تراشه داشته باشید. الزاماً باید با تمامی منابع کلاک آشنایی داشته باشید. در حالت کلی شبکه کلاک سرتاسری از چهار بخش تشکیل میشود:

- پینهای ورودی کلاک سرتاسری

- بافرهای کلاک سرتاسری

- درخت کلاک و شبکه کلاک سرتاسری

- نواحی کلاک، شبکه کلاک محلی

همانطور که در فهرست بالا هم مشاهده میکنید. شبکه کلاک محلی خود به عنوان بخشی از شبکه کلاک سرتاسری در نظر گرفته میشود.

پینهای کلاک سرتاسری (GCLK)

تعداد پینهای کلاک سرتاسری در نسلهای مختلف تراشهها با هم متفاوت میباشد و به شرح زیر است

- تعداد GCLK ها در تراشههای Virtex-4 با توجه به سایز تراشه بین ۱۶ تا ۳۲ میباشد.

- تعداد GCLK ها در تراشههای Virtex-5 باهم برابر است و تمام تراشهها صرف نظر از سایز ۲۰ پین ورودی کلاک سرتاسری دارند.

- تعداد GCLK ها در تراشههای Virtex-6 باهم برابر است و تمام تراشهها صرف نظر از سایز ۸ پین ورودی کلاک سرتاسری دارند.

پینهای کلاک سرتاسری میتوانند به صورت تکی، و تفاضلی مورد استفاده قرار بگیرند. وقتی از این پینها به صورت تکی استفاده شود، الزاماً باید از پایهای که عبارت P در انتهای آن قرار دارد، استفاده شود. پایه N نمیتواند به عنوان ورودی کلاک استفاده شود. در حالت تکی پایه N میتواند به عنوان یک پین ورودی یا خروجی معمولی استفاده شود.

در صورتی که پینهای GCLK به عنوان ورودی کلاک استفاده نشوند، میتوان از آنها به عنوان ورودی خروجیهای همه منظوره استفاده کرد.

بافرهای کلاک سرتاسری

در حالت کلی، تعداد بافرهای کلاک سرتاسری برابر با تعداد مسیرهای کلاک سرتاسری است. یعنی هر سه تراشه Virtex-5 ، Virtex-4 و Virtex-6 همگی دارای ۳۲ بافر کلاک سرتاسری از نوع BUFG هستند. بافرهای سرتاسری کلاک دروازه ورودی مسیرهای سرتاسری کلاک هستند. ورودی این بافرهای میتواند به طرق مختلفی تأمین شود. در ادامه فهرستی از این ورودیها ذکر شده است. البته با توجه به نوع تراشه ممکن است، تفاوتهای کوچکی نیز وجود داشته باشد ولی به طور کلی محدودیت خاصی برای دسترسی به این بافرها وجود ندارد و تقریباً از هر جایی میتوان به آنها دسترسی داشت.

- پینهای ورودی کلاک سرتاسری

- پینهای اختصاصی کلاک در هر ناحیه کلاک البته با در نظر گرفتن یکسری محدودیت

- کلیه عناصر تشکیل دهنده CMT ها

- سایر بافرهای سرتاسری (BUFG)

- اتصالات و اینترکانکتهای مربوط به بخشهای منطقی تراشه

- بافرهای محلی

- و ترنسیورهای پرسرعت (Gigabit Transceivers)

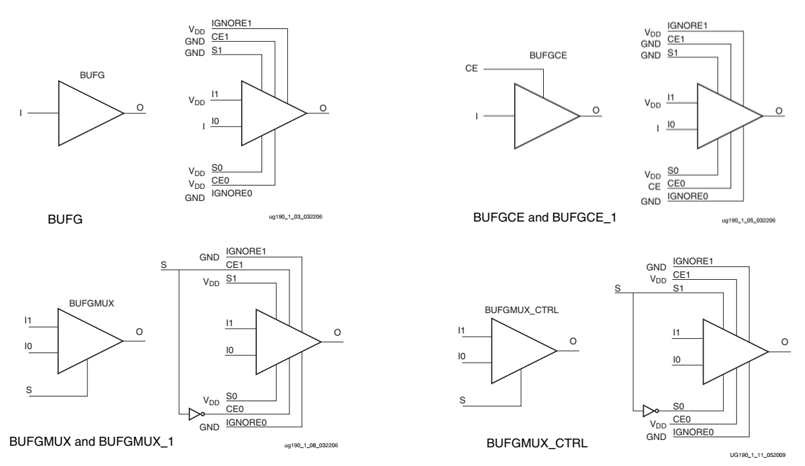

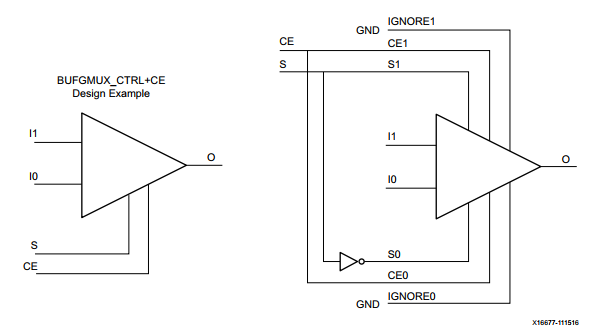

خروجی بافرهای سرتاسری نیز تقریباً در همه جا قابل استفاده است و در تمامی نواحی کلاک قابل دسترسی است. بافرهای سرتاسری به شکلهای مختلفی قابل پیکره بندی هستند در جدول و شکلهای زیر پیکره بندیهای قابل اعمال برای تراشه های Virtex-5 و Virtex-6 ارائه شده است.

کلاکهای محلی

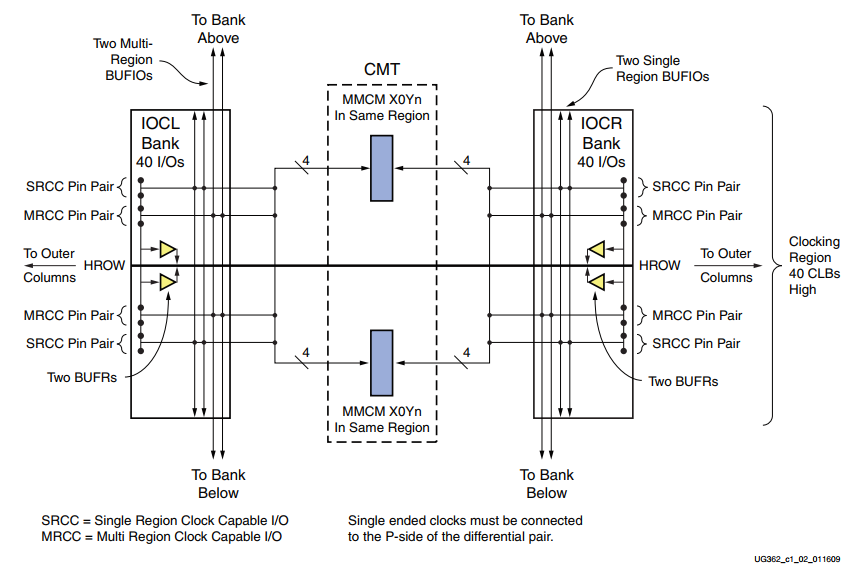

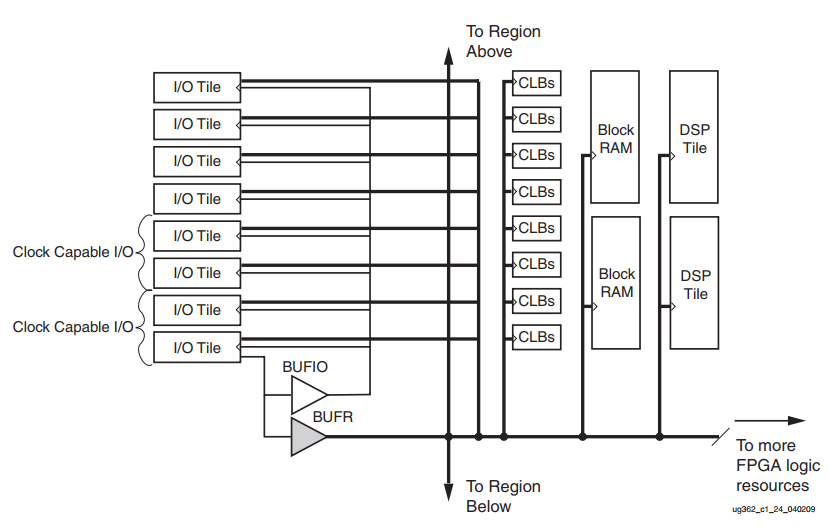

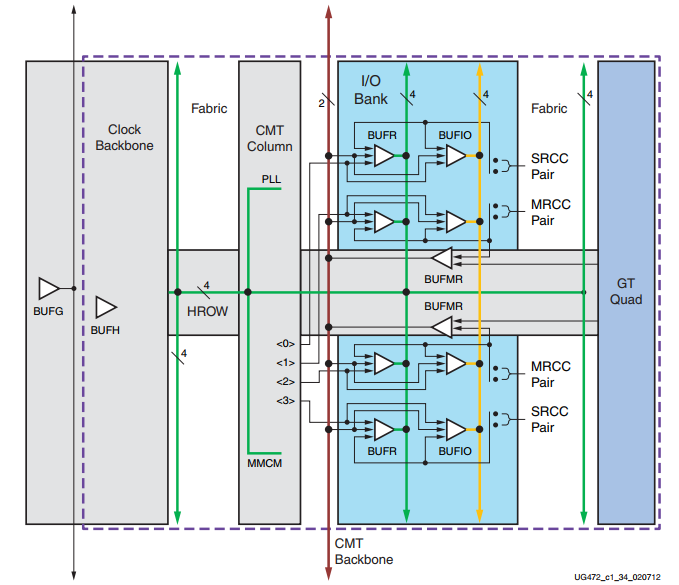

شبکه کلاک محلی، مجموعهای از شبکههای کلاک تفاضلی کوچکِ مستقل از هم و البته مستقل از شبکه کلاک سرتاسری است. برخلاف کلاکهای سرتاسری، گستره تأثیر گذاری سیگنالهای کلاک محلی از طریق بافرهای BUFR محدود به حداکثر سه ناحیه کلاک است. به عنوان مثال در تراشههای Virtex-6 در هر ناحیه دو سیگنال کلاک ورودی/خروجی از طریق BUFIO به صورت اختصاصی برای هر ناحیه و دو سیگنال کلاک ورودی/خروجی اضافی برای تأمین کلاک مورد نیاز نواحی بالایی یا پایینی وجود دارد. این ساختار شبکه کلاک به شکل ویژه برای کاربردهایی که نیاز به اینترفیس source-synchronous دارند، مناسب میباشد.

برای اینکه درک بهتری از شیوه کارکرد کلاکهای محلی داشته باشید، آشنایی با مسیرها و عناصری که به عنوان منابع کلاک محلی شناخته میشوند، حائز اهمیت است. عناصر اصلی سازنده شبکه کلاک محلی در تراشههای Virtex-6 به شرح شکل زیر است.

هر ناحیه کلاک در این تراشهها میتواند حداکثر ۸ بافر کلاک محلی از نوع BUFR و ۶ درخت کلاک محلی داشته باشد. هر ناحیه کلاک هم دقیقاً به اندازه یک بانک IO میباشد. هر بانک چهار پین اختصاصی برای کلاک دارد که این پینها هم به صورت تکی یا تفاضلی قابل پیکره بندی هستند، این ۴ پین میتوانند به عنوان ورودی برای چهار بافر کلاک ورودی/خروجی (BUFIO) و یا چهار بافر کلاک محلی (BUFR) و یا یک CMT در همان بانک یا ناحیه کلاک استفاده شوند.

وقتی از پینهای اختصاصی کلاک به صورت تکی استفاده شود، الزاماً باید از پایهای که با عبارت P در انتهای آن قرار دارد استفاده شود. علاوه بر این بافرهای کلاک محلی (BUFR) میتوانند به عنوان مقسم کلاک نیز عمل کنند و یک نسخه تقسیم بر ۲ تا ۸ شده از کلاک ورودی را خروجی کنند. این ویژگی هنگام استفاده از ویژگی Serializer/Deserializer در IOB ها بکار گرفته میشود. در ادامه با جزئیات بیشتری هر یک از عناصر مختلف تشکیل دهنده شبکه کلاک محلی را بررسی میکنیم.

پینهای کلاک محلی (Clock Capable IO)

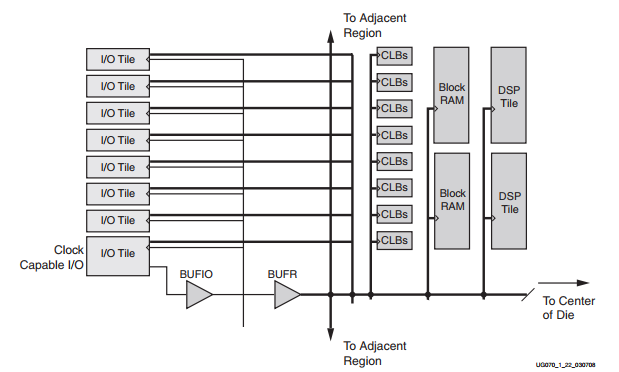

پینهای ورودی خروجی Clock Capable IO زوجهای تفاضلی کاملاً عمومی هستند که یکسری اتصالات خاص سخت افزاری به منابع کلاک محلی و بعضاً منابع کلاک سرتاسری دارند. وقتی این پینها به عنوان ورودی کلاک استفاده بشوند، میتوانند به عنوان ورودی BFFIO و BUFR استفاده بشوند.

- هر ناحیه کلاک در تراشههای Virtex-4 دو پین اختصاصی Clock Capable IO دارد.

- هر ناحیه کلاک در تراشههای Virtex-5 دو پین اختصاصی Clock Capable IO دارد.

- هر ناحیه کلاک در تراشههای Virtex-6 چهار پین اختصاصی Clock Capable IO دارد.

هم در کلاکهای محلی و هم در کلاکهای سرتاسری، وقتی قرار است پینهای ورودی کلاک به صورت تکی استفاده بشوند، الزاماً باید از پایه P باید استفاده کنید. زیرا ارتباط مستقیم به مسیرهای کلاک فقط از طریق این پین وجود دارد و پایه N نمیتواند در این شرایط برای ورودی کلاک استفاده میشود. پایه N تنها میتواند به عنوان یک ورودی یا خروجی معمولی استفاده بشود.

در تراشههای مختلف با توجه به چیدمان قرار گیری ستونهای IO همینطور تعداد آنها این ورودیها ممکن است دسترسیهای دیگری نیز داشته باشند. مثلاً میتوانند مستقیماً به ورودی کلاک یک MMCM متصل بشوند. در این شرایط کیفیت سیگنال کلاک نسبت به کلاک دریافتی از GCLK ها بیشتر است. البته MMCM و پینهای کلاک محلی الزاماً باید در یک ناحیه باشند.

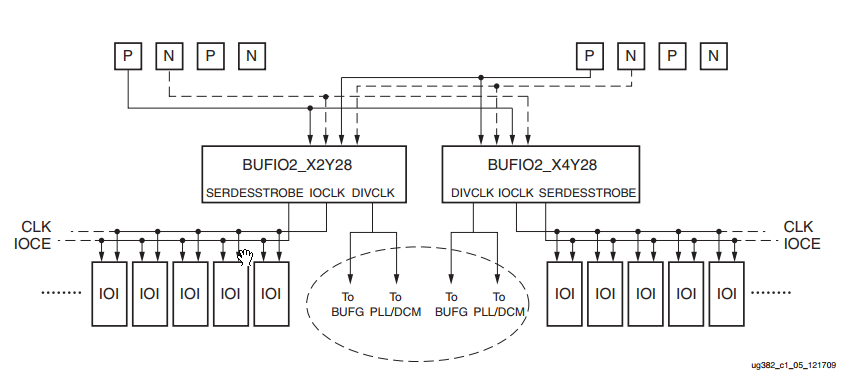

بافرهای ورودی خروجی (IO Clock Buffer – BUFIO)

بافرهای BUFIO یکی از انواع بافرهای محلی هستند که مسیرهای اختصاصی کلاک در هر ناحیه را تغذیه میکنند و در ارتباط مستقیم با منابع IO هستند. این کار به صورت کاملاً مستقل از مسیرهای سرتاسری صورت میپذیرد. معمولاً بافرهای BUFIO به صورت ایدهال برای کاربردهایی که کلاک ورودی سنکرون با داده داریم (source Synchronous) مناسب هستند. یک مثال مناسب برای این کاربرد، داده و کلاک دریافتی از تراشههای مبدل آنالوگ به دیجیتال است.

در برخی از تراشهها چهار و در برخی دیگر دو بافر BUFIO در هر بانک وجود دارد. دو تا از BUFIO ها فقط در همان ناحیه کلاک و دو تا از آنها در ناحیه کلاک مجاور بالایی و یا پایینی میتوانند مورد استفاده قرار بگیرند. نکته مهم اینجاست که BUFIO ها نمیتوانند کلاک مورد نیاز برای منابع منطقی درون تراشه را تأمین کنند. زیرا فقط به منابع ورودی خروجی (IO) دسترسی دارند.

بافرهای کلاک محلی (Regional Clock Buffer – BUFR)

دیگر بافر کلاک محلی BUFR نام دارد. این بافر هم مشابه BUFIO تنها میتواند برای تأمین کلاک مورد نیاز درون شبکه کلاک محلی استفاده بشود و مستقل از شبکه کلاک سرتاسری است.

برخلاف بافرهای BUFIO ها بافرهای BUFR ها میتوانند به منابع منطقی درون تراشه دسترسی داشته باشند. علاوه بر این، این بافرها میتوانند به تعدادی از مسیرهای محلی کلاک در همان ناحیه و تعدادی از مسیرهای محلی کلاک در نواحی مجاور بالایی و پایینی دسترسی داشته باشند (CLB, block RAM, etc).

ورودی این بافرها علاوه بر پینهای کلاک محلی میتوانند اتصالات داخلی تراشه یا IO ها یا MMCM ها باشد. این بافرها میتوانند نسخه تقسیم شدهای از کلاک ورودی را نیز تولید کنند. تقسیم بر یک تا ۸ امکان پذیر است.

در عمل بافرهای BUFR در کاربردهای source-synchronous که نیاز به مدیریت محدودههای کلاک (clock domain crossing) دارند یا کاربردهایی که نیاز به تبدیل سریال به موازی دارند، بهترین انتخاب هستند.

- تعداد آنها در Virtex-5 دو تا است زیرا این تراشهها ۴ خط کلاک محلی دارند.

- تعداد آنها در Virtex-6 دو تا است زیرا این تراشهها ۲ خط کلاک محلی دارند.

نتها و مسیرهای کلاک محلی

علاوه بر مسیرها و درخت کلاک سرتاسری که بخش بزرگی از شبکه کلاک سرتاسری هستند. در تراشههای FPGA یکسری نِت یا مسیر کلاک محلی وجود دارد که این مسیرهای کلاک هم برای کارکردهایی با حداقل توان و حداقل کجی طراحی شدهاند. نکته بسیار مهم اینجاست که مسیرهایی که استفاده نشوند، قطع میشوند. این شبکه کلاک به صورت اتوماتیک زمانی که تمام منابع منطقی درون تراشه استفاده شده باشند، فن اوت درخت کلاک را مدیریت میکنند.

تعداد این مسیرهای کلاک محدود است و مثلاً در تراشههای Virtex-6 برابر با ۶ عدد است. این مسیرهای کلاک کاملاً محلی و مستقل از شبکه کلاک سرتاسری هستند. برای دسترسی به نِتهای کلاک محلی، بافرهای BUFR باید به صورت دستی توسط طراح درون کد فراخوانی شوند.

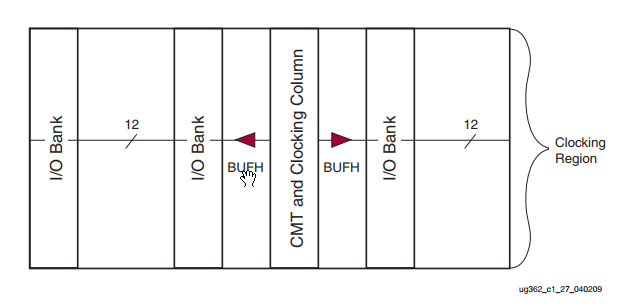

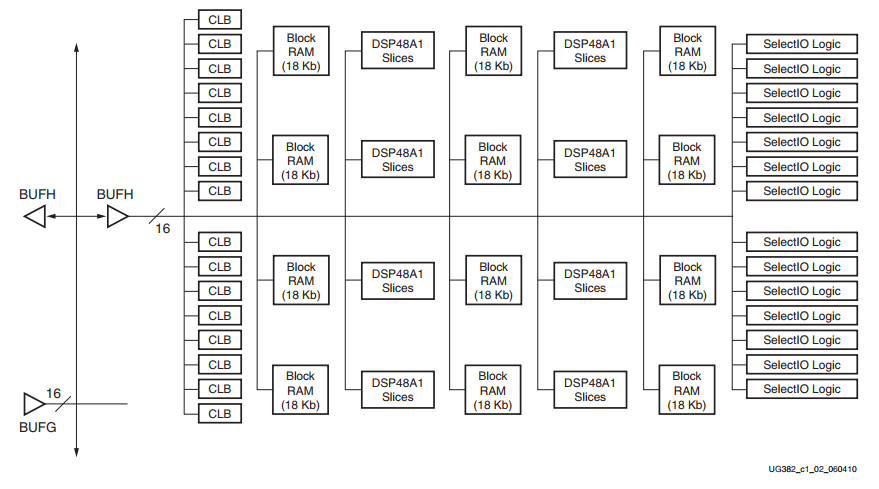

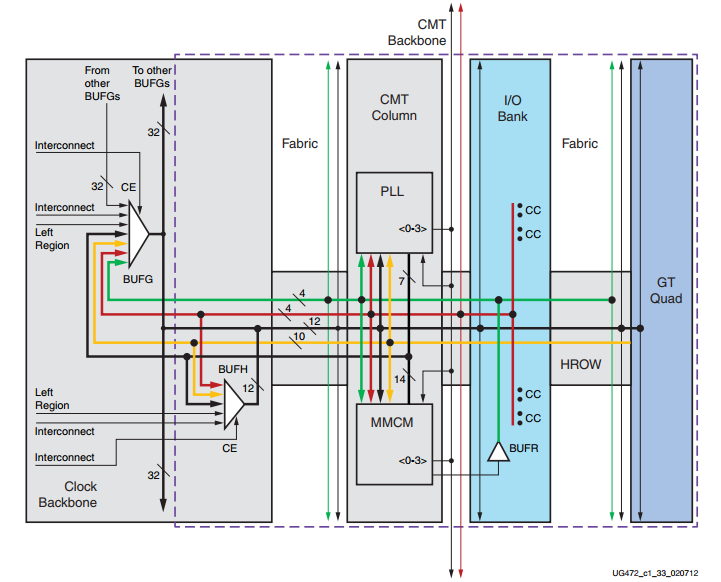

بافرهای کلاک افقی (Horizontal Clock Buffer–BUFH)

این بافرها در تراشههای Virtex-6 معرفی شدند و تا قبل از آن وجود نداشتند. بافرهای کلاک افقی که BUFH نام دارند روی ستون فقرات افقی درخت کلاک قرار دارند و خروجی آنها تنها در یک ناحیه کلاک قابل استفاده میباشد. تراشههای Virtex-6 هر ناحیه ۱۲ بافر BUFH دارند. هر بافر BUFH یک پین فعال ساز دارد که میتوان به صورت پویا آن را فعال و یا غیر فعال کرد. ورودی بافرهای BUFH توسط یکی از ورودیهای زیر تأمین میشود.

- توسط خروجی MMCM ها

- توسط خروجی BUFG ها

- اتصالات و اینترکانکتهای محلی

- ورودی خروجی کلاک محلی

در مقایسه با بافرهای BUFG بافرهای BUFH مصرف توان پایین تری دارند.

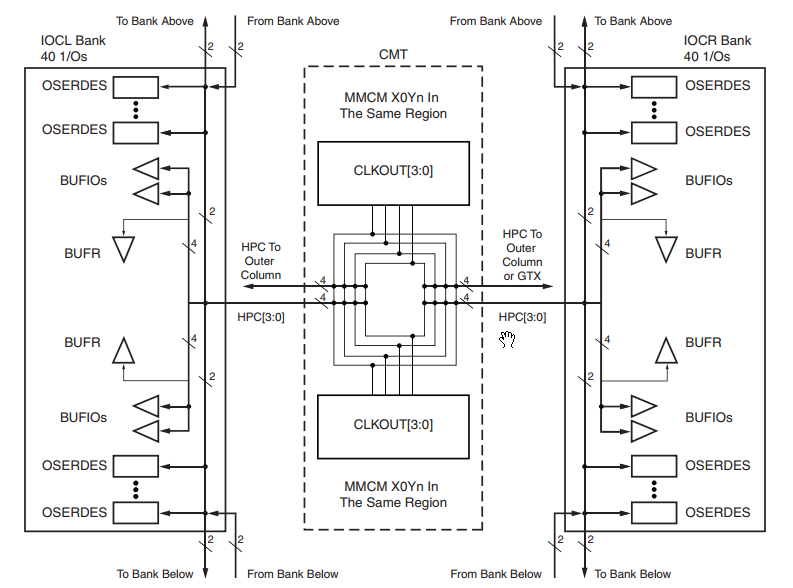

کلاکهای با کارایی بالا فقط در Virtex-6

مسیرهای HPC ، کوتاه شده عبارت High Performance Clock یکسری خطوط اختصاصی پرسرعت هستند که کاربردهایی بسیار محدود دارند. توضیح آنها خارج از حوصله این مقاله است و تنها در تراشه های Virtex-6 وجود داشتند، از این رو تنها به ارائه یک شکل از کلیات آن بسنده میکنیم.

توزیع کلاک در Spartan-6

در تراشههای Spartan-6 شبکه توزیع کلاک متشکل از چهار بخش است:

- پینها یا پدهای ورودی کلاک سرتاسری (GCLK)

- بافرها و مالتی پلکسرهای کلاک سرتاسری (BUFG, BUFGMUX)

- بافرهای کلاک ورودی/خروجی (BUFIO2, BUFIO2_2CLK, BUFPLL)

- بافرهای محلی و افقی کلاک (BUFH)

دو نوع شبکه کلاک در تراشههای Spartan-6 وجود دارد.

- شبکه کلاک سرتاسری که مسیرهای با تأخیر کم و اختصاصی بین کلاک و سایر منابع درون تراشه ایجاد میکند.

- شبکه کلاک محلی ورودی خروجیها که کلاکهایی بسیار کارآمد و دقیق با حداقل کجی را برای منابع ورودی خروجی فراهم میکند.

به شکل خلاصه موارد استفاده و عملکرد هر کدام از این بافرها در ادامه تشریح گردیده است:

بافرهای BUFGMUX همچون نسلهای قبلی میتوانند به عنوان مالتی پلکسر برای سوییچ کردن بین دو منبع کلاک سرتاسری و یا در قالب یک بافر ساده BUFG بکار گرفته بشوند. این بافر تنها بافری است که به صورت مستقیم به منابع و مسیرهای کلاک سرتاسری و در نتیجه ورودیهای کلاک فلیپ فلاپها دسترسی دارد. با وجود اینکه کلاک ورودی فلیپها از طریق منابع و مسیرهای هم منظوره (مسیرهایی غیر از مسیر کلاک که برای اتصال LUT و Memory و … استفاده میشوند) درون تراشه قابل تأمین است، اما به دلیل بالا بودن کجی کلاک این کار توصیه نمیشود.

بافرهای BUFPLL و BUFIO2 تنها برای تأمین کلاکهای مورد نیاز در یک ناحیه کلاک قابل استفاده میباشند. کارایی آنها در مقایسه با بافرهای سرتاسری BUFGMUX بالاتر است و به همین دلیل است که خروجیهای آنها انعطاف پذیری محدودی دارد. تنها مقاصد مجاز برای این بافرهای ورودی کلاک عناصر ورودی ISERDES و یا عناصر خروجی OSERDES درون IOB های هر بانک میباشد. البته BUFIO2 امکان ارسال سیگنال کلاک به BUFG ها و همینطور DCM و PLL را نیز دارا میباشد. در تراشههای Spartan6 یک بافر ویژه دیگر نیز وجود دارد که BUFIO2_2CLK نام دارد و میتواند در مواردی که نیاز به در اختیار داشتن یک کلاک تفاضلی درون تراشه داریم به جای BUFIO2 مورد استفاده قرار بگیرد. یک مثال مناسب برای آن کلاکهای DDR عناصر ISERDES2 و OSERDES2 میباشد.

به شکل مشابه بافرهای BUFPLL برای تأمین کلاکهایی به سمت ورودی/خروجیها هدایت میشوند، کاربرد دارند. ابن بافرها در کاربرهای SDR میتوانند مستقیاً یک مسیر اختصاصی از PLL به سمت ورودی خروجیها در همان ناحیه کلاک برقرار کننند.

بافرهای BUFH به عنوان یکسری بافر کمکی و البته با کیفیت در شبکه کلاک محلی برای تسهیل فرایند مسیریابی در هر ناحیه کاربرد دارند و به نوعی دسترسی مستقیم به بخش افقی مسیرهای سرتاسری کلاک را فراهم میآوردند.

و نکته آخر اینکه، این تراشهها خبری از پینهای Clock Capable در بانکهای IO نیست و تنها پینهای کلاک سرتاسری در آنها وجود دارد.

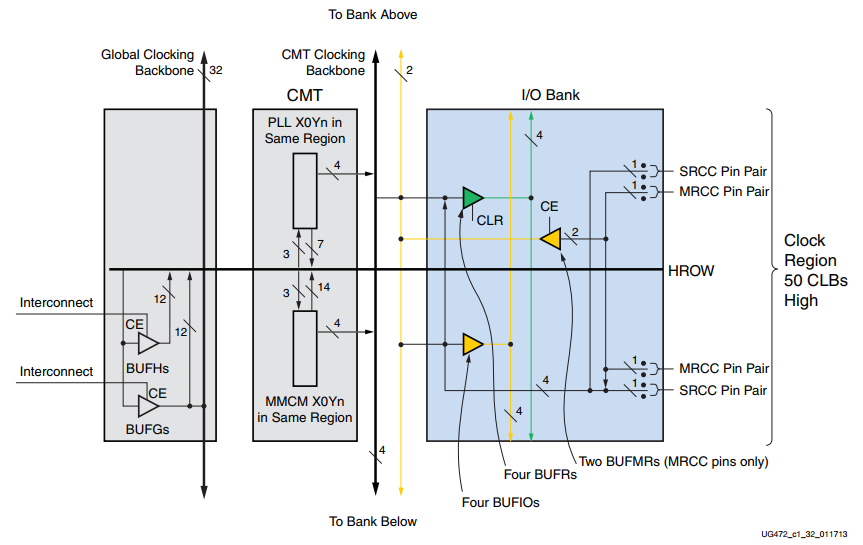

توزیع کلاک در 7Series

یکی از مهمترین تغییراتی که در تراشههای 7Series نسبت به نسلهای قبلی ایجاد شده است، حذف پینهای GCLK است. در این تراشهها دیگر خبری از پینهای کلاک سرتاسری نیست و تنها پینهایی که میتوانند کلاک را به سمت شبکه با کیفیت کلاک درون تراشه هدایت کنند، پینهای Clock Capable در هر ناحیه کلاک یا بانک ورودی خروجی میباشد.

هر ناحیه کلاک یا به طور خاص بانک IO در تراشههای FPGA دارای تعدادی پین ورودی با برچسب CC است که سیگنال کلاک برای ورود به مسیرهای اختصاصی کلاک درون تراشه باید الزاماً از طریق این پینها به FPGA وارد شود. مسیرهای اختصاصی کلاک در تراشههای FPGA از پینهای (Clock Capable) شروع میشود و با استفاده از طیف گستردهای از بافرهای پرسرعت در همان ناحیه کلاک و یا در سرتاسر تراشه منتشر میشود.

با کمک بافرها، مسیرهای اختصاصی و پینهای CC ، کلاک ورودی به تراشه با در نظر گرفتن یکسری محدودیت به بخشهای مختلف آن قابل اتصال میباشد، که جزئیات آن به شرح زیر است:

- اتصال به مسیرهای کلاک سرتاسری در نیمه بالایی یا پایینی تراشه

- اتصال به مسیرهای اختصاصی کلاک ورودی/خروجیها در همان ناحیه کلاک و نواحی کلاک مجاور بالایی و پایینی

- اتصال به مسیرهای کلاک محلی در همان ناحیه کلاک و نواحی کلاک مجاور بالایی و پایینی

- اتصال به واحدهای CMT درون در همان ناحیه کلاک و نواحی کلاک مجاور بالایی و پایینی

همچون نسلهای قبلی در تراشههای 7Series هم انواع مختلفی در دسترس کاربر قرار دارد و شما به عنوان طراح سناریوی کلاک میتوانید با کمک آنها به خوبی محدودههای مختلف کلاک و نحوه تعامل بین آنها را کنترل کنید. در ادامه فهرستی از مهمترین بافرهای کلاک در این خانوده ارائه شده است. دقت شود که این فهرست با نسلهای پیشین تطابق کامل ندارد، از این رو شما برای آشنایی دقیق با بافرها در هر نسل الزاماً باید مستندات همان نسل را مطالعه کنید.

- بافرهای BUFIO

- بافرهای BUFR

- بافرهای BUFMR

- بافرهای BUFG/BUFGCTRL/BUFGMUX

- بافرهای BUFH

بافرهای BUFIO and BUFR : این دو دسته بافر در کلاکهای محلی که نیاز نیست به سرتاسر طرح و سایر نواحی کلاک گسترانیده شوند، استفاده میشوند. یکی از مهمترین و اصلی ترین کاربردهای آنها استفاده در اینترفیسهای IOSERDES است. بافرهای محلی باعث کاهش کجی کلاک هنگام توزیع کلاک میشوند.

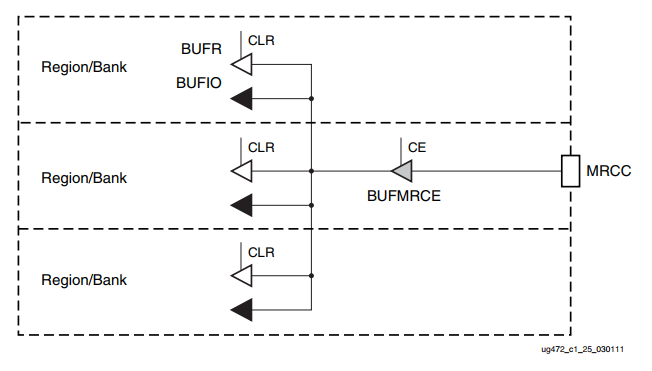

بافرهای BUFMR : این بافرها برای اولین بار در تراشههای 7Series معرفی شدهاند و برخلاف بافرهای BUFR و BUFIO که تنها به صورت محلی و در ناحیه کلاکی که در آن واقع شدهاند، قابل استفاده بودند، بافرهای BUFMR برای انتقال سیگنال کلاک به نواحی کلاک مجاور هستند به همین دلیل Multi-Region نام گذاری شدند. ورودی بافرهای BUFMR باید الزاماً توسط پینهای MRCC یا همان پینهای اختصاصی کلاک Multi-Region تأمین شود.

بافرهای BUFG, BUFGCTRL, and BUFGMUX : هر سه بافر تحت عنوان بافرهای کلاک سرتاسری یا عمومی (Global Buffer) شناخته میشوند و بافرهایی هستند که از آنها برای انتقال سیگنال کلاک به سرتاسر تراشه استفاده میشود. دسترسی به بافرهای سرتاسری تنها از طریق پینهای اختصاصی کلاک امکان پذیر است. این بافرها فن اوت کلاک بالایی دارند و در بخش مرکزی تراشه قرار دارند. همچون نسلهای قبلی از بافرهای سرتاسری میتوان را به صورت یک BUFG ساده و یا بافر کلاک همراه با مالتی پلکسر و یا بافر کلاک همراه با فعال ساز کلاک پیاده سازی کرد.

بافرهای BUFH : بافرهای کلاک افقی که با نام BUFH شناخته میشوند روی مسیرهای انشعابی و افقی درخت کلاک در هر یک نواحی کلاک قرار دارند. این بافرها برای تأمین کلاک آن ناحیه به کار میروند. بافرها BUFH دارای پایه فعال ساز هستند و به کمک آنها میتوان شبکه کلاک یک ناحیه را به صورت کلی فعال و یا غیر فعال کرد. این قابلیت برای کنترل مصرف توان سیستم در بخشهایی از تراشه که به صورت مداوم استفاده نمیشوند، بسیار مفید است.

در تراشههای 7Series در هر بانک ۴ پین اختصاصی برای ورودی کلاک وجود دارد. این پینهای اختصاصی کلاک میتوانند مانند IO های معمولی مورد استفاده قرار بگیرند، ولی در عین حال اتصالات لازم برای دسترسی به منابع داخلی کلاک درون تراشه برای آنها در نظر گرفته شده است. پس اگر از این پینها به عنوان IO معمولی استفاده شود، مشکلی وجود نخواهد داشت.

هر پین کلاک میتواند به صورت تکی (Single Ended) مورد استفاده قرار گیرد و یا با زوج شدن دو پین کلاک مجاور به صورت تفاضلی (Differential) پیکره بندی شود. به این ترتیب در این تراشهها هر بانک میتواند چهار پین کلاک تکی و یا تفاضلی داشته باشد. دو تا از این پینها از نوع Multi-Region Clock Capable (MRCC) و دو تای دیگر از نوع Single-Region Clock Capable (SRCC) میباشند. پینهای MRCC علاوه بر ناحیه کلاک پیش فرض میتوانند به نواحی کلاک مجاور نیز دسترسی داشته باشند.

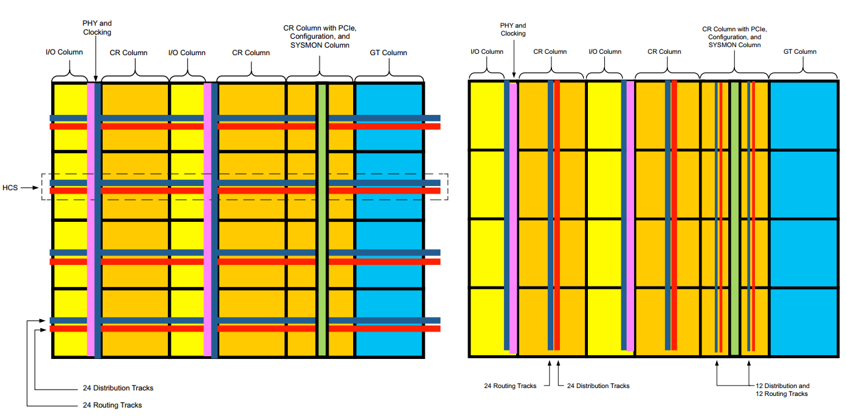

توزیع کلاک در UltraScale

در تراشههای UltraScale و +UltraScale دیگر خبری از تنوع گسترده بافرها در 7Series نیست و پیچیدگی کار برای طراح کاهش یافته است. بافرهای BUFG بیش از گذشته مورد استفاده قرار میگیرند و قابلیتهای آنها نیز افزایش یافته است.

یکی از مشکلات طراحی در نسلهای قبلی استفاده درست از منابع و بافرهای مختلف بود. احتمالاً هر مهندس طراح کهنه کاری حداقل یکبار خطای عدم امکان مسیریابی کلاک را محیط توسعه ISE یا Vivado مشاهده کرده است. این خطا غالباً به دلیل استفاده نادرست از بافرها و عدم درک مناسب جایگاه و کارکرد آنها رخ میدهد. شرکت Xilinx با هدف مرتفع کردن این مشکل گام بزرگی در تراشههای UltraScale برداشته است و یکسان سازی گستردهای روی معماری داخلی شبکه کلاک اعمال کرده است. به نوعی میتوان گفت که Xilinx معماری درخت و شبکه توزیع کلاک را به صورت کامل باز طراحی کرده است و آن را ASIC-Like Clock Architecture نامیده است.

پینهای اختصاصی کلاک در این تراشهها Global Clock (GC) نام دارند و کلاک خارجی از طریق این پینهای سرتاسری وارد تراشه میشود. هر بانک IO دارای ۴ زوج تفاضلی از این پینهای GC است. این پینها به تمامی منابع کلاک درون تراشه اعم از بافرها، MMCM ها و به طور کلی کلیه عناصر داخلی CMT ها دسترسی دارند. تقریباً تمامی قوانینی که برای استفاده از پینهای GCLK و CC که در نسلهای قبلی بیان شد، برای پینهای GC نیز صدق میکند.

همانطور که در بخش اول اشاره شد، با وجود متحول شدن نحوه چیدمان نواحی کلاک (CR)، خطوط یا مسیرهای افقی کلاک همچنان در این نسل نیز وجود دارند و اصطلاحاً ستون فقرات افقی کلاک یا Horizontal Clock Spine – HCS نامیده میشوند. ولی دیگر خبری از ستون فقرات عمودی کلاک نیست. هر HCS در برگیرنده منابع زیر است:

- منابع (خطوط) توزیع (distribution) کلاک

- منابع (خطوط) مسیریابی (routing) کلاک

- بافرهای کلاک (leaf buffers)

- اتصالات شبکه کلاک (clock interconnects) و

- ریشه شبکه کلاک (root of the clock network)

مفهوم مهم دیگری که در این نسل از تراشهها برای اولین بار وارد ادبیات Xilinx شده است، مفهومی به نام PHY است. در کنار هر بلوک IO یک بلوک PHY تعبیه شده است که در برگیرنده CMT ، بافرها و مالتی پلکسرهای سرتاسری است. در واقع کلاک از طریق منابع (خطوط) مستقل مسیریابی و یا توزیع در HCS وارد اتصالات کلاک میشود و از آنجا به سمت CR ها و یا IO ها هدایت میشود.

همانطور که احتمالاً به درستی متوجه شدهاید، در این معماری از دو نوع منبع برای هدایت کلاک درون تراشه استفاده شده است، که عبارتند از:

- منابع یا خطوط توزیع کلاک (Distribution Tracks)

- منابع یا خطوط مسیریابی کلاک (Routing Tracks)

در حالت کلی ۲۴ خط عمودی توزیع کلاک و ۲۴ خط افقی توزیع کلاک و به موازات آن ۲۴ خط عمودی و ۲۴ خط افقی مسیریابی کلاک وجود دارد. توضیح بیشتر در مورد کاربردها و تفاوتهای این دو نیاز به یک مقاله اختصاصی مجزا دارد، اما به طور کلی هدف اصلی از این خطوط، هدایت مناسب سیگنال کلاک از بافرهای سرتاسری به سمت نقطه مرکزی است. نقطه مرکزی (central point) شبکه کلاک، که تحت عنوان ریشه کلاک یا (clock root) نیز شناخته میشود، جایی است که کلاک از آن جا میتواند به سمت مصرف کننده نهایی هدایت شود.

مشابه قبل در هر CMT علاوه بر یک بلوک MMCM و ۲ بلوک PLL تعداد قابل توجهی بافر سرتاسری وجود دارد که عبارتند از:

- ۲۴ بافر سرتاسری از نوع با BUFGCE

- ۸ بافر سرتاسری از نوع BUFGCTRL و

- ۴ بافر سرتاسری از نوع BUFGCE_DIV

در این تراشهها بین ۱۹۲ تا ۷۲۰ بافر سرتاسری کلاک وجود دارد که این باعث میشود دسترسی به سیگنال کلاک با کیفت تر در سراسر تراشه امکان پذیر شود. نکته جالبی که وجود دارد این است که مهاجرت از نسلهای قبلی به این نسل برخلاف چیزی که نظر میرسد، چندان پیچیده نیست و اکثر تفاوتها به صورت اتوماتیک توسط Vivado مدیریت میشوند، مثلاً در شکل زیر میتوانید نحوه جایگزینی اتوماتیک بافرها را مشاهده کنید.

جمع بندی

هر طرح سنکرونی که روی تراشههای FPGA پیاده سازی شود، حداقل به یک منبع کلاک و تعداد زیادی مسیر برای توزیع کلاک درون تراشه نیاز دارد، این در حالی است که در بسیاری از موارد به بیش از یک کلاک برای پیاده سازی طرح نیاز خواهیم داشت و این مسأله میتواند طراحی سناریوی توزیع کلاک را به شدت تحت تأثیر قرار دهد. تعداد بافرهای با کیفیتی که میتوانند در مسیرهای اختصاصی کلاک برای هدایت سیگنال کلاک به بخشهای مختلف استفاده شوند، محدود هستند. از این رو این منابع باید به شکل مناسبی در قالب یک سناریوی منسجم مدیریت شوند. به عنوان مثال در صورتی که طرح ما تنوع و تعداد کلاکهای مورد استفاده زیادی داشته باشد، باید حتماً ابتدا کلاکهای حساس تر که فرکانس و فن-اوت بالاتری دارند را به بافرهای سرتاسری و پرسرعت تر متصل کنیم.

با استفاده از بافرهایی که معرفی کردیم، میتوانیم به صورت پویا کلاک را در بخشی از تراشه فعال یا غیرفعال کنیم. این فعال سازهای کلاک میتوانند به عنوان یکی از تکنیکهای گیت کردن استفاده شوند و باعث کاهش توان مصرفی شوند.

بحث در مورد منابع تولید و توزیع کلاک هر اندازه هم که ادامه پیدا کند، باز هم تمام نمیشود. در این مقاله سعی کردیم هر آنچه را که برای شروع کار مورد نیاز است، معرفی کنیم. بدیهی است هر زمان که کار روی یک پروژه جدید را آغاز میکنیم باید نکات کلیدی و ویژگیهای تراشه هدف را مجدداً مرور کنیم تا بهترین طراحی ممکن را مطابق با منابع درون آن تراشه ارائه کنیم.

10 در مورد “مدیریت سیگنال کلاک: بخش دوم شبکه توزیع کلاک در FPGA”

Тёплый и уютный каркасный дом для круглогодичного проживания в любой зоне

каркасный дом цена [url=https://www.karkasnie-doma-pod-kluch06.ru/]https://www.karkasnie-doma-pod-kluch06.ru/[/url] .

Гелиевые шары для детских праздников— доставка в Нижнем Новгороде по лучшим ценам.

Гелиевые шарики Нижний Новгород [url=http://www.shariki-shop47.ru/]http://www.shariki-shop47.ru/[/url] .

بسیار عالی بود. ممنونم از به اشتراک گذاری اطلاعاتتون.

دم شما گرم

ارادتمندم، از پیامتون سپاسگزارم

An impressive share! I have just forwarded this onto a co-worker who has been doing a little research on this. And he actually bought me lunch simply because I found it for him… lol. So allow me to reword this…. Thank YOU for the meal!! But yeah, thanx for spending time to talk about this subject here on your web page.

Everything is very open with a clear description of the issues. It was definitely informative. Your site is useful. Thank you for sharing!

دم شما گرم. ممنونم بابت به اشتراک گذاشتن دانشتون

ارادتمندم، از پیامتون سپاسگزارم

با سلام،

من این پست رو خوندم و بسیار لذت بردم. اطلاعات این پست نشان دهنده دانش بسیار بالای شما و نحوه بیان خیلی خوب شماست. امیدوارم همچنان مطالب بیشتری از شما در اختیار بقیه قرار بگیره.

با آرزوی موفقیت برای شما

ارادتمندم، از اظهار لطفی که داشتید سپاسگزام