مقدمه

این روزها، تقریباً تمام IP های Xilinx از اینترفیس AXI استفاده میکنند. تراشههای ZYNQ و ZYNQ MP و حتی پردازندههای نرم افزاری میکروبلیز (Micoblaze) و پردازندههای قدرتمند و جدید Versal همگی از اینترفیسهای AXI استفاده میکنند. پر واضح است که اینترفیسهای AXI بخشی جدایی ناپذیر از هر طراحی جدید در تراشههای شرکت Xilinx هستند. درک صحیح مبانی AXI کمک فراوانی به افزایش بهره وری طراح در زمان طراحی و حتی خطایابی سیستم میکند.

در این آموزش از پایگاه دانش هگزالینکس که اولین آموزش از سری آموزشهای AXI است، مبانی و مفاهیم اینترفیسهای AXI3/AXI4 را در تراشههای Xilinx خدمتتان ارائه میکنیم. در اولین گام محبوریم از بخشهای کمی خسته کننده، نه چندان جذاب و البته بسیار مهم شروع کنیم. بسیاری از بخشهای مهمتر، در قسمتهای بعدی این سری آموزشی پوشش داده میشود، ولی در صورتی که به این توضیحات اولیه تسلط پیدا نکنید، در درک آنها با مشکل روبرو میشوید. مقدمه کافیست، بدون هیچ توضیح بیشتری به سراغ تئوری و اصطلاحات مهم در AXI میرویم.

اینترفیس AXI چیست؟

واژه AXI کوتاه شده عبارت Advanced eXtensible Interface است. AXI پروتکل یک اینترفیس است و توسط ARM به عنوان یکی از استانداردهای AMBA معرفی شده است.

مشخصات کامل استانداردهای AXI3/AXI4 به شکل رایگان از طریق وبسایت ARM قابل دانلود است. در صورتی که تمایل دارید با تمامی جزئیات این پروتکل آشنا شوید، پیشنهاد میکنم این فایلها را دانلود و مطالعه کنید.

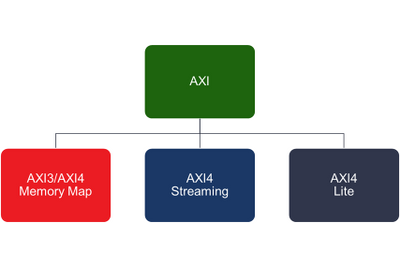

به طور کلی سه نوع اینترفیس AXI4 وجود دارد:

- اینترفیس AXI4-Full : این اینترفیس برای کاربردهایی که نیاز به کارایی بالا دارند، به کار برده میشود.

- اینترفیس AXI4-Lite : این اینترفیس برای ارتباطات ساده و مبادله فرامین کنترلی یا خواندن وضعیت رجیسترها کاربرد دارد.

- اینترفیس AXI-Stream : این اینترفیس برای کاربردهایی که نیاز به تبادل پرسرعت دیتا به صورت استریم دارند، استفاده میشود.

مفهوم اینترفیس Memory-Mapped

اینترفیسهای AXI4 ، AXI3 و AXI4-Lite اصطلاحاً اینترفیسهای Memory-Mapped هستند. یک پورت یا اینترفیس Memory-Mapped روشی برای تبادل دیتا و دستورالعمل بین پردازنده و پریفرالهای متصل به آن است. در این اینترفیس، پردازنده و پریفرال به جای اینکه مستقیماً به یکدیگر وصل بشوند، یک فضای آدرس مشخص از حافظه را بین خودشان به اشتراک میگذارند. به این ترتیب پردازنده و پریفرال به آدرسهای حافظه نگاشت داده میشوند. به بیان سادهتر در اینترفیسهای Memory-Mapped یک پریفرال از نظر پردازنده به عنوان یک حافظه در نظر گرفته میشود و پردازنده برای ارسال دیتا و یا دستورالعمل به این پریفرال، آدرسهای مختلف این حافظه را مقدار دهی میکند. در این شکل از تبادل داده، پردازنده معمولاً Master و پریفرالها Slave هستند و کنترل فرایند تبادل داده توسط Master انجام میشود. این نوع اینترفیسها به شدت باعث افزایش کارایی سیستم میشوند.

نکته: در این آموزش تمرکز اصلی ما روی اینترفیسهای Memory-Mapped است، از این رو اینترفیس AXI-Stream در این مقاله پوشش داده نمیشود.

هر اینترفیس دارای مجموعهای از پورتهای ورودی و خروجی است. در اینترفیس AXI این پورتها درون یکسری کانال دسته بندی شدهاند. برای دسترسی به لیست کامل این پورتها به اینجا مراجعه کنید.

مطالعه جزئیات بیشتر در UG761

کانالهای خواندن و نوشتن در AXI

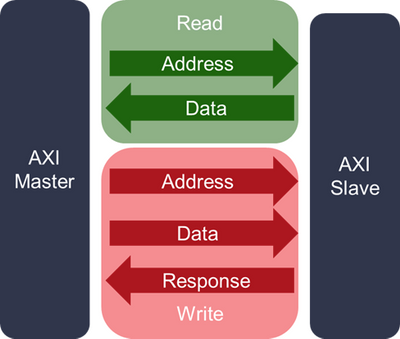

در پروتکل AXI پنج کانال برای خواندن یا نوشتن تعریف شده است.

از این پنج کانال، دو کانال برای مدیریت تراکنشهای خواندن مورد استفاده قرار میگیرند و عبارتند از:

- کانال خواندن آدرس (read address channel)

- کانال خواندن دیتا (read data channel)

و سه کانال برای مدیریت تراکنشهای نوشتن استفاده میشوند که عبارتند از:

- کانال نوشتن آدرس (write address channel)

- کانال نوشتن دیتا (write data channel)

- کانال نوشتن پاسخ (write response channel)

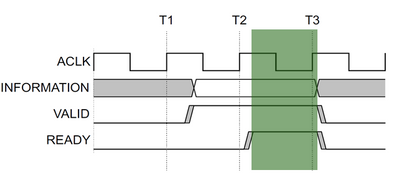

به بیان بسیار ساده اصطلاح کانال، به مجموعهای از سیگنالهای مستقل در پروتکل AXI اطلاق میشود که به همراه دو سیگنال VALID و READY برای تبادل یک نوع خاص از اطلاعات به کار گرفته میشوند.

مطالعه جزئیات بیشتر در UG761

نکته: اینترفیسهای AXI4 ، AXI3 و AXI4-Lite میتوانند به صورت فقط خواندنی (read-only) پیکرهبندی شوند و تنها دارای دو کانال خواندن باشند و یا به صورت فقط نوشتنی (write-only) تعریف شوند و تنها دارای سه کانال نوشتن باشند.

بخش کوچکی از دیتا که در هر لحظه، روی یک کانال ارسال میشود، تحت عنوان ترنسفر (transfer) نام گذاری میشود. تنها زمانی یک ترنسفر بین فرستنده و گیرنده اتفاق میافتد که هر دو سیگنال کنترلی VALID و READY همزمان با همراه لبه بالارونده کلاک فعال شوند. برای مثال در شکل زیر، ترنسفر در لحظه T3 انجام میشود.

تراکنش نوشتن به مجموعه ترنسفرهایی اطلاق میشود که در نهایت منجربه نوشتن یک دیتا ازماژول Master درون حافظه ماژول Slave میشود. مشابهاً تراکنش خواندن نیز به مجموعه ترنسفرهایی اطلاق میشود که در نهایت منجربه خواندن یک دیتا از ماژول Slave به درون حافظه ماژول Master میشود.

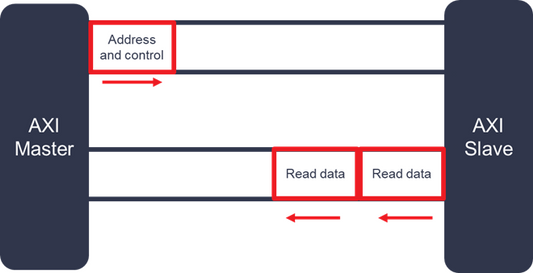

تراکنشهای خواندن AXI

یک تراکنش خواندن نیاز به چندین ترنسفر روی هر دو کانال خواندن دارد.

- ابتدا، برای تنظیم آدرسی که قرار است از آن عملیات خواندن انجام شود، یک ترنسفر آدرس از طریق کانال خواندن آدرس، از Master به سمت Slave آغاز میشود.

- سپس ترنسفر دیتا از آدرس درخواستی، از سمت Salve به سمت Master در کانال خواندن دیتا انجام میشود.

البته در این تراکنش، الزامی به تعیین آدرس قبل از ارسال دیتا نیست. یعنی میتوان آدرس مورد نیاز برای تراکنش را بعد از ترنسفر دیتا، ارسال کرد. کاملاً واضح است که ماژول Slave به عنوان گیرنده نیز میتواند قبل از دریافت آدرس، دیتا را از فرستنده دریافت کند.

توجه کنید که، همانطور که در شکل نیز مشاهده میکنید، ممکن است برای هر آدرس بیش از یک ترنسفر دیتا انجام شود. این نوع از تراکنش اصطلاحاً burst نامیده میشود.

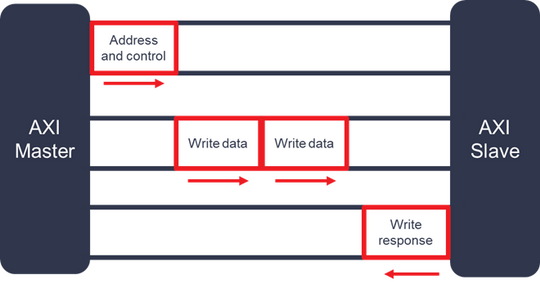

تراکنشهای نوشتن AXI

یک تراکنش نوشتن نیاز به چندین ترنسفر روی هر سه کانال نوشتن دارد.

- ابتدا، برای تنظیم آدرس، یک ترنسفر آدرس از طریق کانال نوشتن آدرس، از Master به سمت Slave انجام میشود.

- سپس ترنسفر دیتا به آدرس درخواستی، از سمت Master به سمت Salve در کانال نوشتن دیتا ارسال میشود.

- در نهایت در پاسخ به این درخواست نوشتن، یک ترنسفر پاسخ از سمت Slave به سمت Master در کانال نوشتن پاسخ صادر میشود. این پاسخ موفقیت آمیز بودن عملیات نوشتن را اعلام میکند.

پاسخ میتواند یکی از چهار مقدار زیر باشد. این پاسخها در کانال پاسخ نوشتن ترنسفر میشوند:

- تایید: این پاسخ دسترسی نرمال و موفقیت آمیز به Slave را تأیید میکند. OKAY-0b00

- تایید ویژه: این پاسخ دسترسی ویژه و موفقیت آمیز به Slave را تأیید میکند. EXOKAY-0b01

- خطای Slave: این پاسخ عدم موفقیت در انجام تراکنش را گزارش میکند، یعنی با وجود در دسترس بودن Slave بازهم تراکنش به دلیلی با ناموفق بوده است. SLVERR-0b10

- خطای دیکد: این پاسخ خطا غالباً توسط کامپوننت اینترکانکت تولید میشود. این خطا مشخص میکند که در آدرس مشخص شده، Slave وجود ندارد. DECERR-0b11

تراکنشهای نوشتن نیز دارای پاسخ هستند، این پاسخها درون کانال پاسخ خواندن ارسال میشوند.

البته باید توجه داشته باشیم که در انتهای هر تراکنش نوشتن یا خواندن نیاز نداریم منتظر پاسخ بمانیم. مثلاً در صورتی که به میزان کافی بافر برای دریافت دیتا در سمت Slave وجود داشته باشد، برای افزایش پهنای باند تراکنش، این امکان وجود دارد که تراکنشهای نوشتن به صورت پشت سر هم آغاز شوند و در انتها پاسخهای آنها تولید شوند. تمامی پاسخها با همین ترتیبی که تراکنشها آغاز شدهاند، تولید میشوند.

الزامات اینترفیس AXI4

یکسری الزامات برای کار با اینترفیسهای AXI4 وجود دارد که به خوبی توسط ARM مستندسازی شده است. ما به بررسی کامل تمامی این الزامات در این آموزش نمیپردازیم، اما لازم است برخی از آنها یادبگیرم و همواره بخاطر بسپاریم.

- بعد از فعال شدن سیگنال VALID توسط Master، این سیگنال باید تا زمان فعال شدن سیگنال READY توسط Slave، فعال باقی بماند. تنها در صورتی که هر دو این سیگنالها در لبه بالا رونده کلاک فعال باشند، ترنسفر موفق انجام میشود.

- سیگنال VALID در اینترفیس AXI که در حال ارسال اطلاعات، نباید وابسته به سیگنال READY اینترفیس AXI که در حال دریافت اطلاعات است، باشد. این یعنی فرستنده و گیرنده باید کاملاً مستقل از هم فعال شوند. اما همانطور که در گزینه قبلی نیز گفته شد، باقی ماندن آنها در وضعیت فعال به هم وابسته است.

- سیگنال پاسخ باید بعد از آخرین ترنسفر نوشتن، تولید شود. البته استثنا هم وجود دارد که به آن اشاره شد و در قسمتهای بعدی این سری آموزشی نیز بیشتر به آن میپردازیم.

- آدرس و دیتای وابسته به هم در یک تراکنش خواندن، باید به صورت پشت سر هم ارسال شوند.

- همواره Slave باید منتظر دو سیگنال ARVALID و ARREADY باشد. بعد از فعال شدن این دو سیگنال، سیگنال RVALID توسط Slave فعال میشود و اعتبار دادههای روی باس را تایید میکند.

در بخش بعدی از این سری آموزشی، ما روش شبیه سازی اینترفیسهای AXI4 را با استفاده از AXI Verification IP به شما آموزش خواهیم داد.

جمع بندی

این تنها یک مرور اجمالی بر اینترفیسهای AXI بود. در این آموزش کوتاه تنها بخشی از ویژگیها و الزامات اینترفیس AXI را به شما معرفی کردیم. مطالعه تمامی جزئیات اینترفیس AXI کاری زمان بر و دشوار است. از این رو نیازی نیست که تمام مستندات آن را مطالعه کنیم. این مستندات معمولاً به عنوان کتابچههای مرجع توسط طراحان حرفهای در زمان طراحی IP Core ها مورد استفاده قرار میگیرد و در زمان استفاده از IP Core ها بخشی زیادی از ملاحظات اینترفیس AXI به صورت اتوماتیک توسط Xilinx در نظر گرفته میشود.

منبع: با اقتباس از وبلاگ Xilinx

4 دیدگاه برای “اینترفیس AXI (قسمت اول: مقدمهای بر AXI)”

سلام و عرض ادب

من این قسمت رو متاسفانه متوجه نشدم

میشه توضیح بدین منظورتون چی بوده دقیقا؟

“البته در این تراکنش، الزامی به تعیین آدرس قبل از ارسال دیتا نیست. یعنی میتوان آدرس مورد نیاز برای تراکنش را بعد از ترنسفر دیتا، ارسال کرد. کاملاً واضح است که ماژول Slave به عنوان گیرنده نیز میتواند قبل از دریافت آدرس، دیتا را از فرستنده دریافت کند.”

درود بر شما امیدوارم حالتون خوب باشه

ببینید، یک تراکنش داده زمانی تکمیل میشه که تمامی بخشهای این تراکنش تکمیل بشه. حالا اگر فرض کنیم برای تکمیل تراکنش به یک آدرس و یک پی لود داده نیاز داریم. در این صورت تراکنش بعد از ترنسفر داده و آدرس تکمیل میشه، حالا کدوم زودتر و کدوم دیرتر ترنسفر بشه تفاوتی ایجاد نمیکنه، مهم اینکه هر دو ترنسفر تمام شده باشه.

سلام و ممنون از مطلب بسیار خوبتون

لطف مشکل تایپی زیر رو هم در متن برطرف بفرمایید:

** نکته: اینترفیسهای AXI4 ، AXI3 و AXI4-Lite میتوانند به صورت فقط خواندنی (read-only) پیکرهبندی شوند و تنها دارای دو کانال خواندن باشند و یا به صورت فقط نوشتنی (write-only) تعریف شوند و تنها دارای سه کانال “خواندن” باشند.

به نظر میرسه که در آخر جمله، به جای عبارت “سه کانال خواندن”، عبارت “سه کانال نوشتن” باید جایگزین بشه.

سلام بر شما دوست عزیز

مراتب قدردانی خودم را به دلیل حسن انتخاب و دقتی که هنگام مطالعه این مطلب داشتید، اعلام می دارم.

همینطور از اینکه وقت با ارزشتون را برای نوشتن این کامنت صرف کردید صمیمانه سپاسگزارم.

موضوعی که به آن اشاره کردید کاملاً صحیح است. این اشتباه مطابق با توضیحات شما برطرف شد.