مقدمه

ممکن است شما سابقه و تجربه کمی در کار با FPGA ها داشته باشید. در این صورت ممکن است شنیده باشید که افراد بعد از پیاده سازی مدارشان نسبت به عدم پایداری آن در شرایط کاری متفاوت گلایه مند هستند. از سوی دیگر ممکن است طراح با تجربهای باشید که سرد و گرم پیچیدگیهای موجود در مسیر پیاده سازی یک سیستم دیجیتال روی FPGA را چشیده است. در این صورت حتماً با یک سیستم شبه پایدار روبرو شدهاید و برای آن چاره اندیشی کردهاید. در سیستمهای شبه پایدار با اعمال تغییرات نه چندان بزرگ روی مدار پیاده سازی شده، برخی از فانکشنالیتیهای سیستم از دست میرود. در چنین شرایطی نتیجه هفتهها و یا ماهها پیاده سازی، یک سیستمِ بسیار حساس و غیر قابل اطمینان است. در این مقاله از پایگاه دانش هگزالینکس، همراه با شما، یک نگاه کلی به اهمیت پدیده گذر بین محدودههای کلاک یا Clock Domain Crossing (CDC) در FPGA میاندازیم و به شما روشها و تکنیکهای سنکرون سازی برای مراقبت از دیتا زمانی که از یک محدوده کلاک به محدوده دیگر کلاک منتقل میشوند را آموزش میدهیم.

تکنیکهای سنکرون سازی به شما کمک میکنند در کنار فانکشنالیتی مناسب، مداری پایدار و کاملاً قابل اطمینان پیاده سازی کنید. موارد فراوانی وجود دارد که در آن عدم کنترل مناسب دیتا بین محدودههای مختلف کلاک ممکن است باعث مختل شدن کار سیستم و پاسخهای تصادفی در خروجی شود.

این آموزش دارای دو بخش کلی است. تمامی توضیحاتی که در این آموزش ارائه میشود مبتنی بر تراشهها و ابزارهای شرکت Xilinx است.

- بخش اول پیش زمینه: در این بخش تعاریف و اطلاعات مقدماتی برای درک بهتر مفاهیم اصلی را ارائه میدهیم.

- بخش دوم تکنیکهای سنکرون سازی: در این بخش مروری بر مهمترین تکنیکهای سنکرون سازی سیگنالها بین دو محدوده کلاک در FPGA خواهیم داشت.

پیش زمینه

دو مفهوم بسیار مهم که لازم است قبل از شروع بحث اصلی یاد بگیریم عبارتند از:

- محدوده کلاک (Clock Domain)

- عدم قطعیت در پایداری یا پایداری ناقص یا شبه پایداری (Meta-Stability)

محدوده کلاک

محدوده کلاک به بخشی از طرح پیاده سازی شده گفته میشود که با یک کلاک خاص کار میکند و این کلاک به لحاظ فاز، فرکانس و یا هر دو با سایر کلاکهای موجود در سیستم متفاوت است. برای مثال، یک کلاک و بافرهای کلاکی که در مسیر آن قرار دارند و همین طور فلیپ فلاپها و سایر عناصر سنکرونی که از این کلاک استفاده میکنند همگی یک محدوده کلاک را میسازند. در نقطه مقابل کلاکهایی با فرکانسهای 55MHz و 100MHz در نظر بگیرد که فاز آنها به شکل مداوم نسبت به هم تغییر میکند. اصطلاحاً این دو کلاک متعلق به دو محدوده کلاک متفاوت هستند. طبیعتاً عناصر سنکرونی که با این دو کلاک تغذیه میشوند نیز متعلق به دو محدوده کلاک متفاوت هستند.

پس به عنوان جمع بندی بار دیگر تأکید میکنیم که تعدادی عنصر سنکرون که با یک کلاک مشترک کار میکنند یک محدوده کلاک میسازند. در صورتی که در مدار ما چندین کلاک متفاوت به لحاظ فاز و فرکانس وجود داشته باشد. محدودههای کلاک متعددی ایجاد میشود.

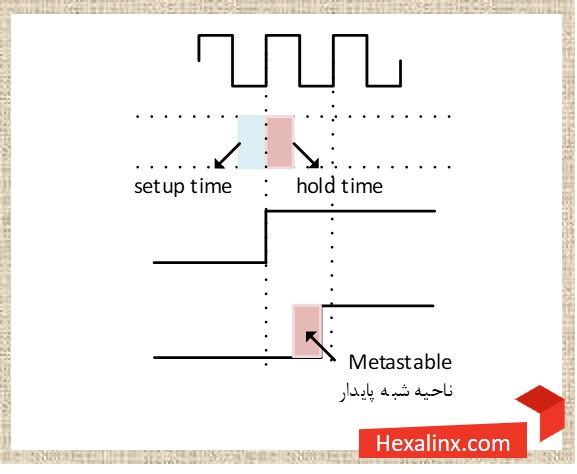

شبه پایداری

با توجه به اینکه مدارات پیاده سازی شده ما باید به صورت یکپارچه کار میکند، از این رو با توجه به تعریف فوق، انتقال مداوم دیتا بین این محدودههای کلاک اجتناب ناپذیر است. اگر یک سیگنال در دو محدوده کلاک استفاده شود یا به بیان ساده تر دیتا بین دو محدوده کلاک دست به دست شود در این صورت ممکن است پدیده شبه پایداری یا Meta-Stability رخ دهد و یک عدم قطعیت در مقدار دیتا اتفاق بیافتد. پدیده Meta-Stability اصطلاحاً حالتی است که در آن تعیین قطعی یک یا صفر بودن سیگنال امکان پذیر نیست و سیگنال در بازه زمانی گذر از حالت low به حالت high قرار دارد. در این چنین شرایطی خروجی برای یک لحظه بین ‘0’ و ‘1’ باقی میماند، (برای مثال در یک سیستم با ولتاژ ۵ ولت، خروجی ممکن است برای مدت زمان خیلی کوتاهی مثلاً چند نانو ثانیه حدود ۲/۵ ولت باشد. شبه پایداری باعث ایجاد اثرات جدی و منفی بر روی عملکرد سیستم میشود از همه بدتر اینکه، تکرار پذیری این حالت شبه پایدار تقریباً غیر ممکن است و بنابراین پیدا کردن منشأ خطا و برطرف کردن آن کاری بسیار سخت است.

پدیده Meta-Stability اصطلاحاً حالتی است که در آن تعیین قطعی یک یا صفر بودن سیگنال امکان پذیر نیست و سیگنال در بازه زمانی گذر از حالت low به حالت high قرار دارد. در این چنین شرایطی خروجی برای یک لحظه بین ‘0’ و ‘1’ باقی میماند.

تکنیکهای سنکرون سازی

به صورت کلی هدف اصلی تکنیکهای سنکرون سازی مراقبت از دیتا در زمان انتقال از یک محدوده کلاک به محدوه دیگر است. رعایت دقیق ملاحظات پیاده سازی با توجه به ماهیت دیتا و شرایط دو محدوده کلاک نسبت به یکدیگر نیاز به کمی تجربه و تکرار دارد. یک مدار سنکرون ساز به مداری اطلاق میشود که در مرز بین دو محدوده کلاک قرار میگیرد و عملیات تبادل سیگنال بین دو محدوده کلاک را مدیریت میکند. در ادامه مرسوم ترین روشهایی که برای سنکرون سازی دیتا بین دو محدوده کلاک مورد استفاده قرار میگیرد به شکل کوتاه معرفی میشود.

- سنکرون سازی با m فلیپ فلاپ

- سنکرون سازی با مالتی پلکسر

- سنکرون سازی با سیگنال هندشیک

- سنکرون سازی با بافر آسنکرون

- سنکرون سازی با مدار تغییر وضعیتی

- سنکرون سازی با ابزارها و Xilinx Primitives

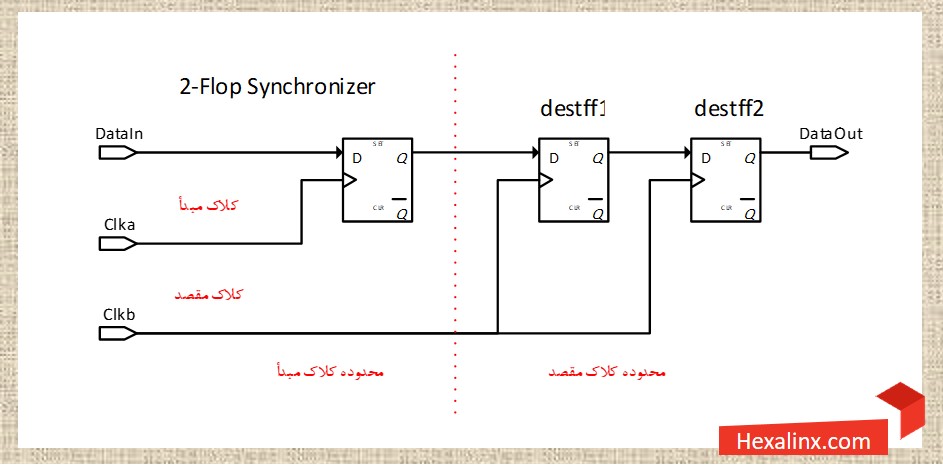

۱) سنکرون سازی m فلیپ فلاپی

در صورت برآورده شدن دو شرط زیر، میتوان از این تکنیک استفاده کرد.

- فرکانس کاری در محدوده کلاک مبدأ کمتر از محدوده کلاک مقصد باشد، یعنی کلاک مبدأ آهسته تر از کلاک مقصد باشد.

- سیگنالی که بین دو ناحیه کلاک منتقل میشود از جنس سیگنالهای کنترلی باشد. توجه شود که تعداد بیتهای سیگنال اهمیتی ندارد.

بعد از اطمینان از برقراری هر دو شرط با رعایت موارد زیر شما به عنوان یک طراح میتوانید از دست نرفتن دیتا در محدوده کلاک مقصد را تضمین کنید. به این ترتیب دادهها بدون هیچ کم و کاستی توسط کلاک سریعتر در مقصد رجیستر میشوند.

ایده کلی به این شکل است که دو فلیپ فلاپ در محدوده کلاک مقصد به صورت متوالی روی سیگنال قرار میدهیم. به این ترتیب سیگنال زمان کافی برای پایدار شدن و کاهش اثرات منفی ناشی از پدیده شبه پایداری را خواهد داشت. در جوامع پیاده سازی این تکنیک تحت عنوان Double Flopping نیز شناخته میشود. البته این ایده میتواند گسترش داده شود به جای دو فلیپ فلاپ از m فلیپ فلاپ استفاده شود. با استفاده از m فلیپ فلاپ شرایط کمی سخت گیرانه تر میشود، زیرا این بار به جای دو کلاک باید سیگنال ورودی به فلیپ فلاپ m-ام به اندازه m+1 کلاک پایدار باقی بماند.

اما برای محکم کاری بهتر است یک اقدام کوچک دیگر نیز انجام دهید و به صورت مستقیم در کد VHDL از attribute های زیر استفاده کنید.

attribute ASYNC_REG : string; attribute ASYNC_REG of destff1 : signal is ”TRUE”; attribute ASYNC_REG of destff2 : signal is ”TRUE”;

با استفاده از این attribute ها به ابزار پیاده سازی پیغام میدهید که این دو فلیپ فلاپ را تا حد امکان نزدیک به هم پیاده سازی کند.

در مواردی که سیگنال کنترلی ما بیش از یک بیت است (باس چند بیتی)، پیشنهاد میشود از تعداد بیشتری فلیپ فلاپ استفاده بشود. ذکر این نکته ضروری است با رعایت ملاحظات CDC تنها رجیستر شدن صحیح دیتا تضمین میشود و نه صحت و درستی خود دیتا. استفاده از کدینگ گری (Gray) روی سیگنالهای کنترلی میتواند ضریب اطمینان بالاتری را به همراه داشته باشد. کدینگ گری نقشی کلیدی در طراحی بافرهای آسنکرون دارد زیرا فاصله همینگ بین تغییرات متوالی سیگنالهای کنترلی همواره یک بیت است و در زمان تغییر وضعیت سیگنال حالتهای غیر مجاز ایجاد نمیشود. خب تا همین جا کافی است به سراغ تکنیک بعدی برویم.

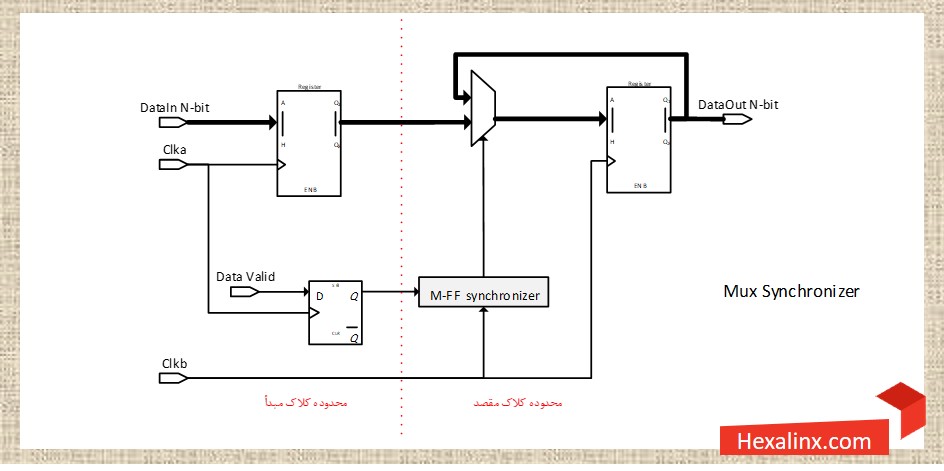

۲) سنکرون سازی مالتی پلکسری

برای استفاده از این تکنیک باید سه شرط زیر برقرار باشند.

- کلاک مبدأ از کلاک مقصد آرام تر باشد.

- سیگنال انتقالی یک باس داده چند بیتی باشد.

- دیتا حداقل برای m+1 کلاک پایدار و ثابت باشد.

به منظور درک بهتر موضوع به شکل زیر دقت کنید.

استفاده m فلیپ فلاپ برای سنکرون سازی ممکن است منجربه کجی دیتا در زمان شود. این باعث میشود فلیپ فلاپ مقصد دیتای نادرستی را رجیستر کند. سنکرون سازی مالتی پلکسری یک راه حل خوب برای حل این مشکل است. در این روش با استفاده از یک مالتی پلکسر زمان مناسب برای رجیستر کردن به فلیپ فلاپ مقصد اطلاع داده میشود. به بیان ساده تر در این روش یک سیگنال فعال ساز کلاک تولید میشود و با استفاده از آن دیتا در نقطه مناسبی با کلاک مقصد رجیستر میشود. ذکر این نکته ضروری است که پدیده کجی دیتا در زمان با پدیده کجی کلاک کاملاً متفاوت است و نباید با هم اشتباه گرفته شوند. خب بحث در رابطه با سنکرون سازی مالتی پلکسری را میتوانیم کمی گسترش دهیم و تکنیک بعدی که بر مبنای استفاده از سیگنال هندشیک است را معرفی کنیم.

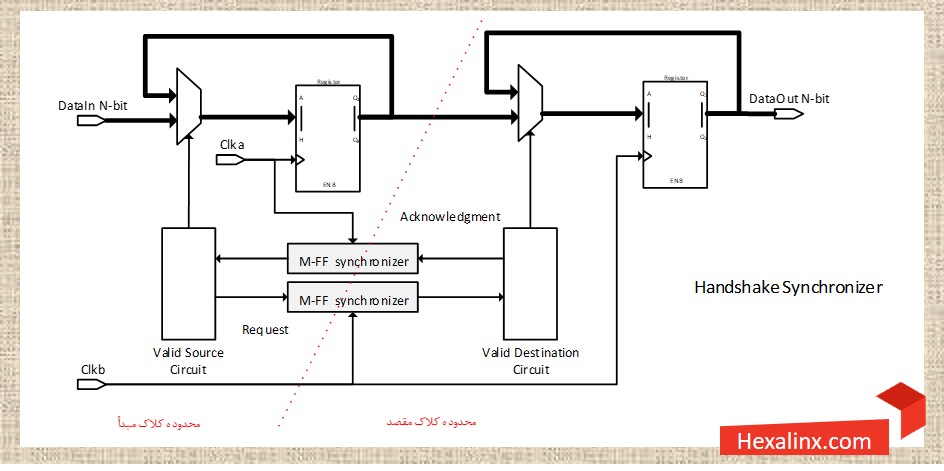

۳) سنکرون سازی با سیگنال هندشیک

همچون تکنیک قبلی برای استفاده از این تکنیک نیز باید سه شرط زیر برقرار باشند.

- کلاک مبدأ از کلاک مقصد آرام تر باشد.

- سیگنال انتقالی یک باس داده چند بیتی باشد.

- دیتا حداقل برای m+1 کلاک پایدار و ثابت باشد.

در واقع سیگنالهای هندشیک ما یک تعمیم هوشمندانه از سنکروسازی مالتی پکسری هستند. خطوط کنترلی اضافه برای درخواست و تصدیق یا تأییده عملیات تبادل داده هستند.

عملکرد کلی این مدار به این صورت است که:

ابتدا کلاک مبدأ دیتا را در فلیپ فلاپ مبدأ لچ میکند و سپس یک سیگنال درخواست به سمت محدوده کلاک مقصد ارسال میشود. این سیگنال درخواست از m طبقه سنکرون سازی فلیپ فلاپی عبور میکند و در محدوده کلاک مقصد به سلامت رجیستر میشود. رجیستر شدن یا لچ شدن دیتا در محدوده کلاک مقصد در اولین کلاک بعد از پایدار شدن سیگنال درخواست در این محدوده انجام میشود. در ادامه بلافاصله یک سیگنال تأییده به عنوان پاسخ به سمت محدوده کلاک مبدأ ارسال میشود. در آخرین گام نیز داده جدید به محض دریافت شدن سیگنال تأییده روی باس قرار داده میشود.

مکانیزمی که توصیح آن ارائه شد، یک مکانیزم استاندارد است و تمامی پروتکلهایی که از هندشیک استفاده میکنند کمابیش مشابه هستند. در این پروتکلها فرستنده بعد از ارسال دیتا به گیرنده پیام مبنی بر آماده بودن دیتا ارسال میکند و گیرنده هم بعد از دریافت دیتا تأییده آن را به عنوان پاسخ به سمت فرستنده ارسال میکند.

استفاده از سیگنالهای هندشیگ (درخواست و پاسخ) مشکلات ناشی از صفر و یک شدنهای متعدد در دیتا را از بین میبرد و ضریب اطمینان پیاده سازی را به شدت بالا میبرد.

۴) سنکرون سازی با بافر آسنکرون

روش بسیار مناسب و پرکاربرد دیگر برای سنکرون سازی باسها چه از نوع دیتا و چه از نوع کنترل استفاده از بافرهای آسنکرون (Asynchronous FIFO) است. بافرهای آسنکرون دارای دو کلاک مستقل هستند. اگر محدوده کلاک مبدأ را محدوده کلاک نوشتن و محدوده کلاک مقصد را محدوده کلاک خواندن در نظر بگیریم، دیتا در محدوده کلاک نوشتن به درون بافر تزریق میشود و در محدوده کلاک خواندن از بافر حذف میشود. از آنجایی که عملیات نوشتن و خواندن کاملاً مستقل از هم انجام میشود، استفاده از این روش همواره مناسب است و یک راه کاملاً امن برای غلبه بر مشکلات CDC در هنگام گذر بین محدودههای کلاک است.

در بافرهای آسنکرون از دو اشاره گر در محدوده نوشتن و خواندن استفاده میشود. این اشاره گرها شمارندههایی برای کنترل آدرس حافظه دو پورت مورد استفاده درون بافر هستند. این شمارندهها از نوع گری هستند و سنکرون سازی با m فلیپ فلاپ روی آنها اعمال میشود. استفاده از شمارندههای گری در بافرهای آسنکرون سلامت کامل فرایند انتقال دیتا را تضمین میکند.

البته نیازی نیست ذهنتان را درگیر جزیئات طراحی این بافرها بکنید. با استفاده از IP Core های Xilinx در محیط توسعه ISE و همینطور محیط توسعه Vivado به راحتی میتوانید یک بافر آسنکرون را درون مدار فراخوانی و سپس پیاده سازی کرد. انتخاب دیگر برای شما استفاده از Primitive هایست که در ادامه به شما معرفی میکنیم.

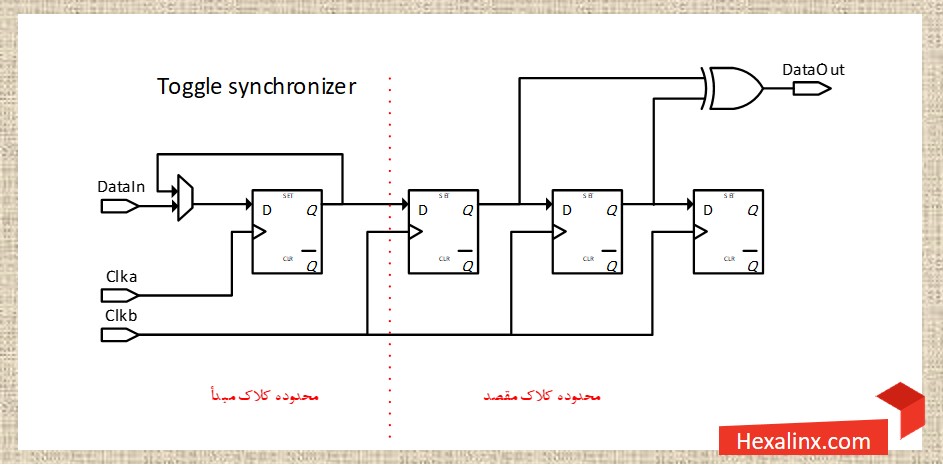

۵) سنکرون سازی تغییر وضعیتی

این تکنیک تنها زمانی که دو شرط زیر برقرار باشند کاربرد دارد.

- کلاک مبدأ از کلاک مقصد سریعتر باشد.

- سیگنال انتقالی یک سیگنال کنترل تک بیتی باشد.

همانطور که احتمالاً متوجه شدهاید، این بار شرایط کمی متفاوت است. شما یک سیگنال کنترلی تک بیتی دارید که عرض پالس آن کوتاه است و قصد دارید آن را با کلاک کندتر در مقصد رجیستر کنید. ناگفته پیداست که در این حالت استفاده از m طبقه سنکرون سازی فلیپ فلاپی راه حل مناسبی نیست و به احتمال فراوان شما موفق به انجام این کار نمیشوید. زیرا پالس سریع شما توسط لبه کلاک مقصد قابل مشاهده نیست. مدار سنکرون ساز تغیر وضعیتی مداری است که برای سنکرون سازی پالس تولیدی در محدوده کلاک سریعتر در محدوده کلاک کندتر استفاده میشود. در شکل زیر مدار سنکرون ساز تغییر وضعیتی قابل مشاهده است.

عملکرد این مدار به این صورت است:

عرض پالس کوتاه در فلیپ فلاپ اول یک سیگنال کنترلی طولانی تر در فلیپ فلاپ دوم میسازد. در ادامه این سیگنال از یک مدار تشخیص لبه در محدوده کلاک مقصد عبور داده میشود تا در نهایت با استفاده از آن یک کلاک پالس عریض تر تولید شود. هدف اصلی این مدار کشیدن یا طولانی کردن پالس کوتاه در مبدأ به اندازهای است که کلاک مقصد قادر به مشاهده و رجیستر کردن آن شود.

این مدار به نوعی دوگان مدار سنکرون ساز m فلیپ فلاپی است و با تعمیم آن میتوان مدارهای کامل تر و قابل اطمینان تری برای انتقال باسهای داده و باسهای کنترلی از محدوده کلاک سریعتر به محدوده کلاک کندتر طراحی کرد.

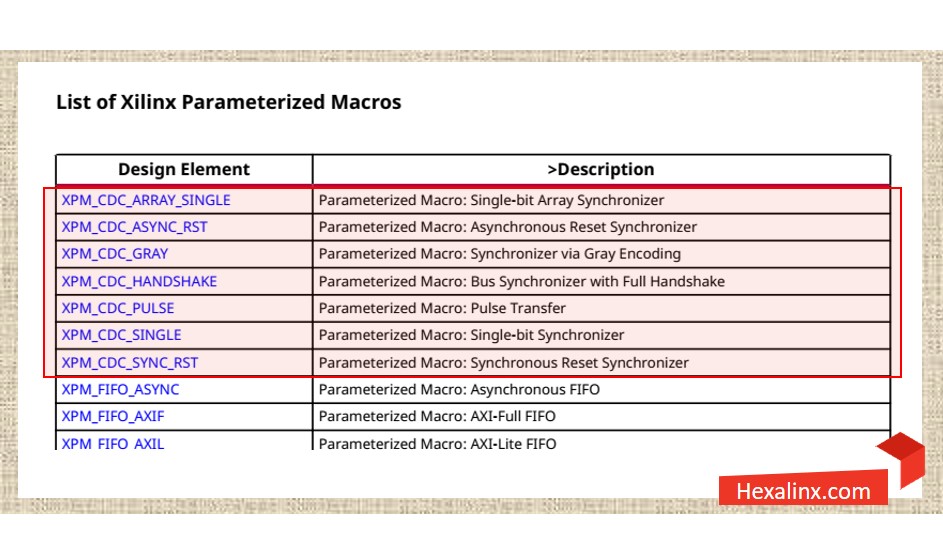

۶) سنکرون سازی با Xilinx Primitives

علاوه بر تمامی مداراتی که معرفی شد، یکسری ابزارهای CDC اختصاصی توسط Xilinx ارائه شده است که بسیار کارامد هستند.

درون تراشههای Xilinx یکسری Primitive وجود دارد که به سادگی میتوانند برای مراقبت از پدیده CDC به کار گرفته شوند. این XPM CDC Primitive ها با مراجعه به بخش language template در محیط توسعه Vivado قابل فراخوانی و استفاده هستند. این Primitive ها به نوعی یک میانبر برای فراخوانی مدارات سنکرون ساز هستند و شما به عنوان یک طراح میتوانید بعد از آنالیز شرایط و انتخاب تکنیک مناسب سنکرون سازی از یکی از گزینههای زیر در پیاده سازی خودتان استفاده کنید.

- سنکرون ساز آرایه تک بیت Single-bit Array Synchronizer

- سنکرون ساز ریست آسنکرون Asynchronous Reset Synchronizer

- سنکرون سازی با کدینگ گری Synchronizer via Gray Encoding

- سنکرون ساز باس با پیکره بندی کامل هندشیک Bus Synchronizer with Full Handshake

- سنکرون سازی پالسی Pulse Transfer

- سنکرون ساز تک بیت Single-bit Synchronizer

- سنکرون ساز ریست سنکرون Synchronous Reset Synchronizer

برای اطلاعات بیشتر در این زمینه میتوانید به مستندات Xilinx یا مقاله فراخوانی حافظهها و عناصر سنکرون ساز کلاک مراجعه بفرمایید.

جمع بندی

وقتی صحبت از سنکرون سازی و مقابله با پدیده CDC به میان میآید، استفاده از ساده ترین راه برای دستیابی به نتیجه مطلوب همواره در اولویت است. به شرطی که طراح احاطه کامل بر مشکل و آشنایی کافی با اصول سنکرون سازی داشته باشد. بخاطر داشته باشید که شما مجبور نیستید چرخ را ابتدا اختراع کنید. بسیاری از چالشهایی که در پیاده سازی وجود دارند با چند جستجوی دقیق در اینترنت و صرف زمان کافی قابل حل هستند. تکنیکهای سنکرون سازی دیتا که در این آموزش معرفی شد، سالها در جوامع پیاده سازی تست شده و توسط متخصصان در این حوزه بروزرسانی شدهاند. اگر از Vivado و تراشههای سری ۷ برای طراحی استفاده میکنید به شما پیشنهاد میکنیم بعد از مطالعه کامل این آموزش به شکل ویژه روی Primitive های Xilinx تمرکز کنید. زیرا این Primitive ها شالودهای از تمامی مدارات سنکرون ساز معرفی شده را در اختیار شما میگذارند.

منبع: Xilinx ، hardwarebee

2 در مورد “تکنیکهای سنکرون سازی در FPGA”

بسیار مفید بود

متشکرم

از اینکه نظرتون و با ما به اشتراک گذاشتید، سپاسگزارم.