مقدمه

در قسمت اول یک معرفی کوتاه از نحوه دسته بندی بلوکهای ورودی/خروجی درون بانکها ارائه شد و در ادامه مفهوم SelectIO ها توضیح داده شد. در مورد انواع بانکها و دو کلاس HP و HR توضیحاتی ارائه گردید و در نهایت یک ویژگی بسیار مهم در منابع ورودی و خروجی FPGA به نام امپدانس قابل کنترل دیجیتال معرفی شد. در قسمت دوم بخش منطقی منابع ورودی/خروجی را که دقیقا پشت بخش الکتریکی قرار گرفتهاند، معرفی میکنیم. اگر هنوز قسمت اول مقاله را مطالعه نکردید پیشنهاد میکنم ابتدا این مقاله را مطالعه بفرمایید و سپس با ما همراه شوید.

در طول این مقاله هر جا که از پینهای تراشه صحبت به میان میآوریم، منظور پینهای فیزیکی تراشه و بخش الکتریکی متصل به آن است. چون پل ارتباطی میان پینهای فیزیکی تراشه و بخش منطقی ورودی/خروجیها دقیقا همین بخش الکتریکی است.

بخش منطقی منابع ورودی/خروجی

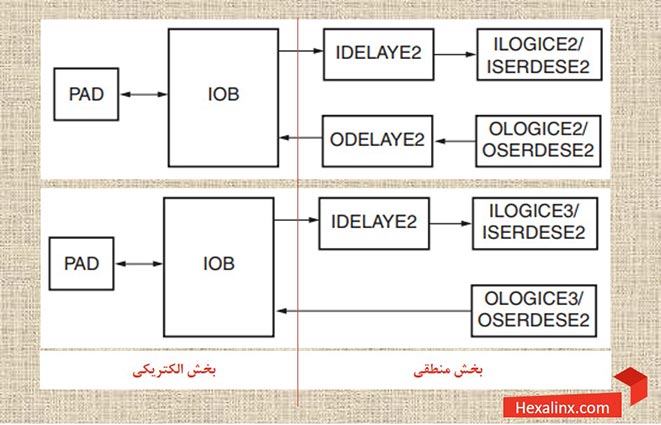

بسیاری از ویژگیهای بخش منطقی در منابع ورودی/خروجی تراشههای سری ۷، مشابه نسلهای قبلی است. همانطور که در قسمت اول اشاره شد، بخش منطقی دقیقاً پشت سر بخش الکتریکی منابع ورودی/خروجی قرار گرفتهاند. به طور خلاصه بخش منطقی متشکل از ۵ واحد است.

- واحدهای منطقی ورودی یا ILOGIC

- واحدهای منطقی خروجی یا OLOGIC

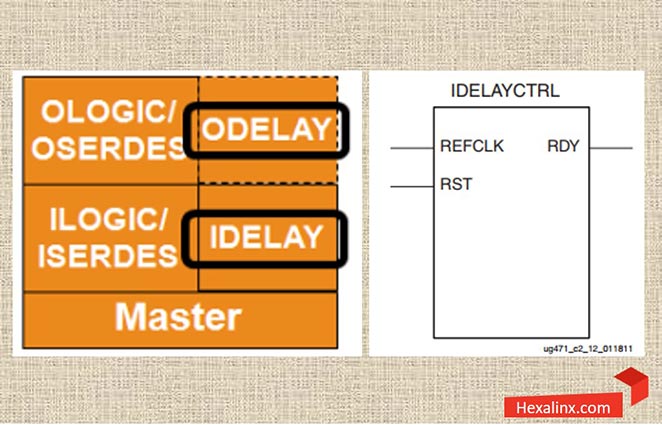

- واحدهای تاخیر یا IDELAY و ODELAY

- واحد پیشرفته سریالایزر/دی سریالایزر ورودی یا ISERDES

- واحد پیشرفته سریالایزر/دی سریالایزر خروجی یا OSERDES

واحدهای منطقی ورودی

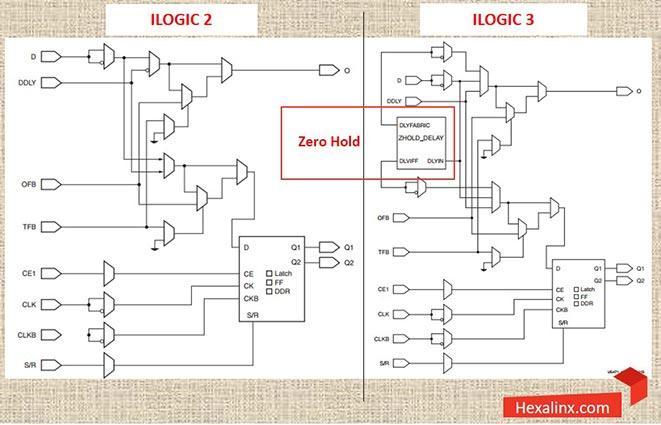

واحد منطقی ورودی ILOGIC در پیشانی بخش منطقی قرار دارد. هر واحد منطقی ورودی متشکل از تعدادی فلیپ فلاپ، بافر و مدارات کنترلی میباشد. یعنی این واحدها در برگیرنده عناصر سنکرون برای نمونه برداری از دیتای ورودی هستند. دیتاها روی پینهای تراشه قرار میگیرند و بعد از گذر از بخش الکتریکی، به درون تراشه هدایت میشوند. دو نوع واحد منطقی ILOGIC در تراشههای سری ۷ وجود دارد.

- بانکهای HP با استفاده از واحدهای ILOGIC2 و

- بانکهای HR با استفاده از واحدهای ILOGIC3 پیکرهبندی میشوند.

به صورت معمول هر دو واحد تحت عنون ILOGIC مخاطب قرار داده میشوند. تنها تفاوت این دو واحد مربوط به عنصر ZHOLD است. این عنصر برای کاهش اثر تاخیر اضافه شده در کاربردهایی که کلاک به همراه دیتا به سمت FPGA ارسال میشود بکارگرفته میشود. (کاربردهای Source Synchronous )

- بلوکهای ILOGIC2 در بانکهای HP عنصر ZHOLD ندارند.

- بلوکهای ILOGIC3 در بانکهای HR عنصر ZHOLD دارند.

همانطور که اشاره شد، ورودیهای ILOGIC از سمت پینهای تراشه تامین میشوند. این ورودیها ممکن است صورت مستقیم از طریق پینهای تراشه یا به صورت غیر مستقیم از طریق واحد تاخیر IDLEAY تامین شوند.

خروجیهای ILOGIC به منابع داخلی تراشه منتهی میشود. این اتصال به یکی از سه شکل زیر انجام میشود.

- به صورت مستقیم و آسنکرون (بدون کلاک) به سمت یک مدار ترکیبی

- و یا در مد SDR با لبه بالا یا پایین رونده کلاک فلیپ فلاپ داخلی

- و یا در مد DDR با هر دو لبه کلاک فلیپ فلاپ داخلی

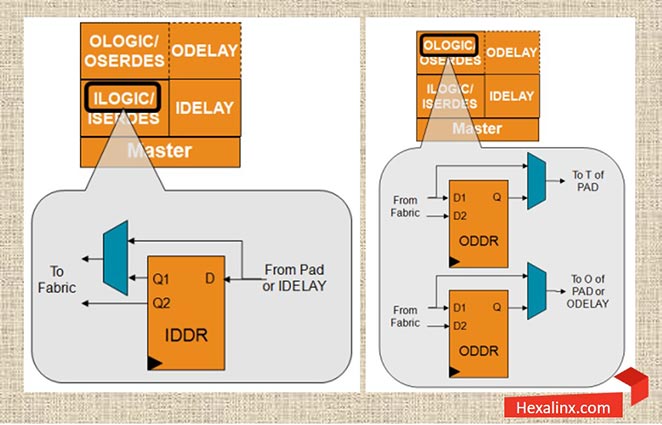

زمانی که یک ورودی به صورت مستقیم به یک LUT درون تراشه متصل میشود، یک مسیر کاملا ترکیبی شکل میگیرد. در این حالت هیچ رجیستری فراخوانی نمیشود. تقریبا تمام فرایند اتصال اتوماتیک است و توسط ابزارهای Xilinx کنترل میشود. در صورت رجیستر شدن داده ورودی و فعال بودن تنظیمات مربوط به تجمیع رجیسترها درون ورودی/خروجیها، فلیپ فلاپهای درون ILOGIC با لبه بالا رونده یا پایین رونده دادهها را ذخیره میکنند و به سمت منابع منطقی درون تراشه هدایت میکنند. بکارگیری این فلیپ فلاپها تاثیر بسزایی در بهبود زمان بندی سیستم دارد. در مواردی نیاز است دیتا با استفاده از هر دو لبه بالا رونده و پایین رونده کلاک نمونه برداری شود (مثلا در زمان اتصال به حافظههای پرسرعت خارجی یا مبدلهای آنالوگ به دیجیتال). واحد ILOGIC دارای یک عنصر ویژه به نام IDDR Primitive است که قادر به نمونه برداری در هر دو لبه کلاک است.

تنها فلیپ فلاپهایی که در تراشه FPGA قادر به نمونه برداری از سیگنال در هر دو لبه هستند درون عنصرهای IDDR و ODDR قرار دارند.

واحدهای منطقی خروجی

مشابه واحدهای ورودی ILOGIC ، واحدهای خروجی OLOGIC نیز با توجه به HR یا HP بودن بانکها به دو دسته تقسیم میشوند. بلوکهای OLOGIC3 در بانکهای HR و بلوکهای OLOGIC2 در بانکهای HP قرار دارند.

خروجی واحد OLOGIC به سمت پینهای تراشه منتهی میشود. این خروجیها به صورت مستقیم و یا از طریق واحد ODELAY به سمت پینها هدایت میشوند. ورودی واحد OLOGIC توسط منابع داخلی تامین میشود. این ورودیها ممکن است به یکی از دو شکل زیر باشند.

- به طور مستقیم، از طریق یک فلیپ فلاپ

- یا از طریق یک واحد ODDR با استفاده از هر دو لبه کلاک

هر واحد خروجی OLOGIC شامل دو عنصر ODDR است. عنصر اول برای کنترل و هدایت دادهها به صورت مستقیم به سمت پینهای دیتای خروجی است و دیگری مسئولیت کنترل پایه فعال ساز بافر سه حالته خروجی را بر عهده دارد. کلاک و ریست هر دو عنصر ODDR مشترک است. یکی از مهمترین کاربردهای ODDR ساخت یک کپی از سیگنال کلاک درون تراشه روی پینهای خروجی است. چگونه؟

هر کدام از ورودی/خروجیها میتوانند به صورت ترکیبی و یا ترتیبی (رجیستر شده) پیکرهبندی شوند. تقریبا تمام این ورودی/خروجیها از ویژگی DDR پشتیبانی میکنند و میتوانند دادهها را روی هر دو لبه کلاک مبادله کنند.

واحدهای تاخیر

تمامی بلوکهای ورودی/خروجی در تراشههای سری ۷ دارای خطوط تاخیر قابل پیکرهبندی در حداکثر ۳۲ گام هستند. با توجه به فرکانس کلاک مرجع مورد استفاده برای سلول کنترلر تاخیر یا IDELAYCTRL هر گام میتواند ۳۹ ، ۵۲ و یا ۷۸ پیکوثانیه تاخیر ایجاد کند. در عمل این تاخیرها با استفاده از واحدهای IDELAY یا ODELY پیادهسازی میشوند. تعداد گامهای تاخیر میتواند به صورت صورت ثابت یا متغیر پیکرهبندی شود. یعنی تعداد گامهای تاخیر میتواند در زمان اجرا تغییر داده شود. در حالت کلی واحد IDELAY به طراح اجازه میدهد تا یک تاخیر کنترل شده روی سیگنال ورودی به تراشه اعمال کند. میزان تاخیر روی هر پین میتواند مستقل از پین دیگر باشد. در سمت مقابل واحد ODELAY برای اعمال تاخیر روی سیگنالهای خروجی تراشه مورد استفاده قرار میگیرد. خطوط تاخیر در هر کدام از واحدهایIDELAY و ODELAY از هم مستقل هستند.

به شکل خلاصه مهمترین نکاتی که در مورد خطوط تاخیر بیان شد، به شرح زیر است:

- واحدهای IDELAY در هر دو بانک HR وHP در دسترس هستند.

- واحدهای ODELAY فقط در بانک های HP در دسترس هستند.

- عناصر خطوط تاخیر با استفاده از سلول IDELAYCTRL کالیبره میشوند، میزان تاخیر مستقل از حجم پردازش، دما و ولتاژ است.

- مقدار شمارنده گامها قابل کنترل است و میتواند مقداری بین صفر تا ۳۱ داشته باشد. شمارنده گام میتواند به صورت ثابت یا متغیر پیکرهبندی شود.

- حداقل فرکانس مرجع مورد نیاز برای عملکرد قابل اطمینان ۲۰۰ مگاهرتز است. امکان استفاده از فرکانسهای بالاتر برای تراشههای سریعتر نیز وجود دارد.

واحد ODELAY فقط در بانکهای HP در دسترس است.

تا به اینجا معماری منطقی رجیسترها درون منابع ورودی/خروجی را خدمتتان معرفی کردیم. در ادامه ویژگی پیشرفته این منابع که قابلیت سریالایز و دی سریالایز کردن دادهها ورودی و خروجی به تراشه است پوشش داده میشود.

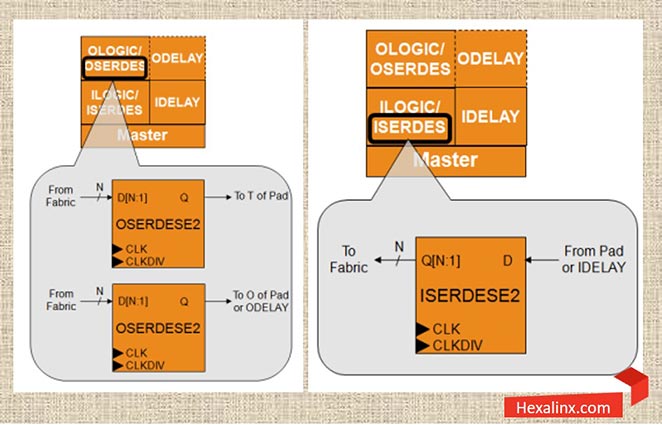

واحدهای پیشرفته سریالایزر/دی سریالایزر

در برخی از اپلیکیشنها نیاز است ترکیبی از ورودی یا خروجیهای پرسرعت سریال، به همراه باسهای موازی نسبتاً کندتر در درون تراشه به کار گرفته شوند. این کار نیازمند فراخوانی واحدهای سریالایزر و دی سریالایزر (SerDes) در بخش منطقی ورودی/خروجیها است. هر بلوک ورودی/خروجی دارای یک واحد ۸ بیتی سریالایزر/دی سریالایزر (IOSERDES) نام دارند. این واحد قادر به تبدیل سریال به موازی دادههای ورودی و تبدیل موازی به سریال دادههای خروجی در روی پینهای تراشه است.

نرخ تبدیل کاملا قابل پیکرهبندی است و میتواند ۲، ۳، ۴، ۵، ۶، ۷ و یا ۸ بیت باشد. با اتصال آبشاری دو واحد سریالایزر/دی سریالایزر در دو پین که در مجاورت هم قرار دارند امکان افزایش عرض بیتها با نرخ ۱۰ و ۱۴ نیز فراهم میگردد. علاوه بر این واحد سریالایزر/دی سریالایزر ورودی (ISERDES) از یک مد ویژه oversampling پشتیبانی میکند. این مد طراح را قادر به بکارگیری دیتا ریکاوری در برخی کاربردها میکند.

واحد سریالایزر/دی سریالایزر ورودی

در این واحد دیتای ورودی که با فرکانس بالا و به صورت سریال وارد FPGA میشود، به چند مسیر موازی که با نرخ پایین تری از کلاک کار میکنند، تقسیم میشود و به سمت منابع منطقی درون تراشه هدایت میشود.

برای روشن شدن موضوع بهتر است مثالی بزنیم. فرض کنید داده ورودی سریال با نرخ ۱ گیگا بیت بر ثانیه روی پینهای تراشه FPGA قرار دارد. این داده باید با استفاده از رجیستر درون بلوکهای ورودی/خروجی نمونه برداری شود ولی به دلیل پایین بودن نرخ کلاک درون FPGA این امر امکان پذیر نیست. حالا فرض کنید حداکثر کلاک کاری قابل استفاده درون تراشه ۲۵۰ مگاهرتز است. یعنی چهار برابر کندتر. در خوشبینانه ترین حالت اگر مدارات پیاده سازی شده در هر کلاک قادر به پردازش دادههای ورودی باشند. آنگاه از هر چهار داده ورودی سه داده از دست میرود و تنها یکی پردازش میشود. این مشکل با فراخوانی واحد سریالایزر/دی سریالایزر ورودی مرتفع میشود. با استفاده از این واحد میتوان ۴ داده سریال دریافتی را به صورت موازی در چهار مسیر مشابه با نرخ کلاک ۲۵۰ مگاهرتز به سمت منابع منطقی درون تراشه هدایت کرد.

دیتای سریال ورودی به ISERDES به صورت مستقیم از طریق پینهای تراشه یا از طریق واحد تاخیر IDELAY تامین میشود.

- پورت ورودی D با استفاده از کلاک پرسرعت (Clk) کنترل میشود.

- این ورودی میتواند SDR یا DDR باشد.

دیتای موازی شده یا دی سریالایز شده به سمت منابع داخلی درون تراشه هدایت میشود.

- پورت خروجی Q با استفاده از کلاک پایینتر (ClkDIV) کنترل میشود.

- عرض بیت این پورت با توجه به نرخ موازی سازی و نحوه نمونه برداری سیگنال ورودی تعیین میشود.

ضریب موازی سازی به یکی از دو شکل زیر است:

- در مد SDR با ضریب ۲، ۳، ۴، ۵، ۶، ۷ و ۸

- در مد DDR با ضریب ۴، ۶ و ۸

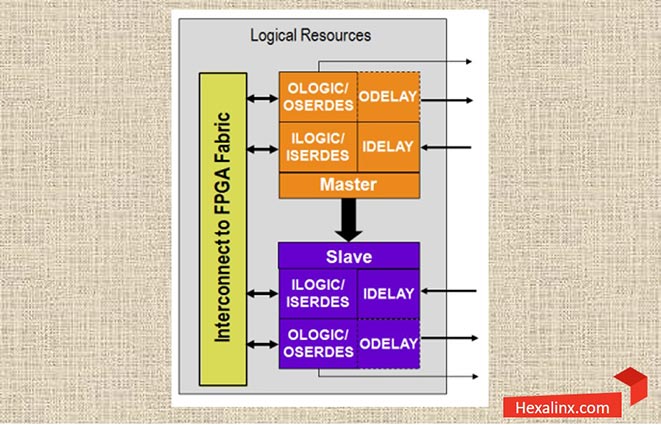

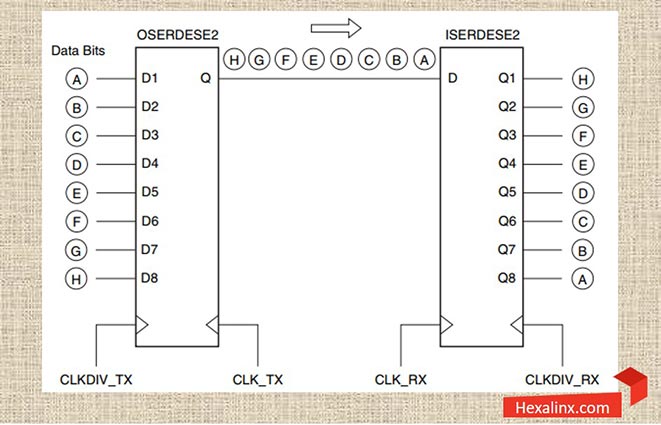

همانطور که گفته شد، علاوه بر این امکان گسترش عرض بیت پورت Q نیز وجود دارد. یعنی میتوان نرخ موازی سازی را افزایش داد. این قابلیت با اتصال آبشاری دو واحد ISERDES مجاور قابل دستیابی است. با اتصال آبشاری Master و Slave دو ISERDES ضریب موازی سازی به ۱۰ و ۱۴ در مد DDR قابل افزایش است. در نهایت آخرین نکته مهم باقی مانده در رابطه با واحد ISERDES مربوط به ماژول BITSLIP است. منبع BITSLIP برای اجرای فریمبندی روی دیتا بکار میرود و با تغییر جایگاه بیتها در باس موازی دریافتی ترتیب دادههای دریافتی را تغییر میدهد.

هر دو کلاک مورد استفاده در واحدهای سریالایزر/دی سریالایزر باید هم فاز باشند.

واحد سریالایزر/دی سریالایزر خروجی

عملکرد واحد OSERDES کاملا برعکس عملکرد واحد ISERDES است. در این واحد دادههای خروجی برای ارسال به سمت گیرندهای که نرخ بیت بالاتری نسبت به FPGA دارد به صورت سریال پشت سرهم قرار داده میشوند.

دیتای خروجی سریال شده به سمت پینهای تراشه یا ODELAY هدایت میشود. در واحد OSERDES:

- پورت خروجی Q با استفاده از کلاک پرسرعت (Clk) کنترل میشود.

- خروجیها میتوانند به صورت SDR یا DDR باشند.

دیتای موازی از سمت منابع داخلی تراشه تامین میشود.

- پورت ورودی D با استفاده از کلاک پایین تر (ClkDIV) کنترل میشود.

- هر دو کلاک مورد استفاده باید هم فاز باشند.

ضریب سریال سازی به یکی از دو شکل زیر است (در ISERDES نرخ تبدیل برای موازی سازی بیان میشد.) :

- در مد SDR با ضریب ۲، ۳، ۴، ۵، ۶، ۷ و ۸

در مد DDR با ضریب ۴، ۶ و ۸

مشابه ISERDES امکان اتصال آبشاری برای افزایش ضریب سریال سازی به ۱۰ و ۱۴ در مد DDR وجود دارد.

کلام آخر اینکه فراخوانی مدهای SDR و DDR در واحدهای IOSERDES مستقل از IDDR و ODDR درون IOLOGIC است. لازم به ذکر است، ترتیب بیتهای ورودی سریال به ISERDES دقیقاً عکس ترتیب بیتهای خروجی از OSERDES است. این مساله در شکل بالا نشان داده شده است.

جمع بندی

در قسمت اول این مقاله خصوصیات الکتریکی گیرندههای ورودی و درایورهای خروجی را بررسی کردیم. در قسمت دوم در دو بخش ابتدا معماری منطقی رجیسترها درون منابع ورودی وخروجی FPGA را معرفی کردیم و در ادامه ویژگی پیشرفته این منابع که قابلیت سریالایز و دی سریالایز کردن دادهها ورودی و خروجی به تراشه بود، پوشش داده شد. بدیهی است که بکارگیری عملی هر کدام از این واحدها و کنترل تنظیمات بلوکهای ورودی/خروجی نیازمند مطالعه دقیق دستورالعمل و دیتاشیت سازنده تراشههای FPGA است. شرکت Xilinx امکان فراخوانی و پیکرهبندی هر کدام از این واحدها را از طریق IP Core یا HDL Template فراهم آورده است. پس جای هیچ گونه نگرانی نیست، کافی است شروع کنید.

10 در مورد “از منابع ورودی و خروجی FPGA چه می دانیم؟ (قسمت دوم: منابع منطقی)”

تشکر

بسیار عالی

سایت شما خبر نامه برای اطلاع از پست هایی که جدید میگذارید دارید ؟

دوست عزیزم از همراهی شما سپاسگزارم

برای اطلاع از آخرین مقالات و مطالب منتشر شده در سایت میتوانید در کانال تلگرام یا اینستاگرام هگزالینکس عضو شوید. آدرس ما در شبکه های اجتماعی در نوار پایینی سایت قابل دسترسی هست.

با سلام

ممنون میشم در رابطه با نحوه اتصال دو واحد ISERDES و OSERDES و ترتیب تبادل بیتها بین این دو واحد بیبشتر توضیح دهید.

با سلام و احترام

خوشحالیم که این مطلب مورد توجه شما قرار گرفته، برای اتصال این دو واحد و استفاده از اونها شما باید اول مسالهای رو که میخواهید حل کنید تعریف کنید. چون با توجه به انتظاری که شما از این واحدها دارید، پیکرهبندیشون متفاوت میشه. الگوی تبادل بیتها دقیقاً مشابه همون چیزیه که تو شکل آخر مقاله توضیح داده شده.

سلام

ممنون میشم از IDDR وODDR بیشتر توضیح بدید در مقاله شکلی گذاشتید ممنون میشم توضیح بدید

با سلام و احترام خدمت شما

خب ببینید توضیح کامل IDDR و ODDR خودش نیاز به یک مقاله و آموزش جداگانه داره. اما سعی میکنم توضیح کوتاهی خدمتتون ارائه کنم.

قبل از هر چیز اجازه بدید مفهوم primitive رو باهم مرور کنیم. اصطلاح primitive به واحدهای سخت افزاری درون تراشه FPGA که توسط طراح قابلیت فراخوانی دارند اطلاق میشود. واحدهای منطقی ILOGIC و OLOGIC به صورت مستقیم داخل کد HDL و شماتیک قابل instance گرفتن و فراخوانی نیستند. پس واژه primitive به آنها اطلاق نمیشود. در نقطه مقابل IDDR و ODDR هر دو از نوع primitive هستند.

در داخل ILOGIC همانطور که در شکل هم نشان داده شده است. یک مدار کنترلی کوچک و تعدادی رجیستر یا فلیپ فلاپ وجود دارد. یکی از این رجیسترها، رجیستر DDR است که قابلیت کار با هر دو لبه کلاک در یک پریود را دارد. (توجه کنید که در حالت کلی رجیسترها تنها قابلیت کار با یکی از دو لبه کلاک را در یک پریود دارند.) این رجیستر DDR درون IDDR primitive و در داخل ILOGIC قرار دارد. IDDR primitive سه مد کاری متفاوت دارد. برای اطلاعات بیشتر در رابطه با مدهای کاری پیشنهاد میکنم به مراجع مراجعه کنید.

مشابه ILOGIC، واحد منطقی OLOGIC هم از مدارت کنترلی و عناصر سنکرون حافظه یعنی فلیپ فلاپها ساخته شده است. در کنار فلیپ فلاپ OFD که تنها با یک لبه کار میکند .یک فلیپ فلاپ DDR درون ODDR primitive وجود دارد که با هر دو لبه کلاک قابل تحریک است، و از ان برای خروجی کردن یک سیگنال سنکرون به صورت dual data rate استفاده میشود. یکی از مهمترین کاربردهای ODDR ساخت یک کپی از کلاک درون تراشه روی پینهای خروجی FPGA است. این کار اصطلاحا clock forwarding نام دارد. این primitive دو مد کاری متفاوت دارد.

امکانش هست از ZHold بیشتر توضیح دهید؟

به طور خلاصه بلوک ZHOLD برای کاهش اثرات ناشی از تاخیر کلاک درون تراشه استفاده می شود.

در مباحث مربوط به زمان بندی در FPGA بررسی ملاحظات hold time ضروری است، با استفاده از ZHOLD بخشی از ملاحظات مورد نیاز به صورت اتوماتیک اصلاح می شود و مسیرهای کلاک و دیتا با هم تراز می شوند.

سلام ممنون از مطالب خوب و مفیدتون

جسارتا منظور از کلمه fabric در fpga fabric چیست ؟

و امکانش هست در رابطه با master و slave توضیح بدید؟

با تشکر

با سلام،

منظور از fabric منابع داخلی خود تراشه هست، یعنی بلوکهای حافظه RAM، بلوکهای ضرب کننده DSP، و بلوکهای منطقی LUT و …

اما در مورد master و slave

موضوع یک مقدار پیچیده تر هستش، ساختار master و slave فقط زمانی که ورودی یا خروجی به صورت تفاضلی باشد معنی پیدا می کند، یک بلوک کمکی ISERDES و یا OSERDES به بلوک اصلی master اضافه می شود و امکان بالارفتن نرخ تبدیل و فراهم می کند. این بلوک کمکی slave هست و براساس پیکره بندی بلوک اصلی بصورت اتوماتیک فراخوانی می شود.

این بلوک اضافی در حالتی که پورت ها به صورت تک سیمه پیکره بندی بشوند اصلا فراخوانی نمی شود و کاربرد ندارد.