مقدمه

معمولاً مقایسه و بررسی حالتهای مختلفِ نیل به یک هدف واحد هم برای خوانندگان و هم برای خود نویسنده (گان) دارای جذابیت است. در این نوشتار از پایگاه دانش هگزالینکس به سراغ مایکروبلیز رفتیم تا این بار نحوه چیدمان و ساختار منابع حافظه را برای این هسته پردازشی نرم افزاری بررسی کنیم. ما در این مقاله برخی از مهمترین نکات را در رابطه با معماری حافظه در مایکروبلیز، بیان خواهیم کرد.

به طور کلی به دلیل ماهیت انعطاف پذیر تراشههای FPGA ، هسته پردازشی نرم افزاری مایکروبلیز (MicroBlaze) را میتوان با استفاده از پیکربندیهای مختلف حافظه پیاده سازی کرد. از آن جمله میتوان به حافظههای کاملاً تجمیع شده محلی (Local Memory)، و یا حافظه های بلوکی (block RAM) در داخل تراشه FPGA و همینطور حافظههای جانبی همچون DDR SDRAM، SRAM و حتی QSPI NOR Flash در خارج از تراشه اشاره کرد.

حافظه انتخابی از هر نوعی که باشد، به استثناء حافظههای محلی، هم میتواند به صورت اختصاصی و هم به صورتی اشتراکی برای مایکروبلیز مورد استفاده قرار بگیرد، به عبارت ساده تر میتواند با یک بلوک Master DMA دیگر به اشتراک گذاشته شود. صد البته در همه موارد، مهندس پیاده ساز میتواند حافظه کَشِ جداگانهای برای دادهها و دستورالعملها به طرح خودش اضافه کند. تقریباً تمام حالات ممکن را میتوان به سه دسته تقسیم کرد که در ادامه مورد بحث قرار میگیرند، بعلاوه یک حالت چهارم که روی قابلیت به اشتراک گذاری حافظه تمرکز میکند. توجه به این نکته مهم است که در عمل الزامی به استفاده انحصاری از یکی از این دستهها وجود ندارد و اجرای هر سه به طور همزمان در یک سیستم کاملاً امکان پذیر است.

حافظه محلی

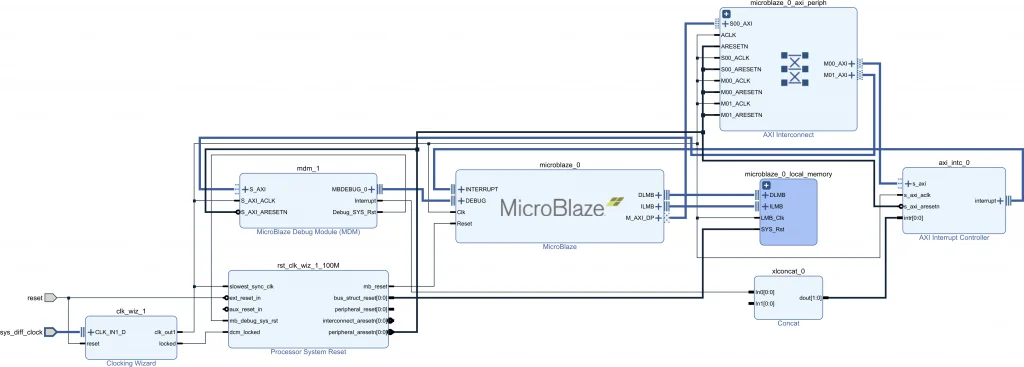

مایکروبلیز میتواند از طریق یک اینترفیس اختصاصی، به نام Local Memory Bus – LMB که دارای تأخیر دسترسی بسیار کم میباشد حافظههای داخلی تراشه را به شکل خاصی فراخوانی کند. این حافظههای داخلی در عمل با استفاده از block RAM ها ساخته می شوند اما به دلیل نوع اینترفیسی که برای دسترسی به آن استفاده میشود، حافظههای محلی یا Local Memory نامیده میشوند. همانطور که در بلوک دیاگرام زیر نشان داده شده است، در ساده ترین شکل ممکن، مایکروبلیز حداقل دارای سه اینترفیس خارجی است. اینترفیس M_AXI_DP پورت داده پریفرال است که مایکروبلیز از آن برای دسترسی به رجیسترهای مختلف پریفرالهای متفاوت استفاده میکند. دو اینترفیس دیگرکه DLMB و ILMB نام دارند، به ترتیب گذرگاههای حافظه محلی برای واکشی دادهها و دستورالعمل ها توسط هسته پردازنده هستند. در حقیقت دلیل اصلی متصل شدن اتوماتیک مایکرو بلیز به حافظه محلی در Vivado به خاطر وجود همین دو اینترفیس است.

صرف نظر از نوع پیکربندی انتخابی برای حافظه، همواره مقدار کمی حافظه محلی برای ذخیره و اجرای کد بوت مایکروبلیز مورد نیاز است. با این وجود اگر حافظه محلی اختصاص داده شده به مایکروبلیز، به اندازه کافی بزرگ باشد، دادهها و دستورالعملها هم میتوانند به صورت کامل روی این حافظه داخلی ذخیره شوند. از آنجایی که دسترسی به حافظه محلی از طریق LMB تنها یک سیکل کلاک تأخیر دسترسی دارد، اجرای کامل مایکروبلیز از روی حافظه محلی نیاز به استفاده از حافظه کَش را به طور کلی منتفی میکند و در نتیجه میزان منابع مصرفی مورد استفاده توسط مایکروبلیز کاهش مییاید.

در کنار تمام مزایایی که به آن اشاره شد، حافظههای محلی دارای چندین کاستی مهم هستند. اول اینکه سایز آن ها محدود است، این مسأله حتی زمانی که تراشه FPGA انتخابی بزرگ هم باشد بازهم خودنمایی میکند، زیرا الزامات مورد نیاز برای تضمین دسترسی به حافظه در یک سیکل کلاک باعث میشود حداکثر ظرفیت حافظه قابل اتصال به اینترفیس LMB محدود شود. کاستی دوم ناشی از اختصاصی بودن حافظه محلی برای مایکروبلیز است. بدین معنا که دادههای ذخیره شده روی آن توسط یک DMA Master دیگر درون سیستم قابل دسترسی نمیباشد. حتی اگر حافظه خارجی به هر دلیلی برای کاربرد مد نظر مورد نیاز باشد، توسعه دهندگان اپلیکیشن باید همواره به خاطر داشته باشند که حافظه محلی تنها برای بخش خاصی از دادهها و کدها قابل دسترسی است. به طور کلی هر پیکربندی که برای معماری حافظهها در مایکروبلیز انتخاب شود حافظه محلی نقشی مشابه حافظههای TCM از پیش تعبیه شده روی SoC را برای مایکروبلیز ایفا میکند. واژه TCM کوتاه شده عبارت Tightly Coupled Memory است. یک مثال مناسب از این حافظهها، حافظه OCM درون پخش پردازنده تراشههای Zynq-7000 MPSoC است.

حافظه بلوکی

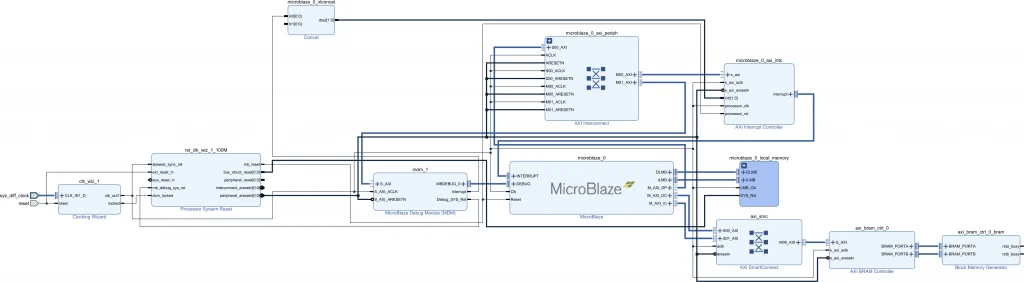

در صورتی که حافظه محلی به اندازه کافی بزرگ نباشد، یا حافظه اشتراکی مورد نیاز باشد، میتوان با اتصال حافظههای بلوکی از طریق اینترفیس AXI به مایکروبلیز، معماری حافظه را طراحی کرد. همانطور که گفته شد، در این معماری، حافظه متصل به LMB همچنان وجود دارد، زیرا برای کد بوت مورد نیاز است. در عین حال دو باس جدید با استفاده یک بلوک AXI SmartConnect به مایکروبلیز متصل شدهاند و یک فضای حافظه جدید به مایکروبلیز اضافه کردهاند. این دو باسِ جدید به اینترفیسهای (پورت) کشِ داده (M_AXI_DC) و دستورالعمل (M_AXI_IC) مایکروبلیز هستند. این دو پورت به یک بلوک AXI Interconnect متصل شدهاند و به کمک آن به تنها پورت Slave روی AXI BRAM Controller متصل شدهاند. البته این امکان وجود دارد که با استفاده از اینترفیس (پورت) پریفرال (M_AXI_DP) به حافظه block RAM متصل شد، اما این روش کارایی به مراتب کمتری دارد.

از نقطه نظر منابع در تراشههای FPGA ، این معماری بسیار مشابه معماری حافظههای محلی است که در بخش قبلی در رابطه با آن صحبت شد. تنها تفاوت آن در این است که در اینجا مایکروبلیز تنها میتواند از طریق اینترفیس AXI به این حافظه دسترسی پیدا کند. استفاده از اینترفیس AXI باعث میشود به اشتراک گذاری حافظه با سایر Bus Master ها با استفاده از بلوکهای AXI Interconnect امکان پذیر باشد.

واژههای Bus Master و DMA Master به هر بلوک یا واحد سخت افزاری اطلاق میشود که دارای یک اینترفیس Master است و میتواند کنترل کننده و شروع کننده جریان داده باشد.

با این وجود، این حقیقت که دسترسی به حافظه بایستی الزاماً از طریق بلوک AXI Interconnect انجام بپذیرد پابرجاست و این بدان معناست که تأخیر دسترسی به حافظه در مقایسه با اینترفیس LMB بیشتر است. مهمتر از همه اینکه، بروز اختلال در دسترسی اشتراکی اجتناب ناپذیر است و در نتیجه آن تأخیر دسترسی ممکن است بیشتر از براوردهای روی کاغذ باشد. به این ترتیب پهنای باند موجود برای دسترسی به حافظه کاهش مییابد. معمولاً در این پیکربندی، استفاده از حافظه کَش برای حفظ عملکرد مایکروبلیز در یک سطح قابل قبول ضروری میباشد.

زمانی که کَش به مایکروبلیز اضافه شود، مایکروبلیز هرگونه دسترسی قابل ذخیره سازی را از طریق اینترفیسهای اختصاصی و کَش شده AXI انجام میدهد. این اینترفیسها به روشهای گیج کنندهای مجوز پارتیشن بندی دستورالعملها، دادهها و صد البته فضای آدرس پریفرال را صادر میکنند.

حافظه خارجی

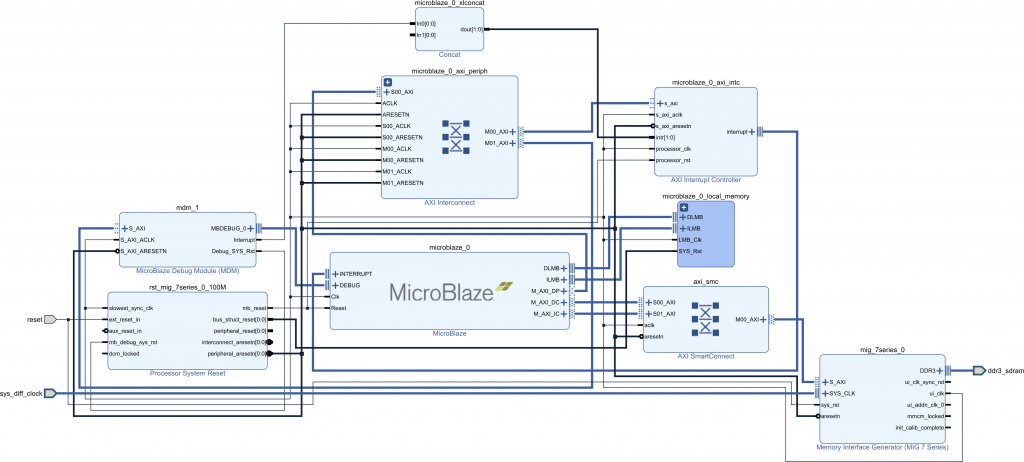

در نهایت، اگر حافظه مورد نیاز به اندازهای زیاد باشد که امکان پیاده سازی آن به شکل قابل قبول با استفاده از منابع حافظه درون تراشه امکان پذیر نباشد، در معماری حافظه باید از حافظه خارجی استفاده کرد. حافظه خارجی میتواند یک نوع RAM از نوع DDR یا SRAM و یا از نوعی حافظه غیر فرار مثل QSPI NOR Flash باشد. در بلوک دیاگرام زیر نحوه اتصال مایکروبلیز به حافظه DDR با استفاده از اینترفیس AXI و از طریق یک بلوک AXI SmartConnect نشان داده شده است.

حافظه خارجی میتواند در برگیرنده کد و داده باشد، در حالی که حافظههای غیر فرار نظیر QSPI NOR Flash تنها میتوانند کد و دادههای ثابت (فقط خواندی) باشند. به این نکته دقت شود که اگر حافظه QSPI که در مد XIP (eXecute In Place) پیکربندی شده باشد، به سادگی قابل نوشتن نیست. به این ترتیب، در صورتی که این تمایل وجود داشته باشد که کد مستقیماً درون QSPI Flash اجرا شود، و یک فایل سیستم مورد نیاز باشد، آنگاه یک حافظه غیر فعال دیگر باید به سیستم اضافه شود.

زمانی که مایکروبلیز دستورالعملها را از حافظه خارجی واکشی و اجرا میکند، خواه حافظه از نوع RAM یا ROM باشد، در هر دو حالت استفاده از کَش برای نگه داشتن راندمان در یک سطح قابل قبول اجباری به نظر میرسد. درچنین شرایطی بیشتر از اینکه در مورد لزوم استفاده از کَش صحبت شود، بیشتر در رابطه با بهینه سازی سایز کَش و نحوه پیکربندی آن برای دستیابی به حداکثر کارایی اپلیکیشن و در عین حال به حداقل رساندن منابع مصرفی روی تراشه FPGA صحبت میشود.

حافظه اشتراکی

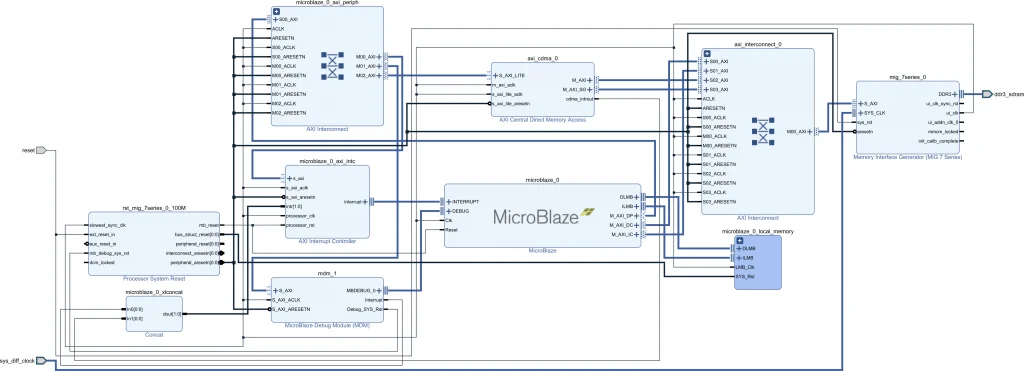

برای استفاده از حافظههای داخلی یا خارجی به صورت اشتراکی باید همراه با آنها بلوک AXI Interconnect در کنار یک یا چند Bus Master بکارگرفته شود. در غیر این صورت این حافظهها توسط Bus Master های مد نظر در دسترس نخواهند بود. به عنوان مثال، در دیاگرام زیر یک بلوک AXI Central DMA به صورت مشترک با مایکروبلیز از طریق AXI Interconnect به یک حافظه خارجی DDR متصل شده است.

همانطور که احتمالاً حدس زدهاید، ناحیه به اشتراک گذاشته شده میتواند به پورت پریفرال مایکروبلیز نیز متصل شود. البته در چنین شرایطی دسترسی به آن به صورت کَش شده نخواهد بود. این بدان معناست که هیچ عملیاتی برای نگهداری و کنترل وضعیت کَش توسط اپلیکیشن به منظور حفظ انسجام آن با حافظه اشتراکی مورد نیاز نخواهد بود. علاوه بر این دسترسی به حافظه اشتراکی از طریق پورت پریفرال از کارایی که یک دسترسی کَش شده میتواند به همراه داشته باشد، بی بهره خواهد بود.

جمع بندی

طرحهای ارائه شده در این مقاله تنها گزینههای موجود برای معماری حافظه در مایکروبلیز نیستند، اما بدون شک رایج ترین آنها هستند. اضافه کردن کامپوننتهای دیگر مانند حافظه پنهان (کَش) L2 به این معماریهای سلسله مراتبی امکان پذیر است. اما در برخی مواقع ممکن است باعث افزایش هزینه طراحی و پیچیده شدن معماری سلسله مراتبی حافظه بشود که به خودی خودی مزایا و ویژگی های منحصر به فرد تراشههای FPGA را تحت تاثیر قرار میدهد. به این ترتیب، برای متعادل کردن مناسب هزینه سخت افزار و مصرف انرژی، بهینه سازی دقیق پیکربندی حافظه مایکروبلیز با توجه به نیازهای اپلیکیشن بسیار مهم است.

منبع : jblopen.com