مقدمه

این نوشتار از پایگاه دانش هگزالینکس، به تشریح و توصیف منابع داخلی تراشههای FPGA که طراحان را در ساخت، توزیع و مدیریت کلاک در FPGA و حتی در سطح سیستم یاری میرساند، اختصاص دارد.

موارد فراوانی وجود دارد که در آن ما نیاز داریم سیگنالهای کلاک جدید تولید کنیم و به صورت مؤثر آنها را در تمام سیستم توزیع کنیم. تراشههای FPGA دارای بلوکهای اختصاصی برای مدیریت کلاک هستند و به ما این امکان را میدهد که این دو کار را انجام دهیم. در بخش اول از سری مقالات آموزشی مدیریت سیگنال کلاک با هم نگاهی به تاریخچه و سیر تکاملی بلوکهای مدیریت کلاک و یکسری از مفاهیم پایه خواهیم انداخت، و در بخش دوم در مورد شبکه توزیع کلاک در FPGA و مجموعه منابعی که برای انتشار مناسب کلاک درون تراشه مورد استفاده قرار میگیرند، به شکل مفصل صحبت خواهیم کرد.

تولید و توزیع کلاک

مروری بر منابع مدیریت کننده کلاک در FPGA

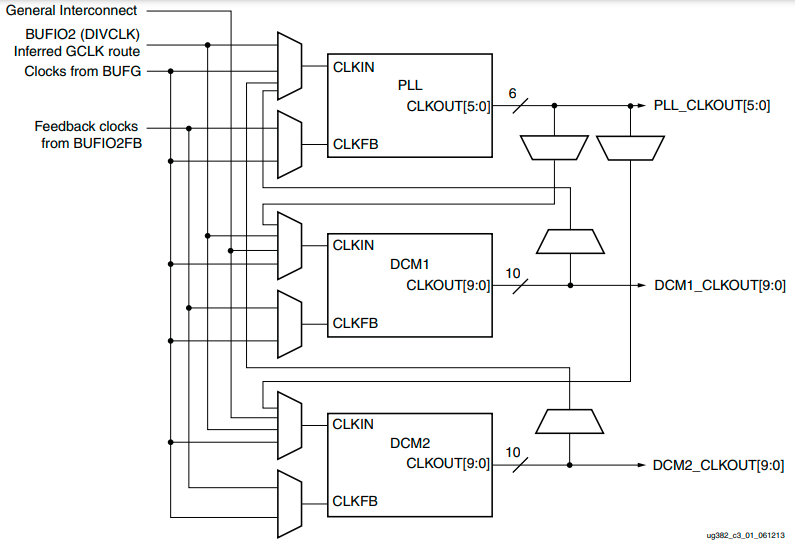

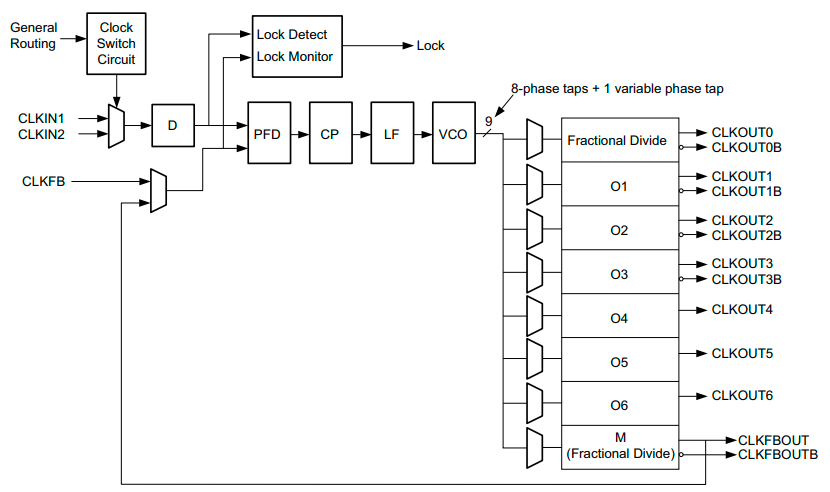

تراشههای FPGA دارای منابع و بلوکهای انعطاف پذیر و البته قدرتمندی برای مدیریت سیگنال کلاک هستند که زمان و هزینه طراحی را به شکل محسوسی کاهش میدهند. این منابع پرکاربرد در تراشههای مختلف شرکت Xilinx با عناوین متفاوتی نام گذاری شدهاند و به مررور زمان برقابلیتهای آنها افزوده شده است. معماری و ساختار سیستم تولید و توزیع کلاک در تراشههای جدیدتر شرکت Xilinx بر اساس CMT ها شکل گرفته است. واژه CMT مخفف عبارت Clock Management Tile است. به عنوان مثال هر CMT در تراشههای سری ۷ متشکل از یک بلوک Mixed Mode Clock Manager (MMCM) و یک بلوک Phased Lock Loop (PLL) است. در تراشههای Spartan-6 و تراشههای قدیمیتر این شرکت در هر CMT دو بلوک Digital Clock Manger (DCM) و یک بلوک PLL قرار دارد.

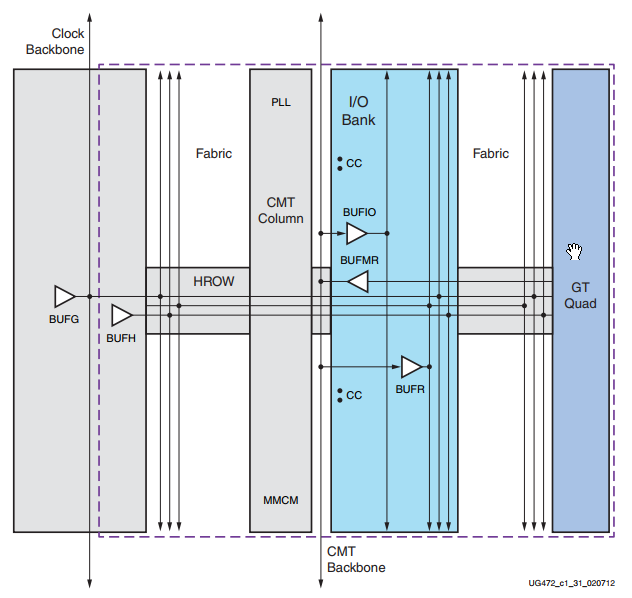

در تراشههای FPGA کلاک خارجی از طریق پینهای اختصاصی کلاک در هر بانک IO که (CC) نام دارند، وارد تراشه میشود. سپس با استفاده از بافرهای ورودی کلاک (IBUF) وارد CMT ها میشود و در نهایت از طریق شبکه کلاک درون تراشه توزیع میشود.

فرایند تولید سیگنال کلاک جدید از روی کلاک مرجع ورودی، توسط بلوکهای مدیریت کلاک با انجام عملیات ضرب و یا تقسیم روی کلاک ورودی صورت میپذیرد. بلوکهای مدیریت کلاک قادر هستند در صورت نیاز شیفت فاز قابل برنامه ریزی روی کلاک نیز اعمال کنند و یا پهنای پالس کلاک را نیز کنترل کنند. علاوه بر این بلوکهای مدیریت کلاک قادر به از بین بردن یا به حداقل رساندن پدیده کجی کلاک (clock de-skew) برای کلاکهایی که در داخل تراشه توزیع میشوند و یا کلاکهایی را که قرار است توسط قطعه دیگری روی بورد استفاده شود، میباشند.

در ادامه این بخش همراه با شما نگاهی متفاوت به تاریخچه و سیر تکاملی بلوکهای مدیریت کلاک در نسلهای مختلف تراشههای FPGA شرکت Xilinx خواهیم داشت، و مسیری را که برای دستیابی به بلوغ فعلی طی شده است، مرور خواهیم کرد.

بلوکهای DCM

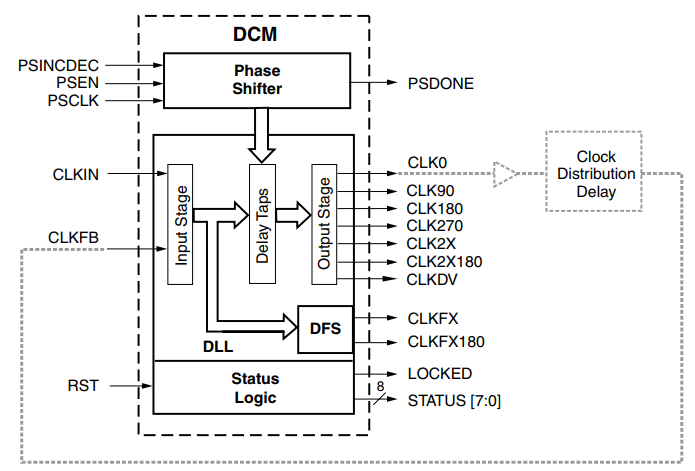

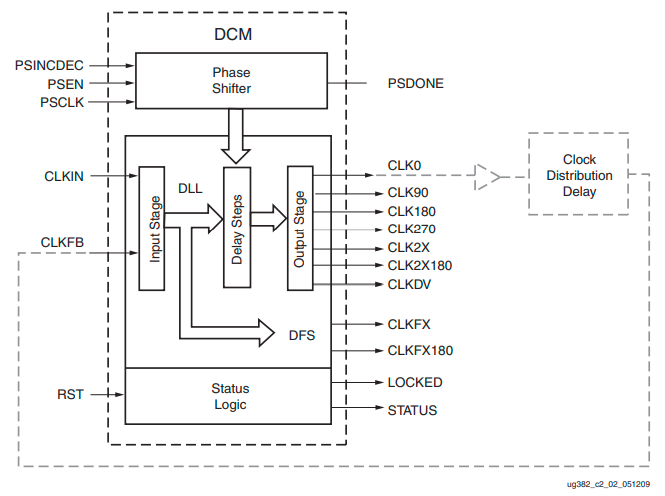

واژه DCM کوتاه شده عبارت Digital Clock Manager است و در ادبیات Xilinx که برای مخاطب قرار دادن بلوکهای مدیریت کلاک درون نسلهای قدیمی تر تراشههای FPGA بکار میرفت. در قلب این بلوکها، عناصری به نام Delay Locked Loop (DLL) قرار دارد. این بلوکها قادرند کجی کلاک را جبران کنند (clock de-skew)، فازهای متفاوتی از یک کلاک تولید کنند، به صورت دینامیک فاز کلاک را تغییر دهند، کلاکهای با فرکانس بالاتر و یا پایین تر تولید کنند و حتی در صورت نیاز کلاکهایی که هارمونیکی از کلاک اصلی ورودی هستند، تولید کنند. این عناصر تنها بلوکهای مدیریت کلاک در تراشههای FPGA تا زمان معرفی تراشههای Virtex-5 بودند (در تراشههای Virtex-2 ، Spartan-3 و Virtex-4 وجود داشتند).

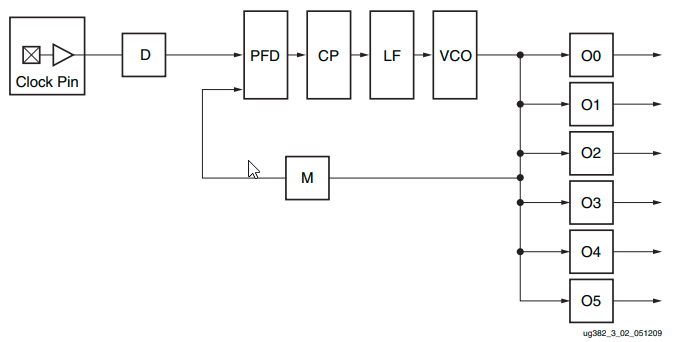

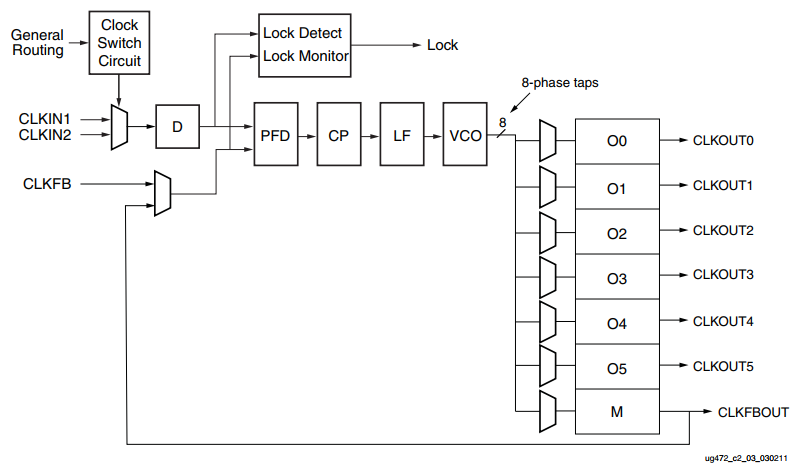

بلوکهای PLL

با معرفی تراشههای Virtex-5 و Spartan-6 بلوکهای جدیدی به نام PLL که کوتاه شده عبارت Phase Locked Loop و اصطلاحاً حلقه قفل فاز نامیده میشوند به همراه بلوکهای DCM معرفی شدند. در عمل PLL یک سلول اختصاصی آنالوگ برای مدیریت کلاک است که قادر به انجام بخش قابل توجهی از قابلیتهای DCM به جز تغییر دینامیک (پویا) و دقیق فاز است. در حالت کلی یک PLL قادر به سنتز و تولید فرکانسهای کلاک به مراتب دقیق تری نسبت به DCM است. این بلوکها میتوانند به صورت همزمان چندین فرکانس متفاوت تولید کنند، در حالی که جیتر فرکانسهای تولید شده نیز نسبت به فرکانس تولید شده توسط DCM از کیفیت بالاتری برخوردار است. این مسأله زمانی که سنتز فرکانس با ضرائب ضرب یا تقسیم نسبتاً بزرگ انجام میشود، بیشتر به چشم میآید.

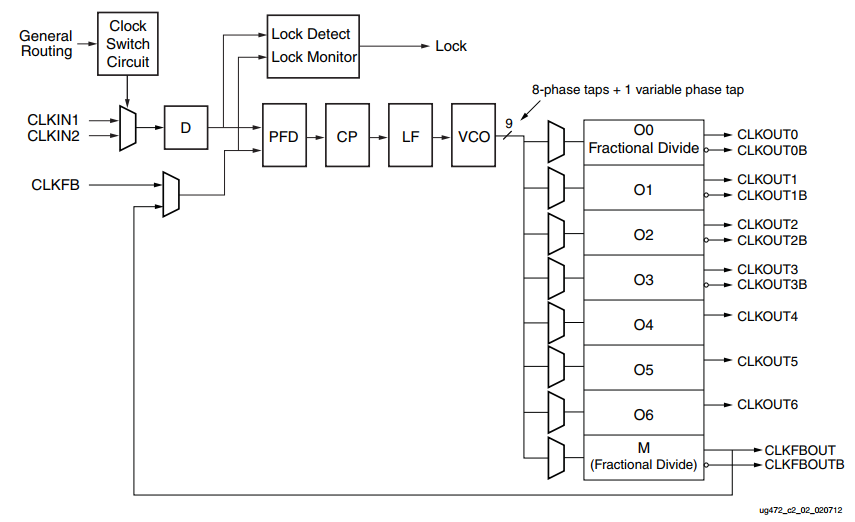

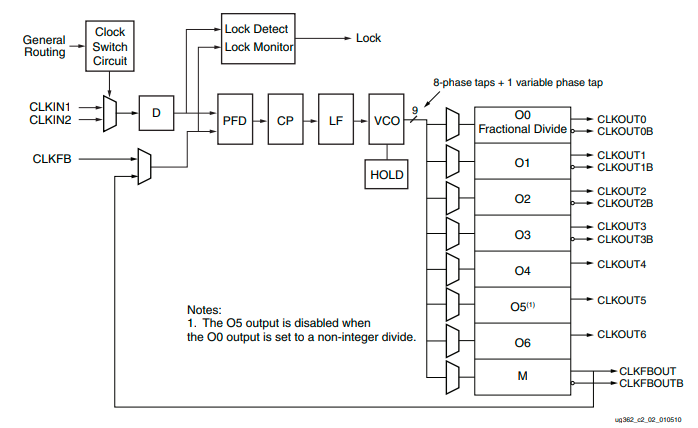

بلوکهای MMCM

در تراشههای Virtex-6 بلوکهای جدید دیگری به نام MMCM که مخفف عبارت Mixed Mode Clock Manager است، معرفی شدند. به بیان ساده یک بلوک MMCM نوعی از PLL است که قابلیتهای ویژه DCM را نیز پشتیبانی میکند. مثلاً MMCM همچون DCM قابلیت تغییر دینامیک فاز را دارد و در حقیقت به همین دلیل از عبارت Mixed Mode در نام گذاری این بلوک استفاده شده است. با معرفی بلوک MMCM هر دو بلوک DCM و PLL در تراشههای Virtex-6 کنار گذاشته شدند، چون این بلوک جدید قادر به اجرای عملکردهای مورد انتظارِ هر دو بلوک قبلی به صورت توأمان بود (شیفت یا تغییر فاز دینامیک و سنتز همزمان چندین کلاک با فرکانسهای متفاوت).

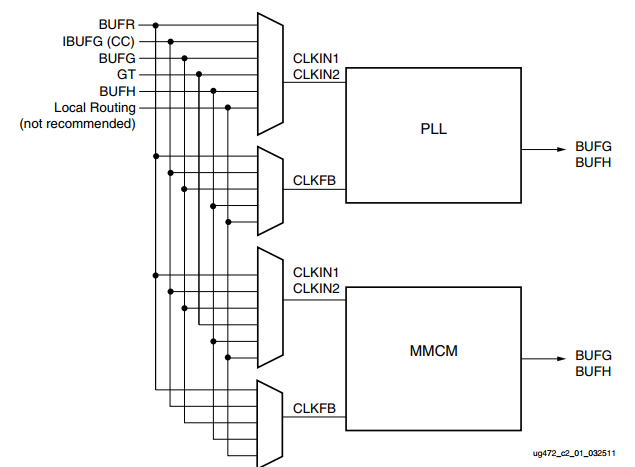

در تراشههای 7Series ، بار دیگر بلوکهای PLL به درون تراشههای FPGA بازگشتند و یک بلوک ترکیبی از MMCM و PLL برای مدیریت کلاک درون این نسل از تراشهها معرفی شد. احتمالاً مهمترین دلیلی که طراحان FPGA را مجبور به گرفتن این تصمیم کرده است، بزرگ شدن فضای منطقی قابل استفاده برای پیاده سازی در درون تراشهها بوده است. (به طور کلی PLL ها کوچکتر از MMCM ها هستند و فضای کمتری روی سطح سیلیکونی تراشه اشغال میکنند.) بعلاوه اینکه PLL ها به شکل ویژهای برای پشتیبانی از ساختارهای درون منابع ورودی/خروجی (IOB) بکارگرفته میشوند. پیاده سازی کنترلر برای حافظههای DDRx-SDRAM با استفاده از ویزارد معروف MIG (Memory Interface Generator) در ISE و Vivado بهترین مثال برای این موضوع است.

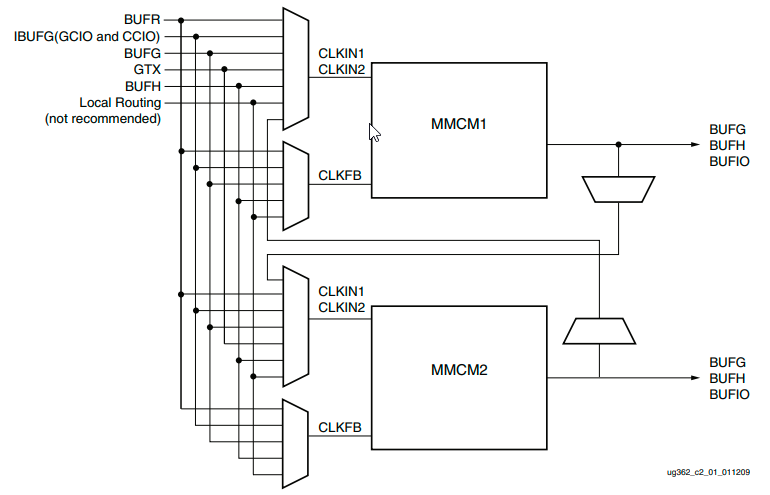

در تراشههای UltraScale و +UltraScale همچنان برای مدیریت کلاک از بلوکهای MMCM و PLL در کنار هم استفاده میشود. هرچند عملکرد و قابلیتهای مورد انتظار از بلوکهای PLL تا حدودی محدود شده است و گستردگی نسلهای پیشین را ندارند. در واقع به نظر میرسد Xilinx استفاده از PLL ها را به شکل اختصاصی برای بلوکهای ورودی خروجی (IO) سفارشی سازی کرده است و اتصالات انعطاف پذیرتری بین آنها در نظر گرفته است. این مسأله هنگام بکارگیری مد کاری “Native Mode” I/O که برای تبادل پرسرعت داده با DDRx-SDRAM ها مورد نیاز است، به خوبی نمایان میشود. البته PLL ها همچنان میتوانند در صورت نیاز در هر جایی فراخوانی و استفاده شوند، اما باید به این نکته توجه داشت که بلوک اصلی مدیریت کننده کلاک در این تراشهها MMCM است و هدف اصلی استفاده از PLL ها تولید کلاک برای IO ها است.

کاشیهای مدیریت کلاک

همانطور که اشاره شد توپولوژی تولید و توزیع کلاک در تراشههای Spartan-6 ، Virtex-6 ، 7Series و UltraScale بر اساس CMT ها شکل گرفته است. در عمل این CMT ها هستند که ساختار درخت و شبکه کلاک را شکل میدهند. هر CMT میتواند متشکل از یک یا چند MMCM و یک یا چند PLL در نزدیکی IO ها و همینطور یک بلوک Phasor باشد. دلیل استفاده از نام Tile برای این واحدهای سخت افزاری شیوه کنار هم قرار گرفتن آنها است. برای انتقال کلاک مدیریت شده درون CMT به سرتاسر تراشه، تعداد زیادی بافر از انواع مختلف در روی درخت کلاک هر تراشه گنجانده شده است. کلاک اولیه و اصلی همواره از طریق پینهای اختصاصی کلاک که اصطلاحاً Clock Capable (CC) Pin نامیده میشوند و به یکی از CMT ها منتهی میشوند، وارد تراشه FPGA میشود و سپس در بخشهای مختلف تراشه انتشار مییابد.

در گذشته و در نسلهای پیشین پایههای Clock Capable با عنوان GClock شناخته میشدند.

نواحی کلاک

مفهوم ناحیه کلاک یا Clock Region اولین بار هنگام معرفی تراشههای Virtex-4 وارد ادبیات Xilinx و تراشههای FPGA این شرکت شد. از نقطه نظر کلاک، تراشههای FPGA به تعدادی ناحیه کلاک تقسیم میشوند. هر چند تقسیم فضای داخلی تراشه به تعدادی ناحیه کلاک در ابتدا چندان حائز اهمیت به نظر نمیرسید، اما به مرور زمان با بزرگتر شدن تراشهها و افزایش تنوع کلاکهای مورد نیاز در یک طرح اهمیت آنها بر همگان روشن شد. هر ناحیه کلاک در بر گیرنده بخشی از عناصر سنکرون درون تراشه است. مدیریتِ تولید و توزیع کلاک در هر ناحیه میتواند مستقل از سایر نواحی صورت بپذیرد. در عمل نواحی کلاک با هدف محلی کردن یکسری از منابع و مسیرهای کلاک درون تراشهها ایجاد شدند.

از نقطه نظر کلاک، تراشههای FPGA بعد از Virtex-4 به تعدادی ناحیه کلاک تقسیم میشوند.

نواحی کلاک در Virtex-4

در ابتدای کار نواحی کلاک در تراشههای Virtex-4 با هدف بهبود الگوی توزیع کلاک درون تراشه و همینطور بازکردن دست طراح برای رهایی از قیدها و محدودیتهای نسلهای پیشین شکل گرفتند. مهمترین ویژگیهای هر ناحیه کلاک در این تراشهها عبارتند از:

- هر ناحیه کلاک از مرکز تراشه تا لبههای سمت راست یا چپ تراشه امتداد پیدا میکند.

- ارتفاع نواحی کلاک در این تراشهها برابر با ۱۶ بلوک قابل پیکره بندی یا CLB است.

- هر ناحیه کلاک در برگیرنده ۳۲ پین IO میباشد.

- با توجه به ابعاد تراشه، این تراشهها ممکن است بین ۸ تا ۲۴ ناحیه کلاک داشته باشند.

نواحی کلاک در Virtex-5

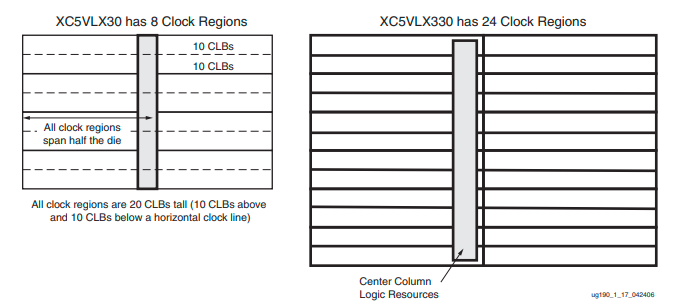

برای اینکه تصویر بصری بهتری از نحوه تقسیم بندی فضای داخلی تراشههای FPGA به نواحی کلاک داشته باشید. به شکل زیر دقت کنید. این شکل شمایی کلی از نواحی کلاک درون دو تراشه از خانواده Virtex-5 را نشان میدهد. نواحی کلاک در این تراشهها دارای مشخصات زیر هستند:

- هر ناحیه کلاک از مرکز تراشه تا لبههای سمت راست یا چپ تراشه امتداد پیدا میکند.

- ارتفاع این نواحی کلاک با هم برابر است و هر کدام شامل ۲۰ بلوک قابل پیکره بندی یا CLB و همینطور ۴۰ پین IO میباشند.

- با توجه به ابعاد تراشه، این تراشهها ممکن است بین ۸ تا ۲۴ ناحیه کلاک داشته باشند.

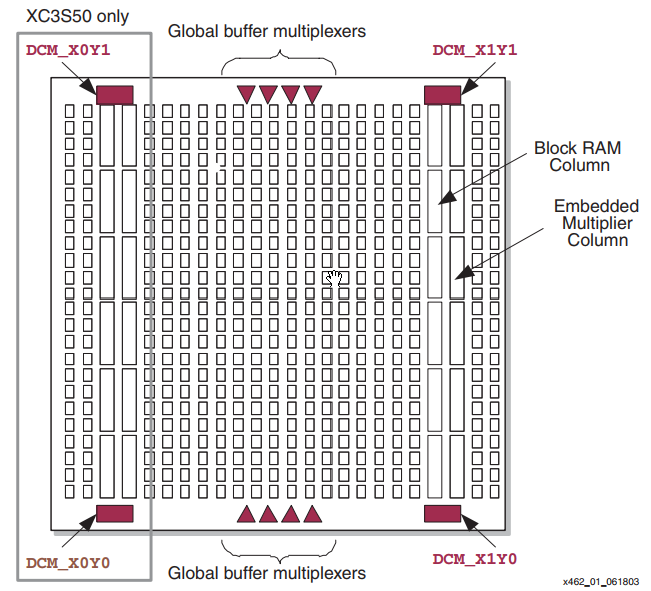

نواحی کلاک در Spartan-6

نحوه چیدمان نواحی کلاک در تراشههای Spartan-6 مشابه Virtex-4 و Virtex-5 است و مشخصات کلی آن به شرح زیر است.

- ارتفاع نواحی کلاک در این تراشهها برابر با ۱۶ بلوک قابل پیکره بندی یا CLB است.

- هر ناحیه کلاک در برگیرنده ۴۰ پین IO میباشد.

- هر ناحیه کلاک ۴ بلوک حافظه ۱۸ کیلو بیتی و ۴ اسلایس DSP48E1 را در بر میگیرد.

- این تراشهها بین ۲ تا ۶ ناحیه کلاک دارند.

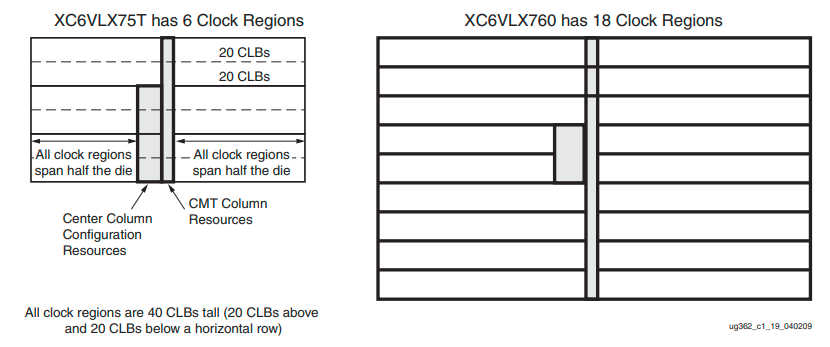

نواحی کلاک در Virtex-6

هر ناحیه کلاک در تراشههای Virtex-6 دارای ویژگیهای زیر میباشد:

- ارتفاع نواحی کلاک در این تراشهها برابر با ۴۰ بلوک قابل پیکره بندی یا CLB است

- هر بانک IO یک ناحیه کلاک محسوب میشود و در برگیرنده ۴۰ پین IO میباشد.

- هر بانک IO چهار پین اختصاصی کلاک دارد.

- این تراشهها بین ۶ تا ۱۸ ناحیه کلاک دارند.

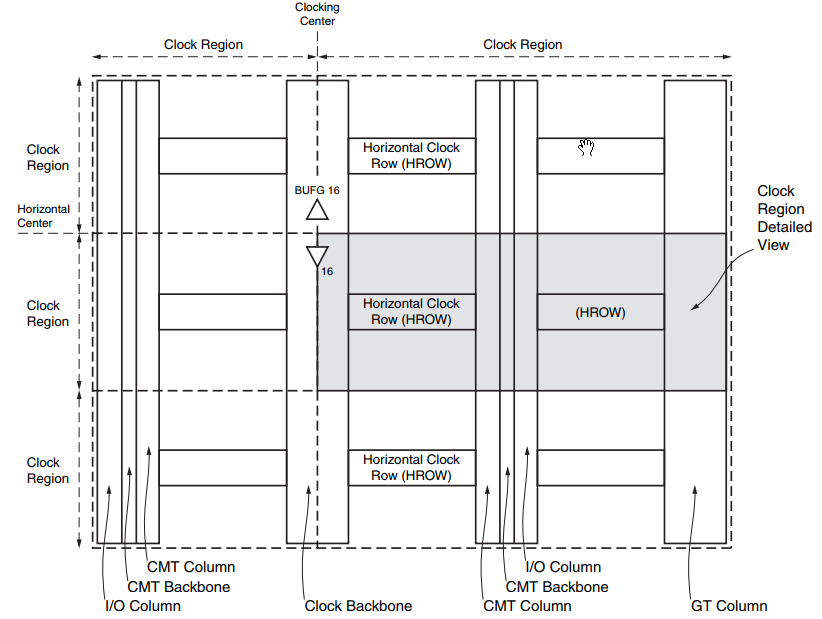

نواحی کلاک در 7Series

نواحی کلاک در تراشههای 7Series دارای ویژگیهای زیر هستند:

- تعداد این نواحی با توجه به سایز تراشه میتواند بین ۱ تا ۲۴ متغییر باشد.

- در داخل هر ناحیه کلاک مجموعهای از عناصر سخت افزاری سنکرون نظیر CLB ، DSP ، block RAM ، CMT و البته IOB وجود دارد. هر ناحیه کلاک فضایی به اندازه ۵۰ بلوک قابل پیکره بندی (CLB) اشغال میکند و در برگیرنده یک بانک ورودی خروجی (IO) است. هر بانک ورودی خروجی متشکل از ۵۰ پین ورودی یا خروجی است. دقیقاً در مرکز این ناحیه، خطوط اختصاصی کلاک قرار دارد که اصطلاحاً HROW کوتاه شده عبارت Horizontal Clock Row نامیده میشود.

- اگر خطوط کلاک در HROW را معیار قرار دهیم تعداد CLB های قرار گرفته در بالا و پایین HROW با هم یکسان و برابر با ۲۵ است.

- برخی از مسیرهای کلاک تنها در یک ناحیه با هم در ارتباط هستند.

به بیان بسیار ساده مسیرهای اختصاصی کلاک درون تراشههای 7Series و نسلهای بعد از آن را میتوان مشابه ستون فقرات و دندهها در بدن موجودات زنده در نظر گرفت. ستون فقرات کلاک جایی است که در آن بافرهای سرتاسری کلاک قرار میگیرند و نواحی کلاک جایی است که دقیقاً دندهها در وسط آن قرار میگیرند. خطوط افقی کلاک دقیقاً از وسط نواحی کلاک میگذرند.

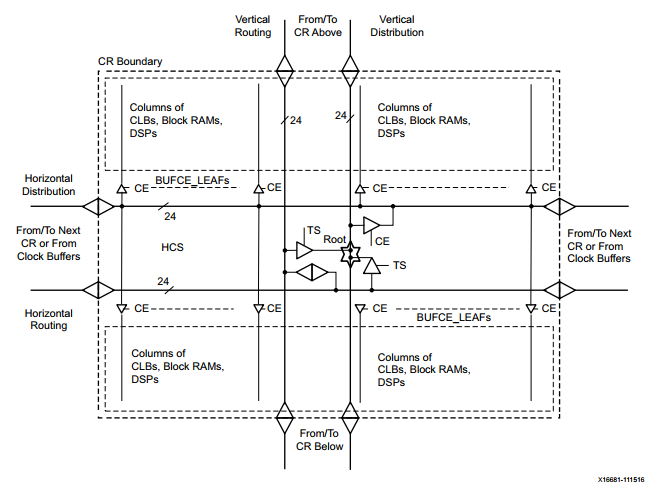

نواحی کلاک در UltraScale

ارتفاع نواحی کلاک در تراشههای UltraScale و +UltraScale برابر با ۶۰ بلوک قابل پیکره بندی یا CLB است و هر ناحیه کلاک در برگیرنده ۵۲ پین ورودی/خروجی معمولی و ۴ پین ورودی خروجی ترنسیور میباشد.

در تراشههای اولترا اسکیل بر خلاف نسلهای قبلی، نواحی کلاک به صورت متقارن در دو طرف ستون فقرات کلاک توزیع نشدهاند و نصف عرض تراشه را در بر نمیگیرند. در این تراشهها نواحی کلاک به شکل کاشی در کنار هم قرار گرفتهاند. هر یک از این کاشیها CR نامیده میشود. ارتفاع این کاشیها برابر با ۶۰ بلوک قابل پیکره بندی است و هر کاشی ۲۴ اسلایس DSP48E2 و ۱۲ حافظه بلوکی را در بر میگیرد. البته در این تراشهها مسیر افقی کلاک تحت عنوان Horizontal Clock Spin (HCS) همچنان حفظ شده است.

جمع بندی

در ابن نوشتار سعی ما بر آن بود تا شما را با بلوکهای مدیرت کلاک در نسلهای مختلف تراشههای FPGA آشنا کنیم و به شکل اجمالی آنها را مقایسه کنیم. در طراحی سناریوی تولید و توزیع کلاک آشنایی با منابع و امکاناتی که هر تراشه در اختیار شما قرار میدهد بسیار حائز اهمیت است. مقوله کلاک در FPGA، موضوع بسیار حساس و نسبتاً پیچیدهای است. اشتباه در نحوه چینش و استفاده از منابع کلاک میتواند اثرات منفی و غیرقابل اصطلاحی روی طرح شما بگذارد.

برآورده نشدن ملاحظات زمان بندی به دلیل اشتباه در طراحی سناریوی کلاک بعضاً ممکن است به باز طراحی بخشهای زیادی از طرح و دوباره کاریهای مکرر ختم شود. این موضوع با بزرگتر شدن طرح و افزایش فرکانس کاری مورد نیاز برای پیاده سازی به شدت نمایان میشود. در بخش دوم از این مقاله در رابطه با شبکه و بافرهای کلاک و نحوه توزیع کلاک در تراشه صحبت خواهیم کرد.

4 دیدگاه برای “مدیریت سیگنال کلاک : بخش اول مدیریت کلاک در FPGA”

عالی بود عالی، خدا قوت….

درود بر شما

علی عزیز از لطف و همراهی شما سپاسگزاریم.

سایت hexalinx حقیقا پر بارترین سایت داخلی در زمینه fpga.من هر هفته به سایت شما سر میزنم واقعا به تلاش و پشت کار شما احسنت میگم و شما رو الگوی بسیار مناسبی برای تمام کسانی که توی این زمینه فعالیت میکنن میدونم.ممنون بابت انتشار دانسته هاتون.

محمد عزیز از لطفی که به هگزالینکس دارید، سپاسگزاریم.

امیدورام در تمام مراحل کار و زندگیتون سربلند و موفق باشید.