مقدمه

در این مقاله دو قسمتی مفاهیم کلی مرتبط با منابع ورودی و خروجی FPGA مرور میشود. سپس به شکل مختصر مهمترین ویژگیهای این منابع معرفی میشوند. این مقاله به طور خاص برای تراشههای سری ۷ شرکت Xilinx نوشته شده است، اما بسیاری از تعاریف ارائه شده برای سایر خانوادهها قابل تعمیم است.

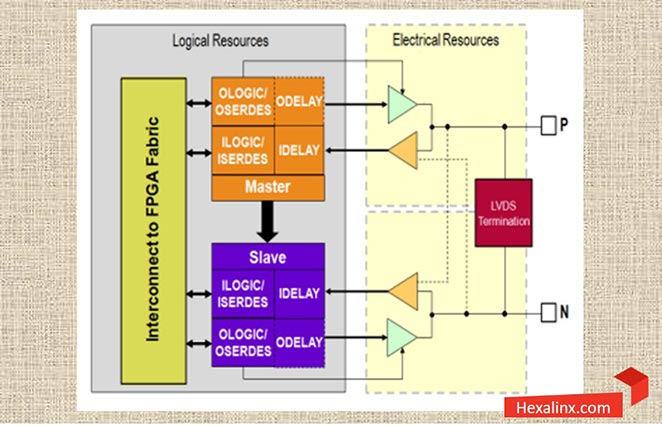

به طور کلی منابع ورودی/خروجی در هر FPGA، منابعی هستند که بین پینها و منابع منطقی درون تراشه قرار گرفته اند. این منابع به لحاظ ساختاری از دو بخش تشکیل شدهاند:

- بخش الکتریکی: وظیفه این بخش کنترل ولتاژ و استاندارد کاری ورودی/خروجی هاست. پیکرهبندی یک پین ورودی/خروجی به صورت تک سیم یا زوج سیم (تفاضلی) و همچنین فعال یا غیرفعال بودن امپدانس داخلی دیجیتال (DCI) هر ورودی/خروجی در این بخش تعیین میشود.

- بخش منطقی: وظیفه این بخش که خود متشکل از چند واحد است، اعمال کنترلهای منطقی روی سیگنالهای ورودی یا خروجی است. پیکرهبندی پورت از لحاظ SDR و یا DDR بودن و همینطور ورودی، خروجی و یا سه حالته بودن پورت در این بخش تعیین میشود. واحدهای پیشرفته تاخیر و سریالایزر/دی سریالایزر هم در این بخش قرار دارند.

بانکهای ورودی/خروجی

دسته بندی منابع ورودی و خروجی FPGA در قالب بانکهای ورودی/خروجی انجام میشود. تعداد این بانکها کاملا به نوع تراشه و پکیج آن وابسته است. در حالت کلی ویژگیهای الکتریکی هر ورودی یا خروجی با توجه به قیود قابل تعریف برای هر بانک، تعیین میشود. البته موارد استثنا نیز وجود دارد که باید به آنها توجه کرد.

با توجه به متفاوت بودن تعداد بانکها بسادگی میتوان حدس زد که تعداد پینهای ورودی/خروجی نیز با توجه به نوع پکیج و منابع درون تراشه متفاوت است. بلوکهای ورودی/خروجی با استفاده از ابزارهای گرافیگی Xilinx به سادگی قابل پیکرهبندی هستند و با بسیاری از استانداردهای الکتریکی سازگار هستند. توجه شود که تمامی پینهای فیزیکی روی تراشه به صورت IO قابل استفاده نیستد. با این وجود تعداد قابل توجهی از آنها به عنوان ورودی/خروجیهای همه منظوره در دسترس هستند. در هر پکیج بجز تعداد محدودی از پینها که به تامین تغدیه مورد نیاز تراشه و پیکرهبندی آن اختصاص دارند. سایر پایهها تقریباً مشابه هم هستند و قابلیتهای یکسانی دارند.

بانکهای ورودی/خروجی در تراشههای سری ۷ در دو کلاس HR و HP دسته بندی میشوند.

- بانکهای با رنج بالا یا High Rate ، همانطور که از نامشان پیدا است برای پشتیبانی از رنج ولتاژی وسیع بین 1.2v تا 3.3v طراحی شدهاند.

- در نقطه مقابل بانکهای با کارایی بالا یا High Performance ، که برای دستیابی به بالاترین راندمان در تبادل داده طراحی شدهاند. این بانکها رنج ولتاژی محدودتری دارند و از ولتاژها 1.2v تا 1.8v پشتیبانی میکنند.

تمامی تراشه های سری ۷ از بانکهای HR پشتیبانی میکنند اما بانکهای HP مختص تراشههای قدرتمندتر و بزرگتر هستند. هر بانک دارای تعدادی پین VCCO اختصاصی است که برای تعیین ولتاژ کاری آن بانک و تامین تغذیه مورد نیاز بافرهای ورودی در آن بانک مورد استفاده قرار میگیرد. هر بانک دارای دو پین با نام VREF است که برای تامین ولتاژ مرجع مد مشترک برای ورودیهای تکی (single-ended) بکار گرفته میشود. البته امکان تامین ولتاژ مد مشترک با مرجع داخلی نیز وجود دارد. هر بانک تنها میتواند یک ولتاژ مرجع داشته باشد.

بانک صفر در FPGA ها یک بانک خاص منظوره است و پین VREF ندارد.

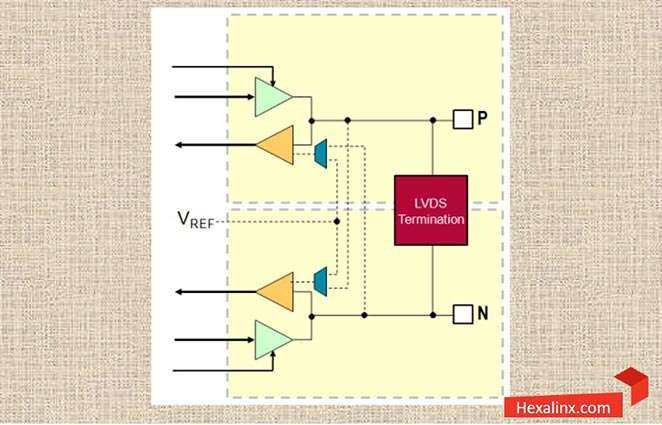

بخش الکتریکی منابع ورودی/خروجی

هر کدام از بانکها در تراشههای FPGA دارای ۵۰ پین ورودی/خروجی هستند. این پینها در اصطلاح SelectIO نام گذاری شدهاند. از این ۵۰ پین ۲ پین به صورت انحصاری تنها با استاندارهای سیگنالهای تک سیم سازگار هستند و ۴۸ پین باقی مانده به صورت ۲۴ زوج تفاضلی یا ۴۸ پین تکی قابل پیکرهبندی هستند. این ۴۸ پین به صوت دو به دو با برچسبهای P و N نام گذاری میشوند.

از نظر الکتریکی هر کدام از SelectIO ها میتوانند خواص متفاوتی داشته باشند. رفتار آنها به عنوان یک درایور خروجی و یا گیرنده ورودی با توجه به خواص الکتریکی که به آن بانک نسبت داده میشود، تعیین میشود. هر SelectIO دارای سه نوع درایور ورودی، خروجی و سه حالته است.

هر پین میتواند به صورت ورودی یا خروجی و یا به صورت ورودی/خروجی دو طرفه پیکرهبندی شود.

ورودیها و خروجیهای تکی از استاتدارد CMOS برای دریافت و یا تولید خروجی استفاده میکنند. برای سیگنالهای خروجی مقدار صفر منطقی به ازای مقادیر نزدیک به GND و مقدار یک منطقی به ازای مقادیر نزدیک به Vcco حاصل میشود. همینطور امکان قرار گرفتن در حالت امپدانس بالا نیز وجود دارد.

طراح به سادگی میتواند پارامترهایی نظیر slew rate و output strength را برای هر پورت خروجی به صورت مستقل تعیین کند. همینطور به صورت اختیاری امکان pull-up و pull-down کردن داخلی هر بلوک ورودی/خروجی وجود دارد. علاوه بر موارد فوق بانکهای HP مجهز به یک مدار داخلی کالیبراسیون برای ساخت تِرمینیشن زوجهای تفاضلی هستند.

مشابه پینهای تکی، زوجهای تفاضلی هم به صورت ورودی و یا خروجی قابل پیکرهبندی هستند. علاوه بر این زوجهای تفاضلی ورودی میتوانند به صورت اختیاری با یک مقاومت ۱۰۰ اهم داخلی به هم متصل شوند و اصطلاحاً تِرمینیشن داخلی یا Internal Termination داشته باشند.

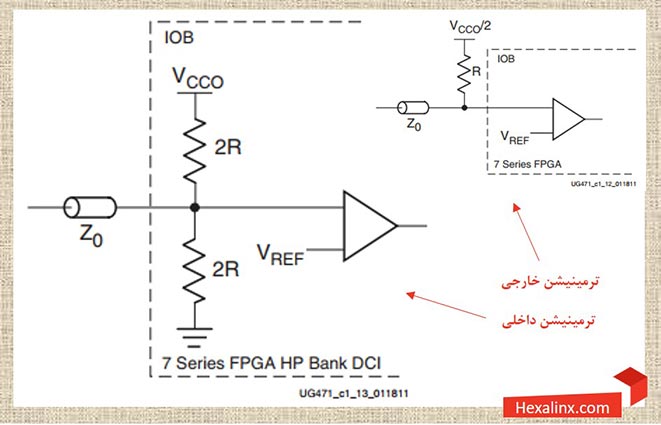

امپدانس قابل کنترل دیجیتال

قبل از اتمام بحث در این بخش بد نیست کمی در مورد DCI صحبت کنیم. البته باید یادآور شویم، نکاتی که در ادامه بیان میشود صرفا یک معرفی کوتاه است. خاتمه دادن یک خط انتقال با استفاده از یک مقاومت برای مدل کردن خصوصیات مصرف کننده در انتهای خط اصطلاحا تِرمینیشن (Termination) نامیده میشود. به بیان دقیقتر ترمینیشن روشی برای کاهش یا از بین بردن انعکاسهای ناخواسته در یک خط انتقال است. این انعکاسها باعث ایجاد اثرات ناخواسته و نویز در سیستم میشود. از نقطه نظر سختافزاری استفاده از تِرمینیشن مناسب یک ملاحظه مهم در طراحی محسوب میشود.

با بزرگتر شدن تراشههای FPGA و بالاتر رفتن سرعت کلاک سیستم، ساخت بوردهای مدار چاپی روز به روز سخت تر میشود. طراحان سخت افزار میدانند که کنترل یکپارچگی سیگنال در زمان انتشار یا همان Signal Integrity بخش مهمی است و حتما باید مورد توجه قرار بگیرد. مفهوم امپدانس قابل کنترل دیجیتال یا DCI دقیقا برای پاسخ گویی به چنین نیازی طراحی شده است.

تقریبا تمامی استانداردهای تفاضلی توسط ورودی/خروجیها پشتیبانی میشود، از LVDS تا HSTL همگی قابل تنظیم هستند.

بانکهای HR از DCI پشتیبانی نمیکنند.

پس به طور خلاصه نکات مرتبط با بخش الکتریکی ورودی/خروجیها به صورت زیر میباشد.

پیکره بندی پایه های P و N مجاور در یک بانک به دو صورت امکان پذیر است.

- دو سیگنال تک سیم

- یا یک زوج تفاضلی

سطوح ولتاژی ورودیها در حالت استاندارد CMOS به صورت زیر است.

- مقدار صفر منطقی به ازای مقادیر نزدیک به GND

- مقدار یک منطقی به ازای مقادیر نزدیک به Vcc

در صورت استفاده از پایههای VREF مقادیر ورودیها با توجه ولتاژ مرجع تعیین میشود.

- مقدار صفر منطقی به ازای مقادیر کمتر از VREF

- مقدار یک منطقی به ازای مقادیر بیشتر از VREF

در حالت تفاضلی یک یا صفر بودن ورودیها به صورت زیر تعیین میشود.

- مقدار صفر منطقی به ازای Vp < Vn

- مقدار یک منطقی به ازای Vp > Vn

جمع بندی

هر بانک ورودی/خروجی میتوانند بصورت مستقل برای یک سطح ولتاژ متفاوت نسبت به بانک دیگر پیکرهبندی شود. این ولتاژ با توجه به ولتاژ پین VCCO تعیین میشود، هر پین میتواند جریان خروجی و سرعت متفاوتی داشته باشد. پینها میتوانند به صورت دو طرفه پیکرهبندی شوند این مزیت باعث بالار رفتن کارایی FPGA در کاربردهایی که نیاز به پیاده سازی پروتکل کنترلی دوطرفه دارند، میشود.

مطلبی که مطالعه کردید قسمت اول از مقاله آموزشی معرفی منابع ورودی خروجی FPGA بود، در قسمت دوم از این سری آموزشی در رابطه با بخش منطقی منابع ورودی خروجی صحبت خواهیم کرد.

10 دیدگاه برای “از منابع ورودی و خروجی FPGA چه می دانیم؟ (قسمت اول: منابع الکتریکی)”

سلام و ادب

درسته هر تراشه ای دیتاشیت خاص خودشو داره ولی اینکه اول فارسی آشنا بشیم خیلی بهتر و قابل فهم تره

لطفا بیشتر از این موارد بذارید

تشکر

محمد حسین عزیز ار اینکه نظر ارزشمند خودتون و با ما در میان گذاشتید، سپاسگزاریم.

و همچنین توضیحاتی درباره single_ended و differentiol هم بفرمایین سپاسگزار خواهم بود.

با سلام و درود فراوان خدمت شما

از همراهی شما سپاسگزاریم و از اینکه با کمی تاخیر پاسخگوی شما هستیم، عذرخواهی میکنم.

همانطور که میدانید تعدادی زیادی استاندارد الکتریکی وجود دارد که برخی تک سیم و برخی دیگر زوج سیم (تفاضلی) هستند.

مثلا TTL و CMOS استانداردهای تک سیم (single ended) هستند و استانداردهایی همچون LVDS و LVPECL استانداردهای زوج سیم یا تفاضلی (differential) هستند.

با سلام میشه لطف بفرمایین توضیحات بیشتری در رابطه با DCI بدین؟

با سلام و درود فراوان خدمت شما

از همراهی شما سپاسگزاریم و از اینکه با کمی تاخیر پاسخگوی شما هستیم، عذرخواهی میکنم.

درک ماهیت و اهمیت امپدانس قابل کنترل دیجیتال وابسته به درک مفهوم ترمینشن در خطوط انتقال است. همانطور که در متن هم اشاره شده خاتمه دادن یک خط انتقال با استفاده از یک مقاومت برای مدل کردن خصوصیات مصرف کننده در انتهای خط، اصطلاحا تِرمینیشن (Termination) نامیده میشود از ترمینیشن برای کاهش نویز خطوط استفاده میشود.

به بیان بسیار ساده ترمینیشن یک مقاومت سری یا موازی در سمت مصرف کننده در یک ارتباط الکتریکی است. فرض کنید قرار است با یک سیم یک پایه از FPGA را به یک مدار الکتریکی دیگر متصل کنیم و FPGA نقطه انتهای مسیر است. یعنی سیگنال به سمت FPGA حرکت میکند. در این شرایط FPGA مصرف کننده است و باید یک ترمینیشن برای آن در نظر گرفته شود. این ترمینیشن میتواند یک مقاومت در کنار تراشه باشد یا اینکه با استفاده از DCI تامین شود.

به عبارت دیگر DCI جایگزینی برای مقاومتهای ترمینیشن خارجی است که معمولا در اتصال اینترفیسهای تفاضلی به FPGA مورد نیاز است و مسئولیت بکارگیری این ویژگی برعهده مهندس طراح نرم افزار است.

در صورتی که هنوز هم نیاز به جزئیات بیشتر دارید، پسشنهاد میکنم حتماً به مراجع ذکر شده مراجعه کنید

با سلام

بسیارممنون از شما.خیییییلی عالی بودند.جامع ،شفاف و قابل درک

از اینکه همراه ما هستید خوشحالیم. برای شما آرزوی موفقیت داریم.

سلام

ممنون از مطالب مفيدتون، كامل و شفاف توضيح داده شده، خيلي عاليه!

پیروز و پاینده باشید.