مقدمه

این نوشتار از پایگاه دانش هگزالینکس یک بروز رسانی برای مقاله مفهوم حافظه در FPGA است و به معرفی بلوکهای UltraRAM در تراشههای +UltraScale اختصاص دارد.

حافظههای اولترا یا UltraRAM ها بلوکهای جدید حافظه در تراشههای FPGA هستند که در خانواده +UltraScale شرکت Xilinx معرفی شدهاند. این بلوکهای حافظه در کنار ساختارهای قدیمی ترِ حافظه که در نسلهای قبلی معرفی شده بودند، امکان ذخیره سازی حداکثر 500Mb داده را درون بزرگترین تراشه این خانواده امکان پذیر کردهاند. یعنی حدود ۶ برابر حافظه بیشتر در مقایسه با حداکثر حافظههای در دسترس روی تراشههای ۲۸ نانومتری 7Series که یک دهه قبل از آن عرضه شده بودند.

ساختارهای حافظه در FPGA های Xilinx

وقتی صحبت از دستیابی به حداکثر راندمان و کارایی یک سیستم، بعد از پیاده سازی روی تراشههای قابل پیکره بندی به میان میآید، مطمئناً بخشی از ذهن طراح به نحوه خواندن و نوشتن دادهها روی حافظه درگیر میشود. هر چه دادهها نزدیک تر ذخیره شده باشند و سریع تر خوانده شوند، کارایی ببیشتری از کلیت سیستم به دست میآید.

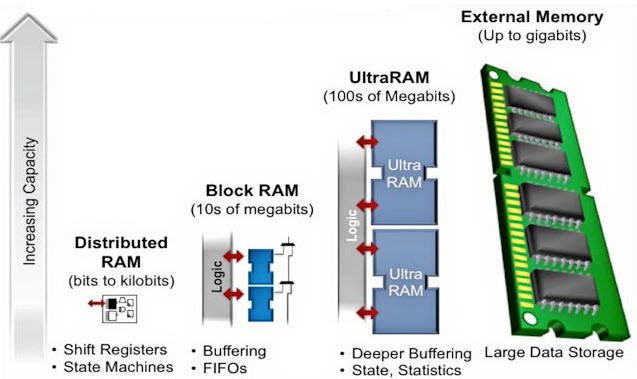

این یکی از مهمترین دلایلی است که تراشههای FPGA و SoC شرکت Xilinx گزینههای مختلف و متنوعی از ساختارهای حافظه را در اختیار طراحان قرار میدهند. گزینههایی همچون:

- حافظههای توزیع شده (DistributedRAM)

- حافظههای بلوکی (BlockRAM) و

- نسل جدید حافظههای اولترا (UltraRAM)

برای انتخاب بین حافظههای بلوکی و حافظههای توزیع شده چند نکته ظریف وجود دارد که بهتر است در نظر گرفته شود. همانطور که اشاره شد، پیش تر در پایگاه دانش هگزالینکس مقاله کاملی در رابطه با حافظهها در FPGA منتشر شده است که مطالعه آن میتواند به انتخاب مناسب بین حافظهها کمک کند. اما شاید معمول ترین قاعده برای انتخاب بین آنها وابسته به تعداد بیتهایی است که قصد داریم، ذخیره کنیم.

- در صورت نیاز به ذخیره ۶۴ یا تعداد کمتری بیت، بهتر است حافظههای توزیع شده مورد استفاده قرار بگیرد.

- در صورت نیاز به ذخیره ۶۴ تا ۱۲۸ بیت داده با طول بیت کمتر از ۱۶ بیت بهتر است از حافظههای توزیع شده استفاده کنیم.

- برای ذخیره بیش از ۱۲۸ داده استفاده از بلوکهای حافظه اولویت دارند.

در عمل استنتاج مستقیم ساختار حافظه درون کدهای HDL بهترین راه برای حصول اطمینان از استفاده بهینه از ساختارهای مختلف حافظه است. این کار ابزار سنتز و پیاده سازی را قادر میسازد که بهترین ساختار حافظه را هنگام ساخت نت لیست و پیاده سازی طرح انتخاب کند. اما کاربردهای جدید امروزی، اغلب نیاز به ذخیره حجم قابل توجهی از دیتا دارند که تنها روی حافظههای بلوکی قابل پیاده سازی هستند.

در تراشههای FPGA و SoC خانواده +UltraScale همچون نسلهای قبلی بلوکهای حافظه (BRAM) تنها قادر به ذخیره سازی 36kb داده هستند این بلوکها انعطاف پذیری قابل قبولی برای ذخیره سازی داده با طول بیتهای بزرگ و کوچک دارند. هر بلوک از دو پورت مستقل از هم برای نوشتن و خواندن پشتیبانی میکند. علاوه بر این هر بلوک 36kb به صورت دو بلوک 18kb نیز قابل پیاده سازی میباشد.

با کمک BRAM ها، طراح این امکان را دارد که با اتصال آبشاری آنها به یکدیگر حافظههای یکپارچه بزرگتری برای ذخیره سازی بیتهای داده درون طرح ایجاد کند. این حافظهها ممکن است به عنوان بخشی از فضای موقت مورد نیاز برای ذخیره دادههای الگوریتم و یا مقادیر و پارامترهای مورد نیاز برای پیکره بندی سیستم مورد استفاده قرار بگیرند.

در تراشههای 7Series و UltraScale اگر سایز دادههای مد نظر برای ذخیره سازی به اندازهای بزرگ باشد که ذخیره آنها درون BRAM ها امکان پذیر نباشد، در این صورت معمولاً حافظههای جانبی خارج از تراشه (off chip memory) همچون DDR ها یا QDR ها مورد استفاده قرار میگیرند.

اما در تراشههای +UltraScale شرایط کمی متفاوت است، چون این تراشهها علاوه بر BRAM و DistributedRAM از عناصر حافظه جدیدی به نام حافظههای اولترا یا همان UltraRAM (URAM) نیز بهره میبرند. بلوکهای UltraRAM در بسیاری از موارد میتوانند جایگزین حافظههای خارجی بشوند و در عین حال کارایی و عملکرد بسیار بهتری را نسبت به حافظههای خارجی تراشه به همراه میآورند.

لازم به ذکر است که بلوکهای UltraRAM جایگزینی برای حافظههای چند گیگابایتی SDRAM و یا حافظههای EPROM که در کنار تراشههای FPGA مورد استفاده قرار میگیرند، نیستند. هدف اصلی از معرفی این SRAM های بزرگ به تعویق انداختن نیاز طراح به استفاده از حافظههای جانبی بزرگ است. به عنوان نمونه برخی از مهمترین انگیزههایی که ممکن است برای بکارگیری این حافظه وجود داشته باشد عبارتند از:

- حافظههای SRAM داخلی تراشه FPGA سریعتر از حافظههای خارجی SDRAM در کنار تراشه FPGA هستند.

- برآورده کردن ملاحظات زمان بندی برای حافظههای SRAM داخلی بسیار ساده تر از حافظههای خارجی است.

- برخلاف SDRAMها، حافظههای SRAM داخلی نیازی به استفاده از پروتکلها و اینترفیسهای پیچیده برای کنترل و تبادل داده ندارد.

بلوکهای UltraRAM

فضای حافظهِ اضافی که توسط UltraRAM ها برای طراح قابل استفاده میباشد با توجه به تراشه هدف متفاوت است، از 13.5Mb در تراشه Zynq MPSoC ZU4EG شروع میشود و تا 360Mb در تراشه Virtex UltraScale+ VU13P افزایش مییابد. اگر چه در تراشههای Virtex UltraScale+ VU13P حداکثر حافظه مستقل قابل پیکره بندی به 100Mb محدود شده است و ایجاد فضای یکپارچه ذخیره سازی بیشتر 100Mb امکان پذیر نیست، که البته عدد بزرگ و قابل توجهی است. در نتیجه این افزایش کل حافظه در دسترس در تراشه VU13P به حدود 500Mb افزایش مییابد.

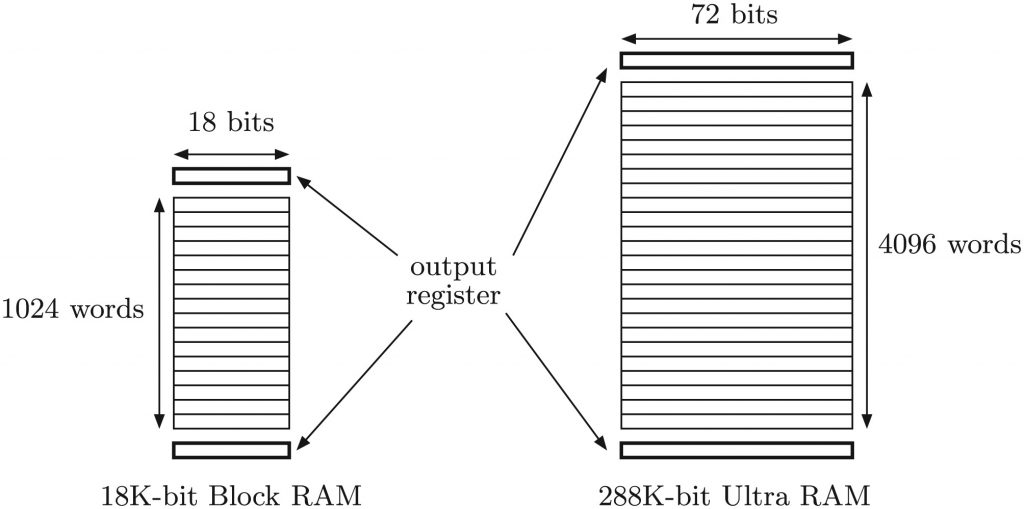

بلوکهای UltraRAM حافظههایی با سایز 228Kb هستند که تنها با یک کلاک سنکرون کار میکنند و حدوداً ۸ برابر بزرگتر از BlockRAM ها هستند. برخلاف BRAM ها، هر URAM دارای دو پورت و اندازه (عمق) ثابت 4k و طول ۷۲ بیت است، که هر دو پورت با یک کلاک سنکرونِ مشترک کار میکنند، اما در عین حال پورتها کاملاً مستقل از هم هستند.

از آنجایی که هر دو پورت مستقل از هم هستند، امکان وقوع تصادم هنگام نوشتن در این حافظهها وجود دارد، از این رو رفتار UltraRAM ها با توجه به اینکه کدام یک از پورتها برای نوشتن و کدام یک برای خواندن استفاده میشود، متفاوت است. یکی از کلیدی ترین مفاهیمی که باید حتماً به خاطر سپرده بشود این است که پورت A همواره کارش را زودتر به پایان میرساند، یعنی:

- اگر هر دو پورت A و B در یک لحظه در یک آدرس واحد بنویسند، آنگاه داده نوشته شده توسط پورت A توسط پورت B بازنویسی میشود.

- اگر پورت A شروع به خواندن از آدرسی بکند که همزمان پورت B در حال نوشتن در آن است، آنگاه داده خوانده شده روی پورت A داده قدیمی روی حافظه است و نه دادهای در حال نوشته شدن در آن است.

- اگر پورت A در حال نوشتن در آدرسی باشد که پورت B همزمان قصد خواندن آن را دارد، آنگاه پورت B دادهای را که روی پورت A قرار دارد، میخواند.

در تراشههای +UltraScale، مشابه تراشههای 7Series تمامی منابع روی تراشه به صورت ستونی سازماندهی شدهاند. تعداد ستونهای URAM در تراشههای مختلف با یکدیگر متفاوت است و از یک ستون تا حداکثر ۵ ستون متغیر میباشد. به این ترتیب عمق دادن به ساختارهای حافظه مبتنی بر URAM ها میتواند همانند BRAM ها با صرف کمترین هزینه از منابع منطقی و با کمک اتصالات مستقیمی که بین منابع حافظه وجود دارد، صورت بپذیرید. یعنی اگر امکان ایجاد یک حافظه با استفاده از حافظههای یک ستون وجود داشته باشد، در این صورت هیچ منابع اضافی از تراشه مصرف نخواهد شد.

اگر سایز حافظه انتخابی به اندازهای بزرگ باشد که برای ایجاد آن به بیش از یک ستون URAM نیاز باشد، در این صورت منابع و اتصالات دیگر درون تراشه نیز استفاده میشوند.

استفاده از UltraRAM ها

از آنجایی که تراشههای +UltraScale در محیط توسعه ISE پشتیبانی نمیشوند از این رو برای استفاده از UltraRAM ها الزاماً باید محیط توسعه Vivado مورد استفاده قرار بگیرد. روشهای متعددی برای فراخوانی آنها در محیط توسعه Vivado وجود دارد که مهمترین آنها عبارتند از:

- روش اول استنتاج مستقیم حافظه از روی کدهای HDL است. یعنی طبق روال مرسوم کدهای HDL مد نظر به شکلی نوشته شوند که ابزار سنتز به صورت اتوماتیک فانکشن مطلوب را پیاده سازی کند و یک نگاشت مناسب به منابع لاجیک (منطقی) درون تراشه شکل بگیرد.

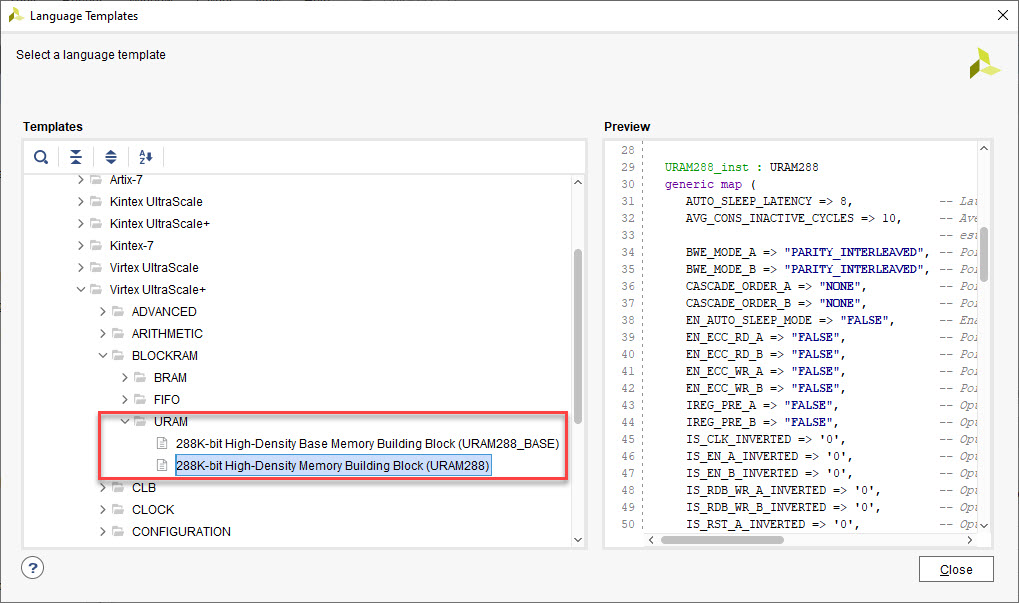

- روش دوم نمونه سازی سریع با استفاده از نمونه کدهای آماده یا Primitive ها و یا عناصر XPM اختصاصی است، که در نسخههای 2016 به بعد در محیط توسعه Vivado گنجانده شده است. با این کار یک نمونه از حافظه به صورت مستقیم درون کدهای RTL قرار داده میشود. این روش باعث ميشود طراح، کنترلی دقیقی روی نحوه پیاده سازی و عملکرد طرح RTL فراخوانی شده، داشته باشد.

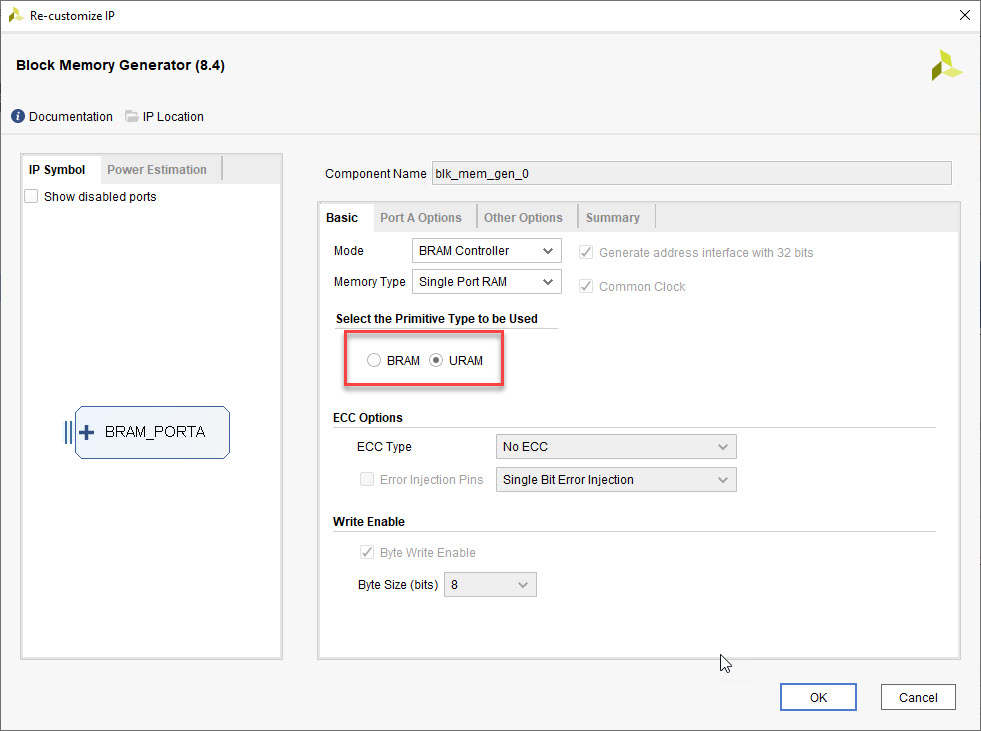

- و روش سوم استفاده از Block Memory Generator در Vivado IP Integrator و انتخاب گزینه URAM در پنجره تنظیمات آن است که عملاً ساده ترین روش برای فراخوانی این حافظهها است.

// Language Template VHDL/Verilog → Synthesis Constructs → Coding Examples → RAM VHDL/Verilog → Device Primitive Instantiation → Kintex/Virtex UltraScale+ → BLOCKRAM → URAM VHDL/Verilog → Xilinx Paramaterized Macros (XPM) → Memory (XPM_MEMORY) → RAM

برای آشنایی با XPM ها و قابلیتهای آن ها به مقاله فراخوانی حافظهها و عناصر سنکرون ساز کلاک با استفاده از XPM مراجعه بفرمایید.

در انتها باید به این نکته اشاره کرد که تمام تراشههای +UltraScale از نعمت UltraRAM بهره نمیبرند، اما در صورتی که تراشه هدف، از عناصر UltraRAM پشتیبانی کند، بدون شک باید نهایت تلاش را برای استفاده حداکثری از آنها به کار گرفت.

جمع بندی

معمولاً تمامی طرحهایی که در FPGA پیاده سازی میشوند، به نوعی از حافظه در شکلها و سایزها مختلف نیاز دارند. اضافه شده بلوکهای جدید، بزرگ و انعطاف پذیر UltraRAM به تراشههای خانواده +UltraScale ظرفیت ذخیره سازی قابل ملاحظهای در درون تراشه FPGA در اختیار طراح قرار میدهد که میتواند بسیار کاربردی باشد. قابلیت متصل کردن بلوکهای قرار گرفته در یک ستون و ساخت حافظههایی با اندازههای متنوع و نسبتاً بزرگ این امکان را به هر کاربری میدهد که بهترین راه حل را برای طراحیهای پیچیده امروزی بکار بگیرد. در عمل بخش زیادی از پیچیدگیهای طراحی بورد و توان مصرفی حافظههای SDRAM با معرفی این بلوکهای حافظههای جدید کنار گذاشته شده است.

منبع : hakster.io, wp477