مقدمه

این مقاله از پایگاه دانش هگزالینکس با هدف معرفی یکی از کتابخانههای کاربردی Xilinx با نام XPM و نحوه استفاده از آن برای فراخوانی حافظهها و عناصر سنکرون ساز کلاک برای علاقمندان به دانشهای تخصصی در حوزه FPGA گردآوری و تدوین شده است. حافظهها و عناصر سنکرون ساز کلاک از جمله ساختارهایی هستند که معمولاً در تمامی طراحیهای FPGA مورد استفاده قرار میگیرند. عناصر حافظه کاربردهای مختلفی دارند و برای ذخیره دادههای ورودی، ذخیره نتایج حاصل از گامهای مختلف پردازشی در یک سیستم، بافر کردن اطلاعات بین طبقات پردازشی سیستم و البته به اشتراک گذاری دادهها بین دو یا چند محدوده کلاک با استفاده از بافرهای آسنکرون (asynchronous FIFOs) بکارگرفته میشوند. عناصر سنکرون ساز هم برای مراقبت از دیتا هنگامی که از یک محدوده کلاک به محدوده دیگر کلاک منتقل میشود، مورد استفاده قرار میگیرند.

مفهوم XPM

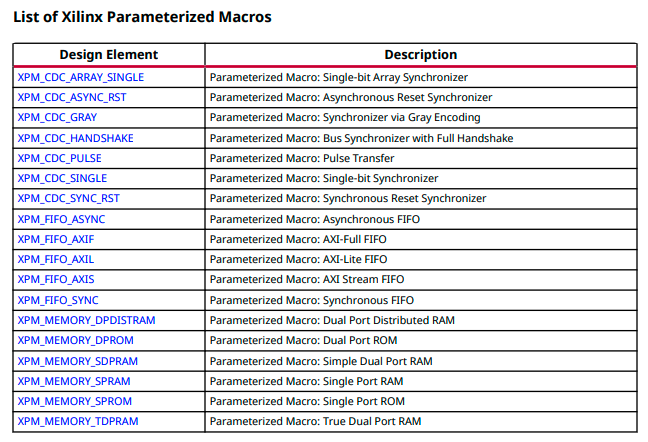

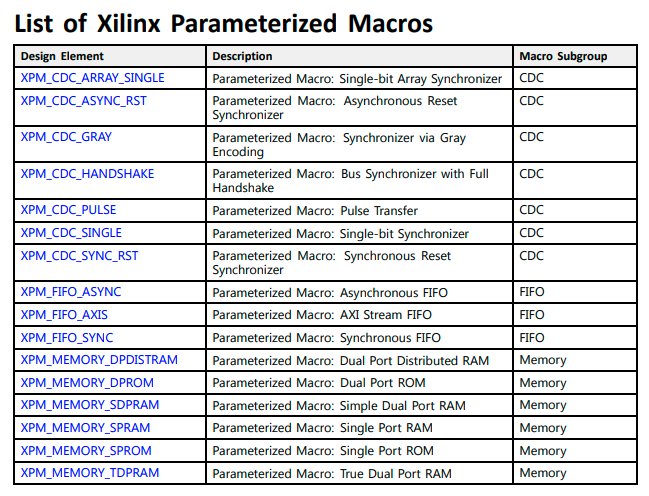

در ابتدا لازم است کمی در مورد XPM صحبت کنیم. اینکه XPM چیست، چه کاربردی دارد و چگونه باید از آنها استفاده کرد؟ عبارت Xilinx Parametrized Macros (XPM) با ترجمه تحت لفظی ماکروهای پارامتری شده Xilinx به آن دسته از عناصر ساده کتابخانهای در محیط توسعه Vivado اطلاق میشود که به صورت معمول در تمامی طراحیهای HDL مورد نیاز هستند. به طور کلی XPM ها ماژولهای نوشته شده با زبان SystemVerilog هستند که در محیط توسعه Vivado تجمیع شدهاند. حافظههای RAM و ROM و FIFO ها و همینطور عناصر CDC (عناصر مورد استفاده برای سنکرون سازی کلاک بین دو محدوده کلاک) ماژولهایی هستند که Xilinx برای آنها XPM ارائه کرده است و جزئیات آن به شرح زیر است.

- عناصر XPM_MEMORY مبتنی بر ساختارهای حافظه RAM و ROM

- عناصر XPM_CDC مبتنی بر پیاده سازی مدارات پایدار برای تبادل امن دیتا بین دو محدوده کلاک

- عناصر XPM_FIFO مبتنی بر ساختارهای FIFO برای تبادل سنکرون و آسنکرون اطلاعات

پیشتر در پایگاه دانش هگزالینکس مقالهای کامل در رابطه با تکنیکهای سنکرون سازی در FPGA منتشر شده است که میتوانید برای درک بهتر پدیده CDC و لزوم استفاده از عناصر XPM_CDC برای انتقال پایدار و کم ریسک دیتا از یک محدوده کلاک به محدوده کلاک دیگر آن را مطالعه کنید.

توضیحات مقدماتی در رابطه با XPM کافیست. اجازه بدهید در ادامه بحث را کمی گسترش دهیم و در رابطه با نحوه فراخوانی عناصر حافظه از کتابخانه XPM جزئیات بیشتری ارائه کنیم.

Macro ها و Primitive ها

اصطلاح Primitive به واحدهای سخت افزاری درون تراشههای FPGA که توسط طراح قابلیت فراخوانی دارند، اطلاق میشود. جزئیات این واحدهای سخت افزاری کاملاً وابسته به معماری تراشه هدف است.

اصطلاح Macro به عناصری گفته میشود که در کتابخانههای UniMacro و XPM در محیط توسعه Vivado و ISE در دسترس هستند و برای مدل کردن یک رفتار یا عملکرد خاص و غالباً پیچیده Primitive ها مورد استفاده قرار میگیرند. ابزار سنتز با استفاده از Macro ها به صورت اتوماتیک Primitive یا Primitive های بکار رفته در آن را فراخوانی و پیکره بندی میکند و به طرح اصلی اضافه میکند.

کتابخانه UniMacro مخصوص تراشههای سری ۷ و نسلهای قبل از آن است و در سریهای UltraScale پشتیبانی نمیشود.

فراخوانی XPM

برای استفاده از عناصر XPM در محیط توسعه Vivado میتوان از یکی از دو رویکرد زیر استفاده کرد.

- استنتاج (Inference) : با استفاده از استنتاج ما طبق روال مرسوم کدهای HDL مد نظر را به شکلی مینویسیم که امیدوار باشیم ابزار سنتز به صورت اتوماتیک فانکشن مطلوب ما را پیاده سازی کند و یک نگاشت مناسب به منابع لاجیک (منطقی) درون تراشه شکل بگیرد. از این رو استفاده از روش استنتاج باعث دستیابی به یک معماری کاملاً انعطاف پذیر برای پیاده سازی ساختارهای حافظه و سنکرون ساز است.

- نمونه سازی (Instantiation) : با فراخوانی مستقیم یا نمونه سازی، یک نمونه از کامپوننت یا ماژول به صورت مستقیم درون کدهای RTL قرار داده میشود. این روش باعث ميشود طراح کنترلی دقیقی روی نحوه پیاده سازی و عملکرد طرح RTL فراخوانی شده، داشته باشد. این رویکرد اغلب در مواردی که یک عنصر سنکرون ساز خاص و یا ساختارهای پیجیده تر حافظه نظیر حافظههای دو پورت یا FIFO ها مورد نیاز باشند، بکارگرفته میشود.

وقتی که یک طرح جدید در محیط توسعه Vivado ایجاد میکنیم، از مزیتی ویژه برخودار میشویم و میتوانیم برای بسیار از عملکردهای مدنظرمان از IP Core ها استفاده کنیم. البته این ویژگی در محیط توسعه ISE نیز وجود داشت اما در Vivado نگاه ویژهای به آن شده است و کتابخانه کاملی از IP ها برای فراخوانی در دسترس طراح است. بیاید فرض کنیم قصد داریم چند پیکره بندی متفاوت از حافظههای داخلی تراشه FPGA را در طرح خود بکار بگیریم. در این کتابخانه طیف گستردهای از ساختارهای حافظه شامل حافظههای تک پورت و دو پورت و همینطور بافرهای FIFO سنکرون و آسنکرون فراهم آورده شده است که همگی با استفاده از Block Memory Generator قابل پیاده سازی هستند و به سادگی میتوان از آنها بهره مند شد.

در کنار سادگی، استفاده از حافظهّهایی که به کمک Block Memory Generator تولید شدهاند، محدودیتها و معایبی را نیز به همراه دارند. اول از همه اینکه این IP ها به صورت black box در زمان سنتز به سایر بخشهای طراح اضافه میشوند. این مسأله باعث میشود ابزار سنتز قادر به ارائه تخمین درستی از منابع مصرفی و تایمینگ طرح نباشد. به بیان دیگر با وجود اینکه فراخوانی ساختارهای مختلف حافظه به صورت black box تأثیری روی عملکرد بهینه آنها ندارد اما کمی گزارشهای خروجی و فیدبکهایی را که به طراح داده میشود، تحت تأثیر قرار میدهد.

از سوی دیگر استفاده از Xilinx Parameterized Macros (XPM) روشی است که میتواند جایگزین استفاده از Block Memory Generator شود. طراحان با استفاده از XPM ها باز هم قادر به ایجاد و فراخوانی ساختارهای مختلف حافظه درون طرح خواهند بود، بعلاوه اینکه از مزایای ویژهای نظیر کاهش قابل توجه زمان سنتز و شبیه سازی نیز بهره مند میشوند. نکته جالب اینجاست که با استفاده از XPM ها دیگر خبری از black box در گزارش خروجی نخواهد بود و ابزار سنتز قادر به تولید گزارش تایمینگ و منابع مصرفی نسبتاً دقیق تری خواهد بود.

بکارگیری XPM ها قابلیتی است که فقط برای تراشههای سری ۷ به بعد امکان پذیر است از این رو پیش از شروع طراحیهای جدید حتماً به استفاده از آنها فکر کنید. در ادامه نحوه فراخوانی XPM ها را مرور خواهیم کرد.

برای استفاده از XPM ها مشابه کاری که بعد از ساخت یک IP با Block Memory Generator انجام میدهیم، باید یک نمونه از آن را در کدهای RTL فراخوانی کنیم. برای اینکار باید به صورت زیر عمل کنید:

در گام اول: کتابخانه XPM و پکیج vcomponents را به کدهای RTL اضافه کنید. یعنی دو خط کد زیر را به بالای کدهای VHDL اضافه کنید.

library xpm; use xpm.vcomponents.all

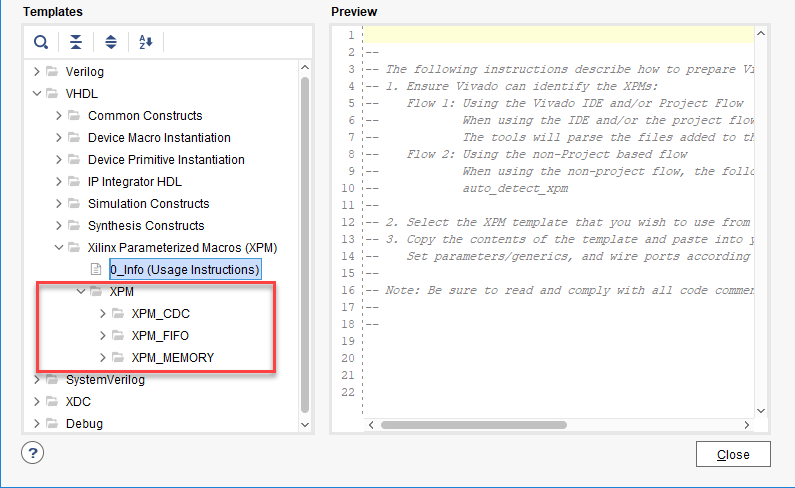

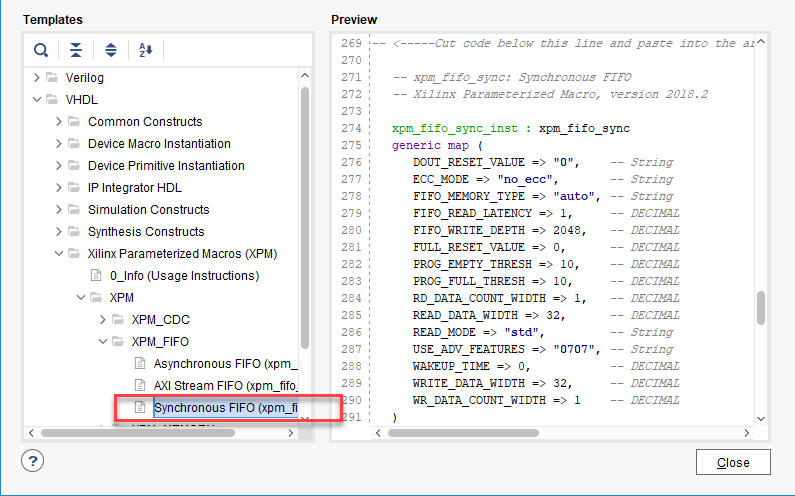

در گام دوم: با استفاده از پنجره Language Template در صفحه Flow Navigator در محیط توسعه Vivado از بین الگویهای آماده موجود، ساختار مورد نظر را انتخاب و به کدهای RTL اضافه کنید.

در پنجره Language Template نمونه کدهای آماده فراوانی وجود دارد که با کپی پیست کردن به سادگی میتوانید آنها را به طرحتان اضافه کنید. برای دسترسی به XPM ها باید به آدرس زیر بروید. همینطور این امکان برای شما وجود دارد تا در صورتی که از ویرایشگر Vivado استفاده نمیکنید این الگوها را برای نسخه 2018.1 از اینجا دانلود کنید و در کد RTL خود استفاده کنید.

// XPM Address in Language Template <Language>/Xilinx Parametrized Macro(XPM)/XPM

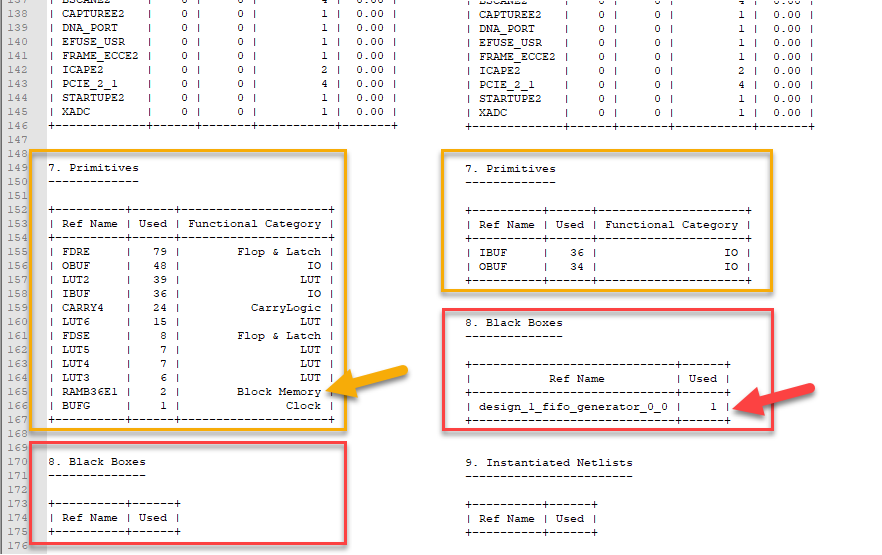

همانطور که پیش تر وعده دادیم حالا بد نیست برای درک بهتر تفاوتی که در گزارش خروجی ابزار سنتر هنگام استفاده از XPM ها رخ میدهد، یک مثال ساده را باهم مرور کنیم. مثال انتخابی ما یک طرح ساده است که در آن یک FIFO سنکرون با دو شیوه مختلف فراخوانی و پیاده سازی شده است.

در روش اول FIFO مورد نظر را با استفاده از FIFO generator ایجاد و مورد استفاده قرار دادهایم. با سنتز طرح و بررسی گزارش سنتز مشاهده خواهید کرد که FIFO به صورت black box گزارش میشود و لیستی که در آن primitive های مورد استفاده گزارش میشوند، هیچ حافظه block RAM گزارش نشده است.

در روش دوم همان FIFO این بار با استفاده از XPM ها فراخوانی شده است. با بررسی مجدد گزارش سنتز به وضوح تفاوت در گزارش Primitive ها قابل مشاهده است، بعلاوه اینکه دیگر از black box خبری نیست و بخش مربوط به آن در گزارش سنتز خالی است. این مسأله در شکلهای زیر، قابل مشاهده است.

در شکل زیر تصویر گزارش سنتز هر دو طرح نظیر به نظیر در کنار هم نشان داده شده است. چند لحظه روی این دو گزارش تأمل کنید تا تفاوت آنها درک کنید.

شما میتوانید به شکل مشابهی سایر ماکروهای Xilinx را تست و اثر آنها را هنگام شبیه سازی و سنتز بررسی کنید.

جمع بندی

به طور کلی استفاده از XPM ها به جای IP Core ها از نقطه نظر سرعت و کارایی نتایج بهتری را به همراه دارد. کاهش زمان شبیه سازی یکی از مزایای مهم آنها به شمار میرود. فراخوانی XPM ها در طرح کار نسبتاً آسانی است، از این رو بد نیست پیش از جمع بندی روی شیوه پیاده سازی بخشهای مختلف طرح به اینکه آیا امکان استفاده از XPM ها را دارید یا خیر به دقت فکر کنیم، چون بدون شک در انتهای کار پشیمان نخواهید شد.

منبع: با اقتباس از microzedchronicles.com و UG953 و UG974

7 در مورد “فراخوانی حافظهها و عناصر سنکرون ساز کلاک با استفاده از XPM”

خواهش می کنم، زحمتی که شما برای جمع آوری این آموزش ها به خرج می دین، بسیار بیشتر شایسته تقدیر و تشکره. ممنونم از شما

و البته black box که به اشتباه block box تایپ شده

حسن عزیز درود بر شما

از دقت نظری که در مطالعه این مطلب به خرج دادید، سپاسگزارم. اشتباهی که در متن وجود داشت، اصلاح شد.

البته هنوز چندتایی block box وجود داره که اونها هم باید اصلاح بشه

سلام بر شما، ممکنه مشکل نمایش یا حافظه کش مرور گر داشته باشید. کلیه موارد اصلاح شده است. ولی مجدد بررسی خواهم کرد.

سلام و تشکر بابت سایت فوق العاده و آموزش های خوبی که قرار می دین.

فکر می کنم در بخش فراخوانی XPM منظور شما inference بوده و نه interface چون توضیحاتی که دادین به Infer کردن می خوره.

حسن عزیز سلام، بدون شک دقت شما در مطالعه متن و احتمالاً مراجعه به مرجع اصلی این مقاله شایسته تقدیر و تشکر است. از طرف خودم و سایر اعضای تیم از شما سپاسگزاریم. امیدوارم در تمامی مقاطع کار و زندگی موفق و پیروز باشید.

واژه صحیح در متن فوق Inference به معنای استنتاج است، که این مورد در متن اصلاح شد.