مقدمه

آنالیز زمانبندی ایستا پیش از هر چیزی نیازمند این است که ما با ابزارهای این کار و مفاهیم اولیه آن آشنا باشیم. در سایه آشنایی با تعاریف میتوانیم بهترین روش ممکن برای دستیابی به کارایی مطلوب را انتخاب و به موثرترین شکل به کار بگیریم. در این آموزش از پایگاه دانش هزالینکس قصد داریم شما را با مفهوم retiming و شیوه استفاده از تکنیک retiming در ابزار سنتز Vivado آشنا کنیم. اگر علاقمند به موضوعات مرتبط با بهینه سازی زمانبندی در طراحیهای FPGA هستید، تا انتها با ما همراه باشید.

تعریف retiming

در ابتدا اجازه بدهید یک تعریف از retiming ارائه بدهیم. شاید در آغاز این تعریف کمی گنگ و نامفهوم به نظر برسد، اما با توضیحاتی که در ادامه مطالعه خواهید کرد، ابهامات اولیه به کلی برطرف میشود.

اصلاح زمانبندی مسیرها در FPGA، یا retiming یک تکنیک بهینه سازی ترتیبی برای جابجایی رجیسترها در طول منابع منطقی است. این کار با هدف بهبود کارایی طرح بدون بروز تداخل روی رفتار ورودی و خروجیهای مدارات منطقی انجام میشود.

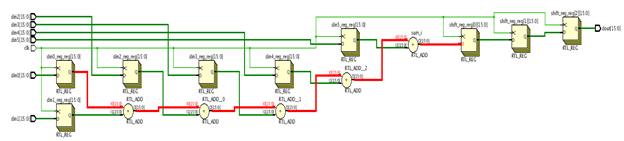

مدار نشان داده شده در شکل (۱) دارای مسیر بحرانی با یک جمع کننده شش ورودی است. این مسیر با رنگ قرمز متمایز شده است. این دقیقاً همان مسیری است که کارایی مدار را تحت تاثیر قرار میدهد.

تعریف مسیرهای زمانبندی ایستا (Static Timing Paths)

مسیر زمانبندی ایستا، مسیری است که

- از یک عنصر کلاک دار شروع می شود.

- در طول تعدادی عنصر ترکیبی و نتهای متصل کننده آنها منتشر می شود و

- به یک عنصر کلاک دار ختم میشود.

عناصر کلاک دار شامل فلیپ فلاپ ها، بلوکهای ضرب کننده، حافظهها و … هستند و عناصر ترکیبی شامل LUT ها، مالتی پلکسرها و … هستند.

در عمل آنالیز زمانبندی ایستا تنها برای بخشهایی از مدار که بین دو عنصر سنکرون قرار دارند صورت میپذیرد و مسیرهای فاقد عنصر سنکرون نادیده گرفته میشوند، به بیان سادهتر آنالیز زمانبندی برای مدارات ترکیبی کاملا بی معنی است.

مشخصههای زمانبندی و به طور کلی کارایی مداری که در این شکل نشان داده شده است میتواند با اعمال تکنیک retiming روی رجیسترهای خروجی جمع کننده بهبود پیدا کند. برای این کار لازم است رجیسترها به نقطهای از مدار که عناصر ترکیبی بیشتری در آنجا هستند، منتقل شوند.

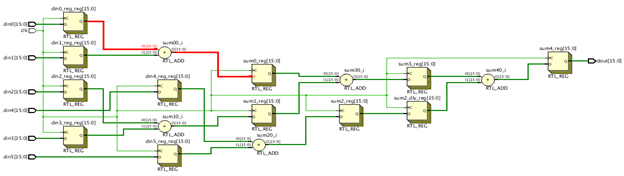

تأخیر مجموع ما در این مدار برابر با ۴ است. شکل (۲) یکی از روشهای موجود برای انتقال رجیسترها با هدف کاهش توالی منابع منطقی را نشان میدهد. جابجا کردن رجیستر خروجی به ابتدای مدارت ترکیبی اصطلاحاً backward retiming نامیده میشود. با این کار، مسیر بحرانی محدود به یک جمع کننده دو ورودی میشود.

نکته دیگری که باید در مثالهای بالا به آن توجه کنیم، تغییر در تعداد رجیسترهاست.

شکل (۱) دارای ۹ رجیستر روی هر باس (سیگنالهای ۱۶ بیتی) است. در حالی که شکل (۲) دارای ۱۲ رجیستر باس متفاوت است. واضح است که این اختلاف ناشی از بکارگیری تکنیک backward retiming است. با جابجایی رجیستر از خروجی به سمت ورودی هر دو ورودی گیت باید دارای رجیستر باشند.

به طور کلی دو نوع retiming وجود دارد:

- جابجایی فلیپ فلاپها به صورت رو به عقب یا backward retiming و

- جابجایی فلیپ فلاپها به صورت رو به جلو یا forward retiming .

در backward retiming رجیسترهای خروجیگیتها حذف میشود و رجیسترهای جدید در ورودی آنها قرار داده میشود. در forward retiming دقیقاً به صورت معکوس عمل میکند و رجیسترهای را از ورودی گیتها حذف و در خروجی گیتها قرار میدهد.

برای اینکه تکنیک backward retiming با موفقیت همراه شود، مدار ترکیبی باید تنها یک رجیستر را درایو کند و fanout اضافی روی سایر بخشهای منطقی نداشته باشیم. برای اینکه forward retiming کار کند هر ورودی گیت باید با رجیسترهایی که دارای کنترل ستهای مشابه هستند درایو شود.

تعریف fanout در مدرات دیجیتال و FPGA

در الکترونیک دیجیتال، مفهوم fanout به عنوان پارامتری برای توصیف ظرفیت خروجی گیتهای منطقی بکار برده میشود و بیانگر تعداد ورودیهایی است که یک خروجی میتواند برای گیتهای دیگر تامین کند. به بیان سادهتر در FPGA تعداد مسیرهای منشعب شده از یک سیگنال یا پورت خروجی fanout نامیده میشود. هر پورت ورودی در گیتهای منطقی نمیتواند با بیش از یک پورت خروجی تغذیه شود، اما در نقطه مقابل هر خروجی ممکن است برای تامین ورودی بخشهای مختلف سیستم مورد استفاده قرار بگیرد. هر چه fanout یک سیگنال خروجی کمتر باشد، میزان پایداری و قابلیت اطمینان از عملکرد آن سیگنال و در نتیجه کل سیستم بالاتر میرود. در واقع fanout معیاری برای سنجش تعداد کپیهای ساخته شده از یک سیگنال واحد درون طراحی دیجیتال است.

تنظیمات سرتاسری در مقایسه با تنظیمات محلی

برای فعال سازی و اعمال اتوماتیک تکنیک retiming در ابزار سنتز Vivado دو روش وجود دارد.

- روش محلی (local retiming)

- و روش سرتاسری (global retiming)

در روش سرتاسری فرایند اصلاح زمانبندی روی تمام طرح اعمال میشود و رجیسترها روی بخشهای مختلف ترکیبی مدار جابجا میشوند. نحوه اعمال این جابجاییها کاملاً وابسته به ملاحظات زمانبندی طرح است.

در واقع بعد از فعال سازی تنظیمات سرتاسری retiming کل طرح آنالیز میشود و رجیسترها به سمت بدترین مسیرها از نقطه نظر زمانبندی منتقل میشوند. با این الگو بهینه سازی سرتاسری روی طرح اعمال میشود و طرح ما در مجموع سریعتر میشود. برای انجام این کار لازم است قیود زمانبندی مناسب و البته دقیق (timing constraints) برای طرح تعریف و در فایل xdc گنجانده شوند. تنظیمات سرتاسری با فراخوانی سوئیچ -retiming در synth_design (فرمان tcl برای سنتز طرح) و یا انتخاب گزینه retiming در برگه تنظیمات ابزار سنتز Vivado فعال میشود. علاوه بر این با استفاده از ویژگی BLOCK_SYNTH در زمان سنتز، این امکان برای ما وجود دارد که تنها یک ماژول خاص را برای retiming مشخص کنیم.

در نقطه مقابل در روش محلی، کاربر با استفاده از attribute ها درون کد HDL صراحتاً به ابزار میگوید عملیات retiming را دقیقاً روی کدام بخش از مدار و به چه صورت ( backward retiming و یا forward retiming ) انجام شود.

لازم است به این نکته توجه داشته باشید که در زمان اجرای retiming ابزار دقیقاً همان کاری را کاربر تعیین کرده است، انجام میدهد و کلیه ملاحظات زمانبندی اتوماتیک کنار گذاشته میشوند. یعنی تمامی مسئولیت کارایی مدار بعد از local retiming بر عهده مهندس طراح است.

برای اطلاعات بیشتر در این زمینه میتوانید به UG901 مراجعه کنید

آنالیز گزارش خروجی (Log file)

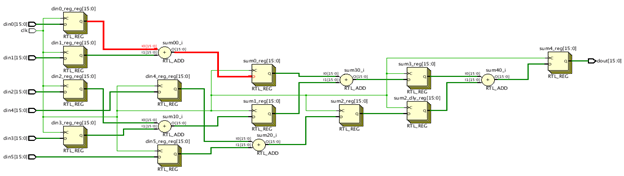

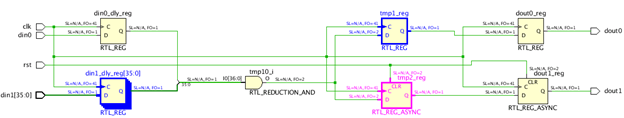

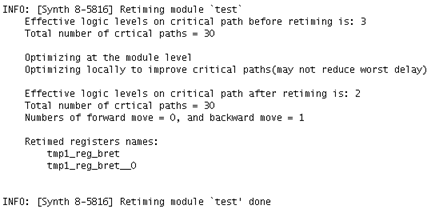

شکل (۴) مثالی را نشان میدهد که در آن تکنیک retiming باعث بهبود تعداد سطوح منطقی میشود. ساختار ما دارای مسیر بحرانی با سه سطح منطقی است که از گیت and با ۳۷ بیت تامین می شود. رجیستر مبدأ din1_dly_reg نام دارد و رجیستر مقصد tmp1_reg نام گذاری شده است. یک رجیستر اضافی دیگر بلافاصله بعد از رجیستر tmp1_reg وجود دارد و هیچ سطح منطقی بین این دو رجیستر وجود ندارد.

در واقع ما با یک مسیر ایده آل روبرو هستیم و میتوانیم به خوبی مشخصههای زمانبندی آن را اصلاح کنیم. در اینجا ما دو مسیر پشت سرهم داریم که مسیر اول آن دارای سه سطح گیت منطقی است و مسیر دوم آن فاقد سطوح منطقی یا گیتی است. ما میتوانیم سطوح منطقی مسیر اول را از ۳ به ۲ سطح کاهش و سطح منطقی باقی مانده را به مسیر دوم منتقل کنیم.

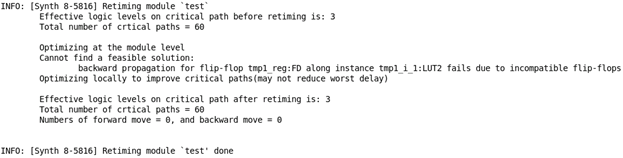

فایل گزارش خروجی سنتز، اطلاعاتی مشابه شکل زیر را در کنسول خروجی نمایش میدهد:

با مطالعه این گزارش شما میتوانید تعداد سطوح منطقی در هر بخش از طرح خود را قبل و بعد از اعمال تکنیک retiming بررسی نمایید. در این گزارش نام رجیستر جدیدی که ساختهایم نیز مشاهده میشود. زمانی که ابزار سنتز یک رجیستر جدید با هدف اصلاح زمانبندی تولید میکند از پیشوندهای “bret” و “fret” به ترتیب برای مشخص کردن رجیستر تولیدی جدید در backward retiming و forward retiming استفاده میکند.

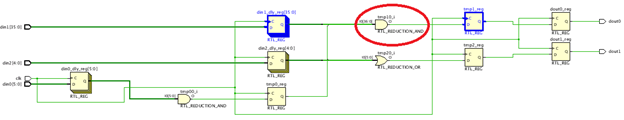

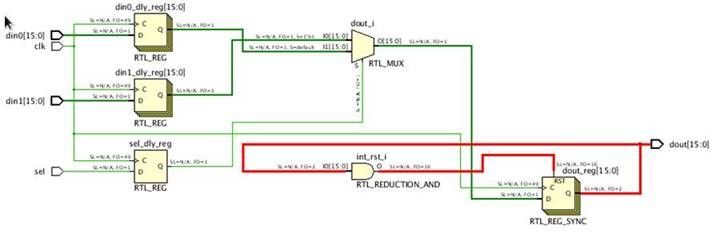

شکل (۶) مداری را نشان میدهد که وجود یک رجیستر ناسازگار از اعمال retiming جلوگیری میکند. در این ساختار نیز همچون ساختار قبلی رجیستر مبدأ din1_dly_reg نام دارد، در ادامه مسیر یک گیت and با ۳۷ بیت وجود دارد که باعث ایجاد سه سطح منطقی میشود. در نهایت مسیر به رجیستری به نام tmp1_reg منتهی میشود. علاوه بر این گیت AND دارای fanout اضافی به یک رجیستر دیگر است که با رنگ صورتی متمایز شده است.

در این مثال به دلیل وجود رجیستر اضافی در خروجی گیت and اعمال retiming امکان پذیر نیست. این رجیستر دارای ریست آسنکرون است در حالی که رجیستر tmp1_reg چنین شرایطی ندارد. از آنجایی که دو تا رجیستر خروجی دارای کنترل ست های مشابه نیستند، امکان اعمال تکنیک backward retiming روی گیت AND وجود ندارد. گزارشی خروجی سنتز اطلاعاتی مشابه با تصویر نشان داده شده در شکل (۷) را نشان میدهد

فایل گزارش خروجی سنتز شامل پیغامی درباره عدم سازگاری فلیپ فلاپها هست. در این گزارش تعداد سطوح منطقی قبل و بعد از retiming تغییر نمیکند.

به طور کلی عملیات retiming در موارد زیر امکانپذیر نیست:

- زمانی که از قید Timing Exceptions روی رجیسترها استفاده شده باشد (قیدهایی همچون multicycle paths, false paths, max delay )

- زمانی که ویژگی Keep روی رجیستر فعال شده باشد. (در زمان استفاده از قیدهایی همچون DONT_TOUCH, MARK_DEBUG)

- رجیسترهایی که دارای کنترل ست متفاوت باشند

- رجیسترهایی که مستقیماً به خروجیها و یا ورودیهای ماژول متصل شده اند. مگر اینکه طرح به صورت OOC – out of context علامت گذاری و سنتز شود.

مثالی از یک حلقه فیدبک

در ادامه یک مثال از مداری که در آن retiming قادر به بهبود مسیر بحرانی در یک حلقه فیدبک نیست را با هم مرور میکنیم. وقتی که یک مسیر دارای یک رجیستر مبدأ و مقصد یکسان است، بهینه سازی با تکنیک retiming قادر به ایجاد بهبود در سطوح منطقی نیست.

برای مثال مدار شکل (۸) را در نظر بگیرید:

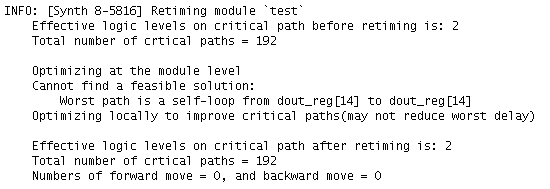

مسیر بحرانی رجیستر “dout_reg” با رنگ قرمز متمایز شده است. خروجی رجیستر بعد از عبور از گیت AND در ادامه به پین ریست رجیستر مبدأ منتهی میشود.

گیت RTL_REDUCTION_AND با توجه به عرض بیت ما یعنی ۱۶ بیت، دارای دو سطح منطقی است.

تصویری که در شکل (۹) ملاحظه میکنید. بخشی از گزارش سنتر است که در آن ابزار سنتز Vivado ماهیت این مسیر بحرانی را توصیف کرده است. در این گزارش، نام سلولهایی که بخشی از مسیر بحرانی هستند نیز ذکر شده است.

جمع بندی

به طور کلی در تعیین عمکرد و کارایی یک طرح عناصر سازنده طرح تاثیرگذار نیستند !!! بلکه شیوه کنار هم قرار دادن آنها تعیین کننده است. در این آموزش ما شما را با یکی از تکنیکهای بهینه سازی زمانبندی در FPGA آشنا کردیم. بدیهی است در طرحهای پیچیده استفاده از تکنیک retiming به تنهایی کافی نیست و شما باید برای دستیابی به نتایج مطلوب تسلط لازم به کلیه مفاهیم آنالیز زمانبندی ایستا داشته باشید.

منبع: برگرفته از وبلاگ Xilinx