مقدمه

اهمیت و عملکرد کلاک در یک سیستم دیجیتال را میتوان مشابه نقش خون در بدن موجودات زنده در نظر گرفت. برای سالم و توامند بودن نیاز داریم دستگاه گردش خون در بدن کاملا سالم باشد. هر چند این شرط کافی نیست، اما شرط لازم است. خون در بخشهای مختلف بدن جریان پیدا میکند و متابولسیم بدن را تنظیم میکند. مشابهاً کلاک هم در بخشهای مختلف یک سیستم دیجیتال سنکرون جریان پیدا میکند و رویدادهای دیجیتال درون سیستم را کنترل میکند. عملکرد کلاک درون تراشه FPGA و کلیه تراشههای SoC نیز دقیقا به همین صورت است. در این آموزش از پایگاه دانش هگزالینکس قصد داریم شما را با مفاهیم تأخیر، جیتر، کجی و عدم قطعیت کلاک در مدارات کلاک به ویژه FPGA آشنا کنیم. این مفاهیم را با هم مقایسه میکنیم و اهمیت هر کدام را بیان میکنیم.

طراحی کلاک

دو فاز در طراحی سیگنال کلاک برای هر سیستم دیجیتالی وجود دارد.

در فاز اول فرض میشود کلاک در حالت ایده آل خودش قرار دارد. در طول طراحی سطح رجیستر، سنتز و جانمایی عناصر روی تراشه، کلاک کما بیش چنین شرایطی دارد. ایده آل فرض کردن کلاک به این معناست که هیچ مکانیزم یا توپولوژی فیزیکی برای توزیع کلاک در سطح تراشه وجود ندارد و هر جا که به کلاک نیز داریم به شکل معجزه واری این کلاک روی پین ورودی کلاک عناصر سنکرون ظاهر میشود.

فاز دوم بعد از ساخت توپولوژی توزیع کلاک آغاز میشود. در این فاز مسیرهای کلاک مشابه درختی در سرتاسر تراشه پخش میشوند. بافرهای مناسب در بخشهای مختلف این مسیر قرار میگیرند و هدایت سیگنال کلاک را از یک نقطه آغاز به یک نقطه پایان برعهده میگیرند. نقطه آغازین معمولا منبع تولید کننده کلاک و نقاط پایانی هزاران و بلکه میلیونها فلیپ فلاپی هستند که در سرتاسر تراشه قرار دارند و برای عملکرد مناسب به این کلاک نیاز دارند. در عمل ساخته شدن مسیرهای کلاک و شکل دهی یک درخت کلاک (clock tree) بعد از فرایند مسیریابی (routing) انجام میشود. بعد از پایان پروسه مسیریابی وضعیت کلاک از حالت ایده آل به حالت کلاک انتشار یافته در سطح تراشه تغییر میکند.

تأخیر کلاک چیست؟

اجازه بدهید در ابتدا کمی درباره مفهوم دو عبارت clock latency و insertion delay باهم صحبت بکنیم. واژه تأخیر کلاک یا همان clock latency، مفهومی است که در ادبیات کلاک ایده آل مورد استفاده قرار میگیرد. این تأخیر به مدت زمان مورد نیاز برای حرکت سیگنال کلاک از پین خروجی منبع تولید کننده آن (مثلا اسیلاتور) به سمت مقصد آن در پین ورودی یک فلیپ فلاپ اطلاق میشود. این تأخیر توسط طراح تعریف میشود و در واقعیت وجود ندارد. این تأخیر تا قبل از ساخته شدن درخت کلاک قابل اندازه گیری نیست.

بعد از شکلگیری درخت کلاک، تأخیر کلاک قابل اندازه گیری میشود. از اینجا به بعد این تأخیر، تحت عنوان تأخیر اضافه شده یا همان insertion delay شناخته میشود. (امیدوارم از نحوه ترجمه عبارت insertion delay نا امید نشده باشید !!). این دو واژه در بسیاری از موارد به جای هم به کار برده میشوند ولی افراد هوشمندتر از واژه clock latency برای اشاره به مقدار تئوری و مطلوب insertion delay استفاده میکنند.

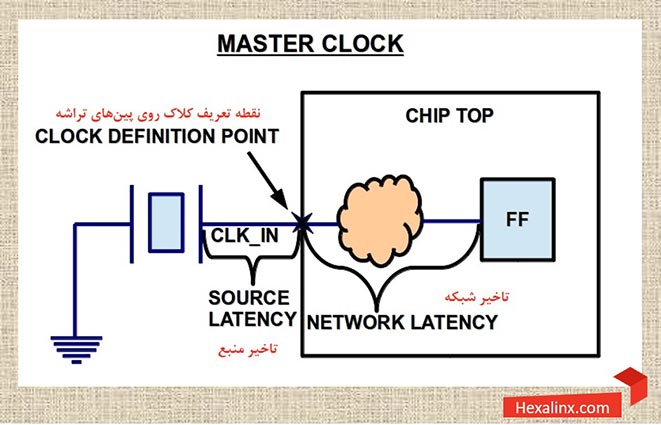

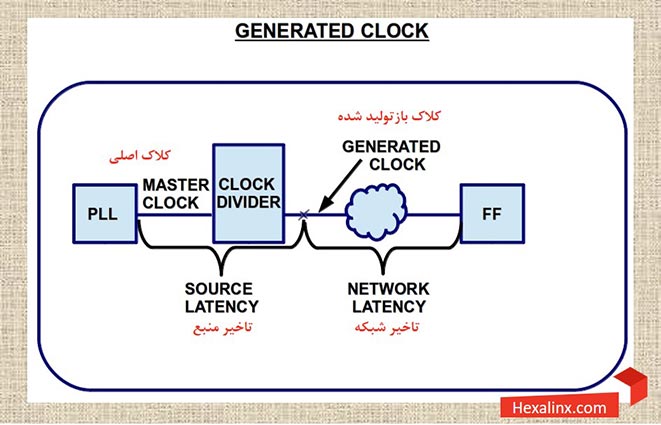

به هرحال ما در ادامه از واژه تأخیر کلاک برای مخاطب قرار دادن هر دو مفهومی که توضیح داده شد استفاده میکنیم (هم در حالت ایدآل و هم در حالت واقعی). تأخیر کلاک در حالت واقعی از دو بخش تشکیل شده است. بخش اول تأخیر ناشی از منبع کلاک است و بخش دوم تأخیر ناشی از شبکه کلاک است.

تأخیر منبع کلاک به تأخیر بین نقطه منبع تولید کلاک و نقطه تعریف آن گفته میشود. تأخیر شبکه کلاک تأخیر بین نقطه تعریف کلاک تا نقطه مقصد کلاک است. برای روشن شدن موضوع به شکلهای (۱) و (۲) دقت کنید.

کجی یا چولگی کلاک چیست؟

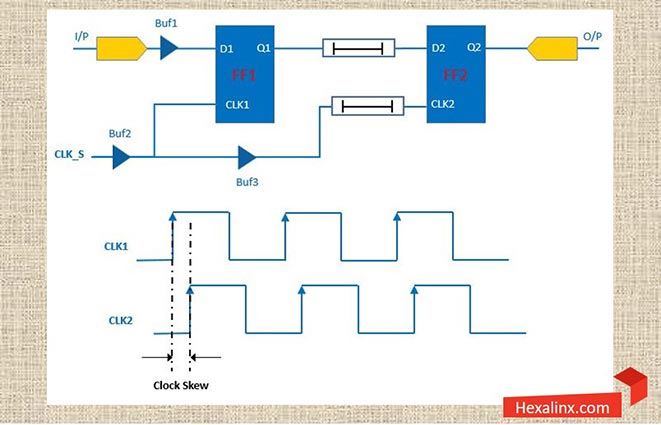

فرض کنید کلاک از یک منبع مشخص تولید میشود و در بخشهای مختلف سیستم توزیع میشود. اگر از بین تمامی این مقصدها دو مقصد را در نظر بگیریم و تأخیر موجود در مسیر کلاک برای هر کدام از این دو مقصد را محاسبه کنیم و سپس دو عدد بدست آمده را با هم مقایسه کنیم. اختلاف زمانی محاسبه شده اصطلاحاً کجی کلاک یا همان clock skew نامیده میشود. به بیان دقیقتر کجی کلاک معیاری است که برای بیان اختلاف زمانی در مسیر حرکت کلاک از یک منبع مشترک به سمت دو مقصد متفاوت. در مدارات سنکرون کجی کلاک روی یک مسیر مشخص بین دو فلیپ فلاپ محاسبه میشود.

اگر تأخیر زمانی رسیدن کلاک از منبع مشترک به فلیپ فلاپ قرار گرفته در ابتدای مسیر کمتر از تأخیر زمانی کلاک از منبع مشترک به فلیپ فلاپ انتهای مسیر باشد. آنگاه کجی کلاک مقداری مثبت دارد. شکل گیری چنین شرایطی برای بررسی setup مطلوب است. اگر شرایط برعکس باشد کجی کلاک مقداری منفی خواهد داشت و شرایط برای بررسی hold مطلوب است. مقدار ایده آل برای کجی کلاک (شرایطی که همه راضی باشند !!) مقدار صفر است؛ که البته در عمل دست نیافتنی است. هدف اصلی از طراحی یک توپولوژی یا درخت کلاک مناسب، کاهش مقدار کجی کلاک است.

جیتر کلاک چیست؟

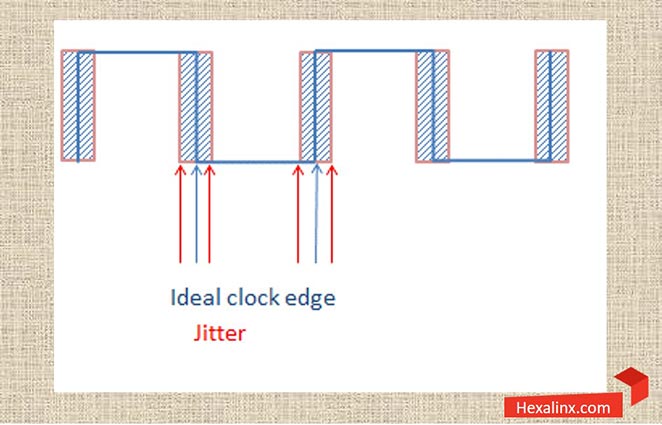

پریود کلاک منبع تولید کننده کلاک هیچ گاه دقیق و ثابت نیست و عددی که تحت عنوان پریود ارائه می شود در واقع مقدار متوسط پریود کلاک است. در حالت کلی پریود کلاک ممکن است در یک الگوی کاملا تصادفی کمی کوتاه تر و یا کمی بلندتر شود. این رخداد جیتر کلاک (clock jitter) نام دارد. دلیل اصلی بروز جیتر کلاک به ماهیت منبع تولید کننده آن بر میگردد. اسیلاتورهای کلاک و PLL ها همواره یک مقدار محدودی جیتر در خروجی شان تولید میکنند. نویز ناشی از سایر مدارات در یک سیستم و همینطور شرایط محیطی هم ممکن است در جیتر کلاک تأثیر داشته باشد.

عدم قطعیت کلاک چیست؟

عدم قطعیت کلاک مفهومی است که برای بیان میزان انحراف لبه کلاک در حالت واقعی از مقدار تئوریک آن بکار برده میشود. در حالت ایده آل لبههای بالا و پایین رونده کلاک روی پین ورودی تمامی فلیپ فلاپها در یک لحظه بدون هیچ انحرافی دریافت میشوند. اما در واقعیت این غیر ممکن است. موقعیت لبههای کلاک در تمامی لحظات ثابت نیست و ممکن کمی به عقب یا جلو متمایل باشد.

به عنوان مثال کلاکی را در نظر بگیرد که در مشخصات توصیفی آن پریود 1ns با عدم قطعیت 100psدرج شده است. در عمل فاصله هر لبه کلاک تا لبه کلاک بعدی 1ns±50ps است.

خب حالا سؤال اینجاست که تفاوت آن با جیتر یا کجی کلاک چیست. به نظر شما تعریفی که ارائه شد تقریباً بیان دیگری از همان مفاهیم قبلی نیست؟ ممکن است سؤال دیگری نیز مطرح شود که اصلا چرا زمان رسیدن لبه کلاک به پین ورودی فلیپ فلاپ دقیقاً به اندازه یک پریود نیست؟ اجازه بدهید تا ابتدا به سؤال دوم را پاسخ بدهیم چون در عمل پاسخ سؤال اول نیز در آن نهفته است.

عوامل تأثیرگذار در عدم قطعیت کلاک

ممکن است چندین دلیل منجربه ایجاد عدم قطعیت در کلاک بشود.

- اولین عامل تأثیرگذار، کجی کلاک است. در بخش قبل مفهوم کجی کلاک را توضیح دادیم.

- دومین عامل به ماهیت منبع تولید کننده کلاک بر میگردد. این عامل را هم کمی قبلتر تحت عنوان جیتر کلاک معرفی کردیم. قبل از ساخته شدن توپولوژی کلاک عدم قطعیت برابر با حاصل جمع جیتر کلاک و کجی کلاک است و بعد از ساخته شدن توپولوژی کلاک عدم قطعیت کلاک دقیقاً همان جیتر کلاک است.

- عامل سوم مربوط به شرایط محیطی است. زیرا مسیرهای نسبتا ایده آل و پایدار تراشه تحت تاثیری عواملی همچون نویز یا تغییرات دمایی دستخوش تغییر میشوند که این تغییرات در نهایت منجر به تشدید پدیده کجی کلاک میشود.

جمع بندی

تا پیش از این عادت داشتیم تا کلاک را با دو پارامتر فرکانس و پریود توصیف کنیم. در حالی که این دو پارامتر مشخصههای کلاسیک کلاک هستند و هیچ اطلاعاتی در مورد میزان دقت کلاک و پایداری آن در مدار ارائه نمیدهند، پارامترهایی نظیر تأخیر، جیتر، کجی و عدم قطعیت کلاک تاثیر بالایی روی عملکرد یک سیستم سنکرون دارند و در تحلیل زمان بندی ایستا بکار گرفته میشوند. در عمل جیتر به عنوان ورودی برای ابزارهای پیاده سازی تعریف میشود و میزان کجی کلاک هم به صورت اتوماتیک با استفاده از مسیرهای توزیع کلاک درون تراشه FPGA محاسبه میشود.

منبع: با اقتباس از columbia.edu

4 دیدگاه برای “تأخیر، جیتر، کجی و عدم قطعیت کلاک”

عالی و شیوا

درود فراوان

همراهی و لطف شما باغث افتخار ماست.

با سلام . با تشکر از زحمات شما بابت تهیه و تدوین محتوای دقیق و کامل هگزالینکس.

منظور از “بررسی setup” و “بررسی hold” در این مقاله چیست ؟

با سلام و درود فراوان بر شما دوست عزیز

همراهی و پیامهای ارزشمند شما باعث دلگرمی تیم هگزالینکس است.

پاسخ به سؤالی که مطرح کردید چندان کوتاه نیست و نیاز به آشنایی شما به مفاهیم زمانبندی ایستا در FPGA دارد.

دو مفهوم setup و hold برای بررسی پایداری و ثابت بودن مقدار یک باس داده در لبههای کلاک استفاده میشود و به نوعی حداقل و حداکثر زمان مجاز تأخیر در هنگام ارسال یک سیگنال از یک عنصر سنکرون به عنصر سنکرون بعدی را تعیین میکند. این دو مفهوم به صورت زیر تعریف میشوند.

بررسی setup time یعنی حصول اطمینان از اینکه تغییر وضعیت در یک عنصر کلاک دار زمان کافی برای انتشار به سمت عنصر کلاک دار دیگر قبل از لبه بعدی کلاک را دارد یا نه؟ به طور کلی setup برای طولانی ترین مسیر بررسی میشود.

بررسی hold time یعنی حصول اطمینان از اینکه تغییر وضعیت یک عنصر کلاک دار همزمان با لبه کلاک قبل از رسیدن همان لبه کلاک به عنصر مقصد، در عنصر کلاک دار مقصد منتشر نمیشود. به طور کلی hold برای کوتاه ترین مسیر بررسی میشود.